PLL详解

- 格式:doc

- 大小:14.03 KB

- 文档页数:5

市场常用PLL指标1. 什么是PLL指标?PLL是Phase-Locked Loop(锁相环)的缩写,是一种常用的电子系统控制技术。

在市场领域,PLL指标通常是指一系列用于分析和预测市场走势的技术指标。

这些指标基于市场数据的统计分析,旨在帮助投资者判断市场的趋势和可能的转折点。

2. 常用的PLL指标在市场中,有许多常用的PLL指标被广泛应用于交易决策,下面列举了一些常见的PLL指标:2.1 移动平均线(MA)移动平均线是最基本、最常用的PLL指标之一。

它通过计算一段时间内的价格平均值,以平滑价格曲线,从而消除价格波动的噪音,更好地观察价格走势。

常见的移动平均线有简单移动平均线(SMA)和指数加权移动平均线(EMA)。

SMA是一种最简单的移动平均线方法,它将每个时期的价格相加,再除以时期的个数,得到平均价格。

EMA是一种更加常用的移动平均线方法。

它采用指数加权的方式计算平均价格,较新的价格权重较高,能更及时地反映市场变化。

2.2 相对强弱指标(RSI)相对强弱指标是一种衡量市场买卖力量的指标,也是常用的PLL指标之一。

它通过将一段时间内的平均涨幅与平均跌幅进行比较,来衡量市场的超买和超卖情况。

RSI指标的取值范围为0到100之间,通常大于70表示超买,小于30表示超卖。

2.3 随机指标(KD)随机指标是一种衡量市场超买超卖情况的指标,常用于短期交易。

它通过比较当前价格与一段时间内的最高价和最低价的关系,来判断市场的买卖力量。

随机指标的取值范围为0到100之间,通常大于80表示超买,小于20表示超卖。

2.4 平均真实波动范围(ATR)平均真实波动范围是一种衡量市场波动性的指标,也是常用的PLL指标之一。

它通过计算最高价和最低价之间的波动幅度,来判断市场的行情强度和风险水平。

ATR指标的数值越大,表示市场波动性越高。

2.5 震荡指标(MACD)震荡指标是一种衡量市场趋势强度和转折点的指标,常用于中长期交易。

PLL锁相环相关基础知识由于近期找工作,所以把射频的一些基础知识复习了一遍。

趁着自己还有点时间和精力,把锁相环的一些知识记录一下,基础功不扎实,有误之处还请大佬拍错。

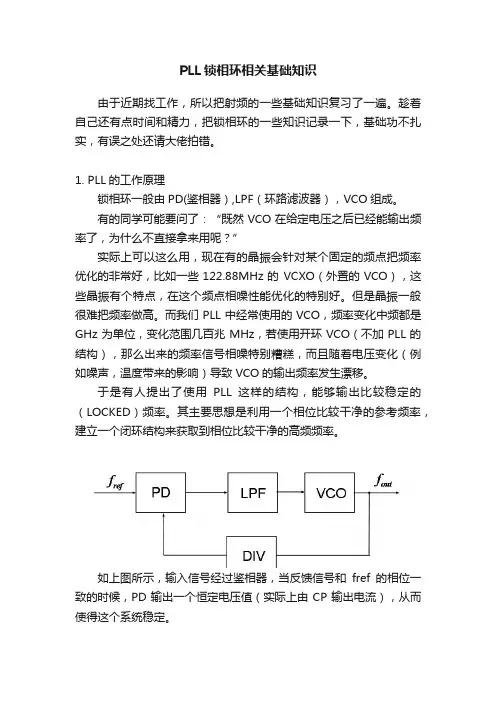

1. PLL的工作原理锁相环一般由PD(鉴相器),LPF(环路滤波器),VCO组成。

有的同学可能要问了:“既然VCO在给定电压之后已经能输出频率了,为什么不直接拿来用呢?”实际上可以这么用,现在有的晶振会针对某个固定的频点把频率优化的非常好,比如一些122.88MHz的VCXO(外置的VCO),这些晶振有个特点,在这个频点相噪性能优化的特别好。

但是晶振一般很难把频率做高。

而我们PLL中经常使用的VCO,频率变化中频都是GHz为单位,变化范围几百兆MHz,若使用开环VCO(不加PLL的结构),那么出来的频率信号相噪特别糟糕,而且随着电压变化(例如噪声,温度带来的影响)导致VCO的输出频率发生漂移。

于是有人提出了使用PLL这样的结构,能够输出比较稳定的(LOCKED)频率。

其主要思想是利用一个相位比较干净的参考频率,建立一个闭环结构来获取到相位比较干净的高频频率。

如上图所示,输入信号经过鉴相器,当反馈信号和fref的相位一致的时候,PD输出一个恒定电压值(实际上由CP输出电流),从而使得这个系统稳定。

如果我们把PD简单看做一个乘法器,那么有参考输入信号反馈输入的角频率为:N一般表示为反馈DIV的分频比。

反馈输入信号为:两者相乘根据积化和差可以得到高频和低频两个分量。

其中高频的部分会被LPF滤掉。

所以只剩低频部分。

对于低频部分,将相位记为:要使得系统稳定,即相位恒定,可以关于相位对时间t求导数,当等于0时可以认为两个相位一致。

一般把看做两个时钟的随机起振相位,上电后保持不变。

所以有当导数为0的时候:此时有假如此时参考频率10MHz,N为350,可以得到3.5GHz的频率输出。

当然前提是PLL的VCO支持这个频段。

当然对于现在的芯片,鉴频器的参考频率输入前也有一个分频器或者倍频器,一般记为R。

pll锁相环工作原理

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。

PLL用于振荡器中的反馈技术。

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。

一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

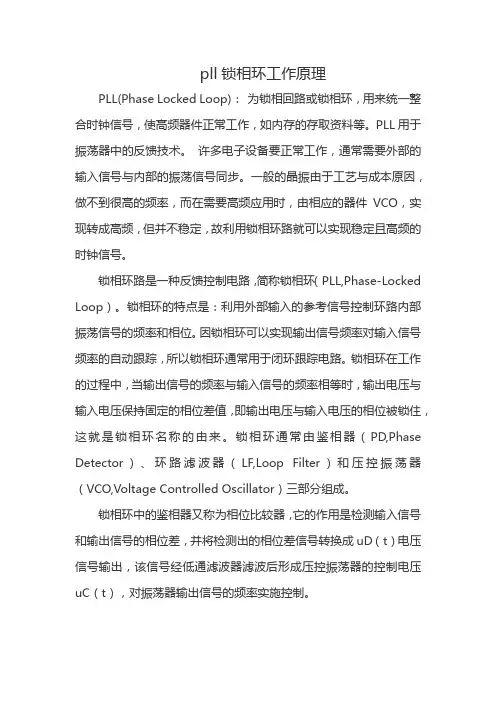

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

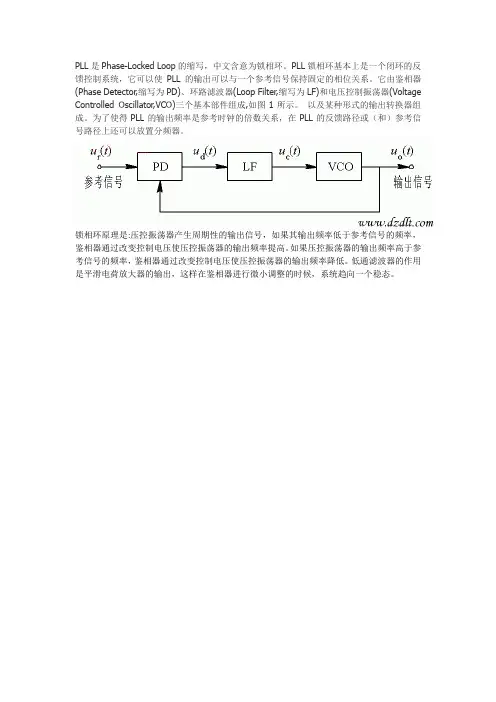

PLL是Phase-Locked Loop的缩写,中文含意为锁相环。

PLL锁相环基本上是一个闭环的反馈控制系统,它可以使PLL的输出可以与一个参考信号保持固定的相位关系。

它由鉴相器(Phase Detector,缩写为PD)、环路滤波器(Loop Filter,缩写为LF)和电压控制振荡器(Voltage Controlled Oscillator,VCO)三个基本部件组成,如图1所示。

以及某种形式的输出转换器组成。

为了使得PLL的输出频率是参考时钟的倍数关系,在PLL的反馈路径或(和)参考信号路径上还可以放置分频器。

锁相环原理是:压控振荡器产生周期性的输出信号,如果其输出频率低于参考信号的频率,鉴相器通过改变控制电压使压控振荡器的输出频率提高。

如果压控振荡器的输出频率高于参考信号的频率,鉴相器通过改变控制电压使压控振荡器的输出频率降低。

低通滤波器的作用是平滑电荷放大器的输出,这样在鉴相器进行微小调整的时候,系统趋向一个稳态。

详解PLL锁定时间精确测量

时钟速度的提高和更严格的信号时序增加了对精准的高频模块的需求。

PLL(锁相环)基于输入信号生成高频输出信号,是一种备受欢迎的用于产

生高频信号的电路。

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。

达到锁定状态所需的时间称为锁定时间,这是

PLL设计最关键的参数之一。

因此,需要非常精确地加以测量。

图1显示了PLL及其组件的简化框图。

图1在锁相环中,VCO信号被划分并发回与参考信号进行比较。

PLL锁定时间是通电后,PLL需要与相匹配(PLL参考时钟和PLL反馈

时钟之间)产生目标频率的时间。

图2显示在反馈时钟和参考时钟的频率相

同时,锁定信号为高。

图2反馈时钟和参考时钟的频率相同时,PLL锁定信号为高

PLL的设计通常采用一种方式,让锁定时间尽可能短,同时仍然提供尽可能高的稳定性。

取决于参考频率的范围,实现锁定状态所花费的时间有所不。

PLL(Phase-Locked Loop,锁相环)是一种电路系统,用于在输入信号和参考信号之间实现相位同步。

它通过调节输出信号的相位和频率,使其与参考信号保持稳定的相位关系。

PLL的基本原理包括以下几个组成部分:

相频比较器(Phase-Frequency Detector,PFD):相频比较器用于比较输入信号和参考信号之间的相位差和频率差,并产生一个误差信号。

锁相环滤波器(Loop Filter):锁相环滤波器对相频比较器的误差信号进行滤波和平滑处理,生成一个控制电压信号。

电压控制振荡器(Voltage-Controlled Oscillator,VCO):VCO根据控制电压的变化来调节输出信号的频率。

控制电压的大小和极性将决定VCO的频率偏移方向和速度。

分频器(Divider):分频器将VCO的输出信号分频得到参考信号,用于与输入信号进行比较。

反馈回路:通过将分频器的输出信号与输入信号进行比较,将误差信号反馈给相频比较器,形成闭环控制系统。

基本工作流程如下:

初始状态下,VCO的输出信号与参考信号存在相位和频率的差异,PFD检测到相位差和频率差,产生误差信号。

锁相环滤波器对误差信号进行滤波,产生控制电压。

控制电压作用于VCO,调节其频率,使其逐渐与参考信号保持同步。

通过反馈回路,将分频器的输出信号与输入信号进行比较,继续调整VCO的频率和相位,以使输入信号和输出信号的相位关系保持稳定。

PLL可以应用于许多领域,如通信系统中的频率合成器、时钟同步、调频解调器等。

它能够实现高精度的频率和相位同步,具有很强的抗噪声和抗干扰能力。

标题:PLL环路参数的计算与建模引言:相位锁定环路(Phase-Locked Loop,简称PLL)是一种常用的电子系统调频技术。

它可以将输入信号的频率与参考信号的频率进行同步,实现频率合成、时钟恢复等功能。

本文将详细介绍PLL环路参数的计算与建模方法,以帮助读者更好地理解和应用PLL技术。

一、PLL环路基本原理1.1 相位锁定环路的定义相位锁定环路是一种闭环控制系统,由相位比较器、积分环节、低通滤波器和VCO(Voltage-Controlled Oscillator,电压控制振荡器)组成。

通过不断调整VCO的频率或相位,使得输入信号与参考信号保持同步。

1.2 PLL环路的工作原理首先,相位比较器将输入信号与参考信号进行比较,得到相位误差信号。

然后,相位误差信号经过积分环节和低通滤波器处理后,控制VCO的频率或相位。

最终,VCO的输出信号被反馈给相位比较器,形成一个闭环控制系统。

二、PLL环路参数的计算2.1 带宽与稳定裕度PLL的带宽决定了其响应速度和稳定性。

带宽越大,系统的追踪能力越强,但也容易产生噪声和震荡。

带宽的计算可以根据系统的要求和参考信号的频率来确定。

稳定裕度是指PLL系统在输入信号频率变化时的稳定性,一般通过相位裕度和增益裕度来描述。

2.2 频率分辨率与拉RANGE频率分辨率是指PLL系统能够分辨的最小频率变化量,它与VCO 的调谐范围(拉RANGE)有关。

拉RANGE表示VCO可以调整的频率范围,一般由VCO的设计参数确定。

频率分辨率的计算可以通过拉RANGE除以分辨率比得到。

2.3 相位噪声与抖动相位噪声是指PLL系统输出信号在频谱上的相位随机变化。

抖动是指PLL系统输出信号的周期性相位扰动。

相位噪声和抖动对于某些应用场合具有重要影响,一般需要根据系统需求进行计算和优化。

三、PLL环路的建模方法3.1 传递函数模型传递函数模型是一种常用的PLL环路建模方法,通过建立输入信号与输出信号之间的传递函数关系,可以分析PLL系统的频率响应和稳定性。

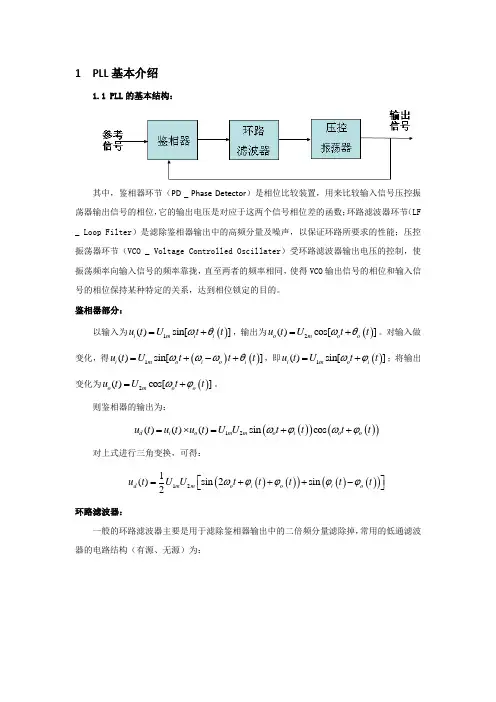

1 PLL 基本介绍1.1 PLL 的基本结构:其中,鉴相器环节(PD _ Phase Detector )是相位比较装置,用来比较输入信号压控振荡器输出信号的相位,它的输出电压是对应于这两个信号相位差的函数;环路滤波器环节(LF _ Loop Filter )是滤除鉴相器输出中的高频分量及噪声,以保证环路所要求的性能;压控振荡器环节(VCO _ Voltage Controlled Oscillater )受环路滤波器输出电压的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO 输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

鉴相器部分:以输入为()1()sin[]i m i i u t U t t ωθ=+,输出为()2()cos[]o m o o u t U t t ωθ=+。

对输入做变化,得()()1()sin[]i m o i o i u t U t t t ωωωθ=+-+,即()1()s in []i m o i u t U t tωϕ=+;将输出变化为()2()cos[]o m o o u t U t t ωϕ=+。

则鉴相器的输出为: ()()()()12()()()sin cos d i o m m o i o o u t u t u t U U t t t t ωϕωϕ=⨯=++对上式进行三角变换,可得:()()()()()()121()sin 2sin 2d m m o i o i o u t U U t t t t t ωϕϕϕϕ⎡⎤=+++-⎣⎦ 环路滤波器:一般的环路滤波器主要是用于滤除鉴相器输出中的二倍频分量滤除掉,常用的低通滤波器的电路结构(有源、无源)为:此外,也可以使用“切比雪夫滤波器”进行滤波。

以上边的有源滤波器电路进行公式变换,可以得到:21()1()d c u s R CS u s R CS+=- 即,LF 环节可以等效视为一个PI 控制环节。

PLL和DLL:都是锁相环,区别在哪里?DLL:一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的家伙。

DLL是基于数字抽样方式,在输入时钟和反馈时钟之间插入延迟,使输入时钟和反馈时钟的上升沿一致来实现的。

又称数字锁相环。

PLL:使用了电压控制延迟,用VCO来实现和DLL中类试的延迟功能。

又称模拟锁相环。

功能上都可以实现倍频、分频、占空比调整,但是PLL调节范围更大,比如说:XILINX使用DLL,只能够2、4倍频;ALTERA的PLL可以实现的倍频范围就更大毕竟一个是模拟的、一个是数字的。

两者之间的对比:对于PLL,用的晶振存在不稳定性,而且会累加相位错误,而DLL在这点上做的好一些,抗噪声的能力强些;但PLL在时钟的综合方面做得更好些。

总的来说PLL的应用多,DLL则在jitter power precision等方面优于PLL。

目前大多数FPGA厂商都在FPGA内部集成了硬的DLL(Delay-Locked Loop)或者PLL(Phase-Locked Loop),用以完成时钟的高精度、低抖动的倍频、分频、占空比调整移相等。

目前高端FPGA 产品集成的DLL和PLL资源越来越丰富,功能越来越复杂,精度越来越高(一般在ps的数量级)。

Xilinx芯片主要集成的是DLL,而Altera芯片集成的是PLL。

Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中,CLKDLL的增强型模块为DCM(Digital Clock Manager)。

Altera芯片的PLL模块也分为增强型PLL(Enhanced PLL)和高速(Fast PLL)等。

这些时钟模块的生成和配置方法一般分为两种,一种是在HDL代码和原理图中直接实例化,另一种方法是在IP核生成器中配置相关参数,自动生成IP。

pll频率合成与锁相电路设计频率合成与锁相电路设计是电子工程中非常重要的主题。

频率合成是指通过组合不同频率的信号来生成新的频率信号的技术。

而锁相电路是一种控制系统,用于将一个振荡器的输出信号与另一个参考信号进行比较,并调整振荡器的频率,使其与参考信号同步。

下面我将从频率合成和锁相电路设计两个方面来详细解释。

首先,频率合成是通过将不同频率的信号进行合成来生成新的频率信号。

这可以通过数字信号处理技术或者模拟电路来实现。

在数字信号处理中,可以使用相位锁定环(PLL)来实现频率合成。

PLL是一种反馈系统,它通过比较输入信号和反馈信号的相位差来调整振荡器的频率,从而实现频率合成。

另一种常见的频率合成方法是使用分频器和相位加减器来实现频率倍增或者分频。

在模拟电路中,可以使用混频器和滤波器来实现频率合成。

其次,锁相电路是一种控制系统,用于将一个振荡器的输出信号与另一个参考信号进行比较,并调整振荡器的频率,使其与参考信号同步。

锁相电路通常包括相位比较器、环路滤波器、控制电压发生器和振荡器等组件。

相位比较器用于比较输入信号和参考信号的相位差,然后通过环路滤波器和控制电压发生器来调整振荡器的频率,使其与参考信号同步。

锁相电路在通信系统、雷达系统和惯性导航系统等领域有着广泛的应用。

在设计频率合成和锁相电路时,需要考虑许多因素,包括振荡器的稳定性、相位噪声、环路带宽、锁定时间等。

此外,还需要考虑电源噪声抑制、温度漂移补偿、环路稳定性分析等问题。

因此,频率合成和锁相电路的设计需要综合考虑电路设计、信号处理、控制系统等多个方面的知识。

总之,频率合成和锁相电路设计涉及到广泛的知识领域,包括信号处理、控制系统、电路设计等。

在实际应用中,需要根据具体的要求和限制来选择合适的设计方案,并进行系统级的分析和优化。

希望这个回答能够帮助你更好地理解频率合成和锁相电路设计。

PLL:为锁相回路,用来统一整合时脉讯号,使内存能正确的存取资料。

锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。

PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。

对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的10MHz 背板时钟同步来实现锁相环同步的。

/support/devices/pll_clock/basics/pll-basics.html---------------------------------------------------------------------------------------------PLL在电子电路中的应用PLL即锁相环,基本原理图是:输入信号-> 鉴相器-> 低通滤波器-> 压控振荡器-> 输出信号|_____________________ |鉴相器有两个输入,分别是输入信号和压控振荡器的输出信号,在二者相位差和频率差不是很大的情况下,鉴相器的输出与两输入信号之差成正比,鉴相器的输出为模拟信号,其通过低通滤波器虑除高频杂波,后进入压控振荡器,压控振荡器的输出频率随其输入电压的改变而改变。

PLL详解

什么是锁相环呢?

MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使

系统更加快速稳定运行,需要提升系统所需要的时钟频率。

这就得用到锁相环了。

例如MCU用的外部晶振是16M的无源晶振,则可以通过锁相环PLL把系统时钟倍频到24M,

从而给系统提供更高的时钟信号,提高程序的运行速度。

51单片机,AVR单片机内部没有锁相环电路,其系统时钟直接由外部晶振提供。

而XS128内部集成了锁相环电路,其系

统时钟既可由外部晶振直接提供,也可以通过锁相环倍频后提供,当然,还有由XS128内部的时钟电路来提供(当其

它来源提供的系统时钟不稳定时,内部时钟电路就起作用了,也就是自时钟模式)。

锁相环作为一个提供系统时钟的模块,是一个基本的模块,几乎每次编程序都得用到。

下面记一下怎样配置锁相环来设定想要的系统时钟。

锁相环PLL、自时钟模式和前面说的实时中断RTI、看门狗COP都属于系统时钟与复位CRG中的模块,固前面用到的寄存器,这里有些会再用到。

在程序中配置锁相环的步骤如下:

第一、禁止总中断;

第二、寄存器CLKSEL的第七位置0,即CLKSEL_PLLSEL=0。

选择时钟源为外部晶振OSCCLK,在PLL程序执行前,内部总线频率为OSCCLK/2。

CLKSEL_PLLSEL=0时,系统时钟由外部晶振直接提供,系统内部总线频率=OSCCLK/2(OSCCLK为外部晶振频率)。

CLKSEL_PLLSEL=1时,系统时钟由锁相环提供,此时系统内部总线频率=PLLCLK/2 (PLLCLK为锁相环倍频后的频率)。

第三、禁止锁相环PLL,即

PLLCTL_PLLON=0。

当PLLCTL_PLLON=0时,关闭PLL电路。

当PLLCTL_PLLON=1时,打开PLL电路。

第四、根据想要的时钟频率设置SYNR和REFDV两个寄存器。

SYNR和REFDV两个寄存器专用于锁相环时钟PLLCLK的频率计算,计算公式是:

PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

其中,PLLCLK为PLL模块输出的时钟频率;OSCCLK为晶振频率;SYNR、REFDV分别为寄存器SYNR、REFDV 中的值。

这两个寄存器只有在PLLSEL=0时才能够写入(这

里就是第二步的设置原因所在了)。

第五、打开PLL,即PLLCTL_PLLON=1。

第六、CRGFLG_LOCK位,确定PLL是否稳定。

当锁相环PLL电路输出的频率达到目标频率的足够小的误差范围内时,LOCK位置1,此时说明PLLCLK已经稳定,可以作为系统的时钟了。

该位在正常情况下为只读位。

第七、PLLCLK稳定后,允许锁相环时钟源PLLCLK为系统提供时钟,即CLKSEL_PLLSEL=1。

到这里,锁相环的设置就完毕了。

如果想更灵活地配置系统时钟,就还得用到下面的寄存器了,下面逐一说说:

1、CRGFLG_LOCKIF 锁相环的中断标志位。

当系统时钟因为稳定或不稳定而导致LOCK位(上面已提到)变化时,该位置1。

此时,如果CRGINT_LOCKIE=1,则产生中断。

CRGINT_LOCKIE=1时,则允许产生锁相环锁定中断。

CRGINT_LOCKIE=0时,则不允许。

2、CLKSEL_PLLWAI是等待模式PLL停止位。

当CLKSEL_PLLWAI=1时,系统进入等待模式时,锁相环PLL停止工作。

当CLKSEL_PLLWAI=0时,系统进入等待模式时,锁相环PLL仍然工作。

下面顺便说一下与自时钟模式相关的几个寄存器:

CRGFLG_SCMIF 自时钟模式中断标志位。

当SCM位变化时,该位置1。

此时,如果CRGINT_SCMIE=1,则产生中断。

CRGFLG_SCM 自时钟模式状态位。

当晶振频率不稳定时,该位置1,系统会进入自时钟模式,系统的时钟将由自时钟模式下的时钟提供。

CRGINT_SCMIE 自时钟模式中断的使能位。

当CRGINT_SCMIE=1时,允许产生自时钟模式中断。

当CRGINT_SCMIE=0时,不能产生自时钟模式中断。

PLLCTL_SCME 自时钟模式使能位。

在自时钟模式下,该位不能被清0。

PLLCTL_SCME=1时,晶振时钟失灵系统将强制进入自时钟模式。

当PLLCTL_SCME=0时,晶振失灵将导致时钟监控器复位。

下面附一条锁相环的初始化程序;

void MCUInit()

{

DISABLE_INTERRUPTS; //(1)禁止总中断

CLKSEL &= 0x7f;

//(2)CLKSEL的第7位置0,选择系统时钟源为OSCCLK

PLLCTL &= 0xbf; // (3)禁止PLL , PLLCTL.6(pllon)设为0;先关闭PLL

SYNR = 0x01; //(4)根据需要的时钟频率设置SYNR和REFDV寄存器

REFDV = 0x00;

PLLCTL |= (1<<6); //(5)打开PLL , PLLCTL.6(pllon)设为1;开PLL

while (( CRGFLG&0x08) == 0x00);

//(6)通过判断LOCK位,

//确定PLL是否稳定

CLKSEL |= (1<<7); //(7)时钟频率稳定后,允许锁相环时钟源作为系统时钟源;

//本句执行后:BusClock=PLLCLK/2

}。