锁相环(PLL)基本原理

- 格式:ppt

- 大小:858.00 KB

- 文档页数:74

fpga pll的原理

FPGA(现场可编程门阵列)是一种可编程逻辑器件,它可以根据需要重新配置其内部电路以执行特定的计算任务。

PLL(锁相环)是一种电路,用于产生稳定的时钟信号,通常用于时序控制和数据传输。

FPGA中的PLL模块通常用于时钟管理和信号处理,下面我将从多个角度来解释FPGA中PLL的原理。

首先,PLL由几个主要部分组成,相位比较器、环形数字控制振荡器(DCO)、低通滤波器和分频器。

PLL的工作原理是通过不断调整DCO的频率,使其输出的信号与参考信号的相位和频率保持一致。

相位比较器用于比较参考信号和反馈信号的相位差,并产生一个误差信号,该信号被送入低通滤波器,滤波器输出的信号作为控制信号送入DCO,调整其频率直到误差信号趋近于零。

在FPGA中,PLL模块通常由数字控制器和振荡器组成。

数字控制器负责接收外部输入的参数,如分频系数、反馈倍频等,并根据这些参数配置PLL的工作模式。

振荡器负责产生稳定的时钟信号,并根据数字控制器的指令调整输出频率和相位。

另外,FPGA中的PLL还可以提供多个时钟输出,并支持时钟切

换和相位对齐等功能。

这使得PLL在FPGA中可以灵活地适应不同的时序要求,满足复杂的时序控制和数据处理需求。

总的来说,FPGA中的PLL通过数字控制器和振荡器实现稳定的时钟信号生成和时序控制,从而满足复杂的时序要求和数据处理需求。

通过不断调整振荡器的频率和相位,PLL可以使FPGA在不同的工作模式下灵活地适应各种应用场景。

c语言中锁相环程序语句摘要:C语言中锁相环程序语句概述与实例解析一、锁相环(PLL)的基本原理1.锁相环的组成2.锁相环的工作原理二、C语言中实现锁相环的程序语句1.锁相环参数设置2.锁相环初始化3.锁相环控制算法4.锁相环状态监测与调整三、实例分析1.简易锁相环电路2.基于C语言的锁相环控制程序3.程序运行效果与分析四、锁相环的应用领域及发展趋势1.锁相环在通信系统中的应用2.锁相环在控制系统中的应用3.锁相环技术的发展趋势正文:一、锁相环(PLL)的基本原理1.锁相环的组成锁相环(Phase Locked Loop,简称PLL)主要由相位比较器、放大器、滤波器和解调器等部分组成。

这些部分协同工作,实现对输入信号相位的锁定。

2.锁相环的工作原理锁相环的工作原理主要是通过相位比较器比较输入信号和本地信号的相位差,然后根据相位差的大小调整本地信号的频率,使得输入信号与本地信号的相位差逐渐减小,最终实现相位锁定。

二、C语言中实现锁相环的程序语句1.锁相环参数设置在C语言中,可以通过定义寄存器变量和设置相应的数值来配置锁相环的参数,例如:```c// 设置锁相环参数reg_lpc = 0x1234; // 设置低通滤波器参数reg_vco_ctrl = 0x5678; // 设置VCO控制参数reg_divider = 0x9ABC; // 设置分频器参数```2.锁相环初始化初始化锁相环时,需要对各个模块进行启动和设置:```c// 初始化锁相环void init_pll(){// 初始化低通滤波器lpf_init();// 初始化VCO控制模块vco_ctrl_init();// 初始化分频器divider_init();}```3.锁相环控制算法在C语言中,可以实现锁相环的控制算法,例如:```c// 更新VCO频率void update_vco_frequency(uint16_t vco_ctrl_data) {// 根据VCO控制数据更新VCO频率vco_update_frequency(vco_ctrl_data);}// 锁相环状态监测与调整void monitor_and_adjust_pll_state(){// 读取锁相环状态uint16_t pll_state = pll_read_state();// 根据状态进行调整if (pll_state == PLL_LOCKED){// 锁定状态,调整VCO频率update_vco_frequency(reg_vco_ctrl);}else if (pll_state == PLL_UNLOCKED){// 未锁定状态,启动锁相环init_pll();}}四、锁相环的应用领域及发展趋势1.锁相环在通信系统中的应用锁相环技术在通信系统中广泛应用于频率合成、本振生成、频率变换等环节,为实现系统的高稳定性和精确度提供保障。

锁相环放大器的原理及应用锁相环放大器(Phase-locked loop amplifier,简称PLL放大器)是一种电子放大器,利用锁相环的原理,对输入信号进行放大,同时保持输出信号与输入信号的相位关系稳定。

锁相环放大器的原理主要包括三个基本模块:相位比较器、低通滤波器和VCO(Voltage-Controlled Oscillator)。

1. 相位比较器(Phase Comparator):相位比较器用于比较输入信号和反馈信号的相位差,并产生一个误差信号。

常见的相位比较器有乘法型相位比较器和加法型相位比较器。

2. 低通滤波器(Low Pass Filter):低通滤波器用于滤除相位比较器输出信号中的高频噪声,只保留误差信号的直流分量,同时具有一定的延迟作用。

3. VCO(Voltage-Controlled Oscillator):VCO是一个可通过电压控制频率的振荡器。

它的频率由输入的控制电压决定,通常与输入信号的频率相等,但相位可能会有一定的偏差。

通过调整VCO的控制电压,可以改变输出信号的相位与输入信号的相位之间的差距。

锁相环放大器的应用非常广泛。

以下是一些常见的应用场景:1. 时钟恢复:锁相环放大器经常用于从数字信号中恢复时钟信号。

通过将输入信号和本地时钟信号进行相位比较,可以产生一个误差信号,并通过调整VCO的频率,将输出信号的相位与输入信号的相位进行同步,从而恢复出准确的时钟信号。

2. 数据通信:锁相环放大器广泛应用于高速数据通信系统中。

通过对接收到的数据信号与本地时钟信号进行相位比较,并调整VCO的频率,可以保证接收到的数据信号与本地时钟信号的相位同步,从而实现可靠的数据传输。

3. 降噪增益:锁相环放大器可以用于降低输入信号中的噪声,并放大信号的幅度。

通过对输入信号和反馈信号进行相位比较,并通过调整VCO的频率,可以实现对信号的放大,并同时抑制输入信号中的噪声。

总之,锁相环放大器通过利用反馈控制的方式,可以实现对输入信号的放大,并保持输出信号与输入信号的相位关系稳定。

dll锁相环原理DLL(数字锁相环)是一种数字电路,用于锁定输入信号与一定频率的参考时钟信号相位。

它是一种数字PLL(锁相环)的特殊情况,可以广泛应用于数字通信、音频处理以及高速数字系统中。

DLL锁相环的工作原理可以归纳为以下几个步骤:1.将参考时钟信号分频:参考时钟信号通过一系列的分频器,被分成与输入信号相同的频率。

2.产生相位差信号:将分频后的参考时钟信号与输入信号比较,产生一个相位差信号。

3.通过数字滤波器进行滤波:将相位差信号通过数字滤波器进行滤波以去除高频噪声。

4.控制输出时钟信号:根据滤波后的相位差信号的大小和正负,控制VCO(电压控制振荡器)输出的时钟信号的相位和频率。

此时输出的时钟信号与输入信号的相位差被锁定在一个可接受的范围内,从而保证了系统的信号同步性和稳定性。

DLL锁相环有许多优点,如下所述:1.响应速度快:使用数字电路的方式,锁相环的响应速度非常快。

因此,它适用于要求精度高且信号变化频繁的应用。

2.实现简单:数字锁相环相对于传统的模拟锁相环,其电路实现更加简单,而且不需要精密的模拟电路设计。

3.稳定性强:由于数字滤波器可以进行高精度的滤波,因此数字锁相环的稳定性也比模拟锁相环更高。

这使得它适用于对相位稳定性要求高的应用场景,如通信系统中的时钟恢复等。

4.适应性强:数字锁相环可以适应不同频率和相位差的输入信号,因此其应用范围非常广泛。

在音频处理中,它可以被用于对频率和相位进行校正,确保各种波形信号的正确性。

在数字通信中,它可以被用于时钟恢复、卫星通信、调制解调器等领域。

总之,DLL锁相环是一种对精度和性能有高要求的应用具有重要意义和应用价值的技术,它在各个领域有着广泛应用,推动着数字化电子技术的飞速发展。

PLL(Phase-Locked Loop,锁相环)是一种电路系统,用于在输入信号和参考信号之间实现相位同步。

它通过调节输出信号的相位和频率,使其与参考信号保持稳定的相位关系。

PLL的基本原理包括以下几个组成部分:

相频比较器(Phase-Frequency Detector,PFD):相频比较器用于比较输入信号和参考信号之间的相位差和频率差,并产生一个误差信号。

锁相环滤波器(Loop Filter):锁相环滤波器对相频比较器的误差信号进行滤波和平滑处理,生成一个控制电压信号。

电压控制振荡器(Voltage-Controlled Oscillator,VCO):VCO根据控制电压的变化来调节输出信号的频率。

控制电压的大小和极性将决定VCO的频率偏移方向和速度。

分频器(Divider):分频器将VCO的输出信号分频得到参考信号,用于与输入信号进行比较。

反馈回路:通过将分频器的输出信号与输入信号进行比较,将误差信号反馈给相频比较器,形成闭环控制系统。

基本工作流程如下:

初始状态下,VCO的输出信号与参考信号存在相位和频率的差异,PFD检测到相位差和频率差,产生误差信号。

锁相环滤波器对误差信号进行滤波,产生控制电压。

控制电压作用于VCO,调节其频率,使其逐渐与参考信号保持同步。

通过反馈回路,将分频器的输出信号与输入信号进行比较,继续调整VCO的频率和相位,以使输入信号和输出信号的相位关系保持稳定。

PLL可以应用于许多领域,如通信系统中的频率合成器、时钟同步、调频解调器等。

它能够实现高精度的频率和相位同步,具有很强的抗噪声和抗干扰能力。

锁相环技术原理及fpga实现一、锁相环技术原理锁相环(Phase Locked Loop,PLL)是一种电路技术,用于在输入信号与参考信号之间产生固定的相位关系。

它由一个相位比较器、一个低通滤波器和一个控制电压源组成。

1. 相位比较器相位比较器是锁相环的核心部件,用于比较输入信号和参考信号的相位差。

常见的有两种类型:单极性和双极性。

单极性相位比较器只能检测到一个方向的相位差,而双极性可以检测两个方向的相位差。

2. 低通滤波器低通滤波器用于对比较结果进行平滑处理,去除高频噪声和不稳定因素。

3. 控制电压源控制电压源根据低通滤波器输出的直流电压来调整VCO(VoltageControlled Oscillator)的频率。

当输入信号与参考信号之间存在相位差时,控制电压源会调整VCO输出频率使其与参考信号同步。

二、FPGA实现FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,可以被重新编程以实现各种功能。

在FPGA中实现锁相环的过程主要包括以下几个步骤:1. 时钟分频器首先需要将输入信号进行分频,使其与参考信号具有相同的频率。

这可以通过时钟分频器实现,FPGA中常见的时钟分频器有计数器和DDS(Direct Digital Synthesis)。

2. 相位比较器相位比较器可以采用XOR门或D触发器等逻辑门电路实现。

其中XOR门可以检测到单极性相位差,而D触发器可以检测到双极性相位差。

3. 低通滤波器低通滤波器可以使用FPGA中的数字滤波器实现,常见的有FIR (Finite Impulse Response)和IIR(Infinite Impulse Response)滤波器。

4. 控制电压源控制电压源通常由DAC(Digital-to-Analog Converter)实现,将数字控制信号转换为模拟电压输出。

这个电压输出会通过OPA (Operational Amplifier)放大并接入VCO来调整其输出频率。

锁相环(PLL)详解

锁相环(PLL)详解锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

而一般情形下,这种锁相环的三个组成部分和相应的运作机理是:

1 鉴相器:用于判断锁相器所输出的时钟信号和接收信号中的时钟的相差的幅度;

2 可调相/调频的时钟发生器器:用于根据鉴相器所输出的信号来适当的调节锁相器内部的时钟输出信号的频率或者相位,使得锁相器完成上述的固定相差功能;

3 环路滤波器:用于对鉴相器的输出信号进行滤波和平滑,大多数情形下是一个低通滤波器,用于滤除由于数据的变化和其他不稳定因素对整个模块的影响。

从上可以看出,大致有如下框图:

┌─────┐┌─────┐┌───────┐

→─┤鉴相器├─→─┤环路滤波器├─→─┤受控时钟发生器├→┬─→└──┬──┘└─────┘└───────┘│

↑↓

└──────────────────────────┘

可见,是一个负反馈环路结构,所以一般称为锁相环(PLL: Phase Locking Loop)。

锁相环有很多种类,可以是数字的也可以是模拟的也可以是混合的,可以用于恢复载波也可以用于恢复基带信号时钟。

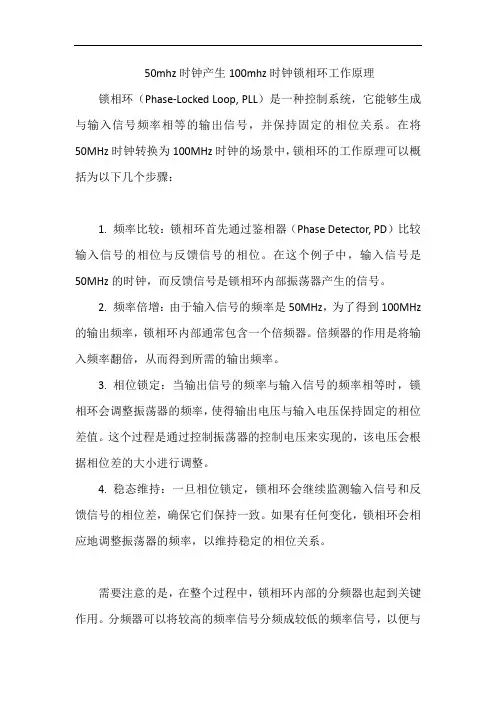

50mhz时钟产生100mhz时钟锁相环工作原理锁相环(Phase-Locked Loop, PLL)是一种控制系统,它能够生成与输入信号频率相等的输出信号,并保持固定的相位关系。

在将50MHz时钟转换为100MHz时钟的场景中,锁相环的工作原理可以概括为以下几个步骤:

1. 频率比较:锁相环首先通过鉴相器(Phase Detector, PD)比较输入信号的相位与反馈信号的相位。

在这个例子中,输入信号是50MHz的时钟,而反馈信号是锁相环内部振荡器产生的信号。

2. 频率倍增:由于输入信号的频率是50MHz,为了得到100MHz 的输出频率,锁相环内部通常包含一个倍频器。

倍频器的作用是将输入频率翻倍,从而得到所需的输出频率。

3. 相位锁定:当输出信号的频率与输入信号的频率相等时,锁相环会调整振荡器的频率,使得输出电压与输入电压保持固定的相位差值。

这个过程是通过控制振荡器的控制电压来实现的,该电压会根据相位差的大小进行调整。

4. 稳态维持:一旦相位锁定,锁相环会继续监测输入信号和反馈信号的相位差,确保它们保持一致。

如果有任何变化,锁相环会相应地调整振荡器的频率,以维持稳定的相位关系。

需要注意的是,在整个过程中,锁相环内部的分频器也起到关键作用。

分频器可以将较高的频率信号分频成较低的频率信号,以便与

输入的50MHz信号进行比较。

这样,即使参考时钟是100MHz,分频器也可以将其分频到50MHz,以便与输入时钟进行相位比较。

综上所述,锁相环通过精确的反馈控制机制,能够实现输入信号频率的倍增,并且保持输出信号与输入信号的相位同步,从而产生稳定且准确的100MHz时钟信号。

DFPLL锁相环原理概述锁相环(Phase-Locked Loop,简称PLL)是一种常见的电子设备,用于同步信号的生成和恢复。

DFPLL(Digital Frequency Phase-Locked Loop)是一种数字锁相环,它采用数字技术实现锁相环的功能。

本文将详细解释DFPLL锁相环的基本原理。

锁相环基本结构锁相环由三个基本组成部分构成:相位比较器(Phase Comparator)、环路滤波器(Loop Filter)和振荡器(Oscillator)。

1.相位比较器:相位比较器用于比较输入信号和反馈信号之间的相位差,并将相位差转换为电压差。

常见的相位比较器有比较器、乘法器等。

2.环路滤波器:环路滤波器用于将相位差转换为控制信号,调整振荡器的频率。

它一般由低通滤波器组成,用于滤除高频噪声。

3.振荡器:振荡器产生参考信号,其频率和相位可以通过环路滤波器的控制信号进行调节。

常见的振荡器有晶体振荡器、VCO(Voltage-ControlledOscillator)等。

DFPLL锁相环原理DFPLL锁相环采用数字技术实现锁相环的功能,其基本原理如下:1.输入信号采样:DFPLL首先对输入信号进行采样,将其转换为数字信号。

采样率需要满足奈奎斯特采样定理,即大于输入信号的最高频率的两倍。

2.相位比较:将输入信号和反馈信号(由振荡器产生)进行相位比较。

相位比较器会计算两个信号之间的相位差,并输出一个数字量表示相位差。

3.数字控制信号生成:相位差经过环路滤波器后,产生一个控制信号。

这个控制信号根据相位差的大小和方向,调整振荡器的频率和相位。

4.数字振荡器控制:控制信号经过数字控制模块,调整数字振荡器的频率和相位。

数字振荡器可以通过改变计数器的计数速度来调整频率,通过改变计数器的初始值来调整相位。

5.反馈信号生成:数字振荡器产生的信号被反馈回相位比较器,与输入信号进行比较。

通过不断调整数字振荡器的频率和相位,使得输入信号和反馈信号的相位差趋近于零,实现同步。

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为:(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

1引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

2全数字锁相环的体系结构和工作原理74XX297是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为M fc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

锁相环的基本组成锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图所示锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

锁相环的工作原理锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。

PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。

对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI 线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的10MHz背板时钟同步来实现锁相环同步的。

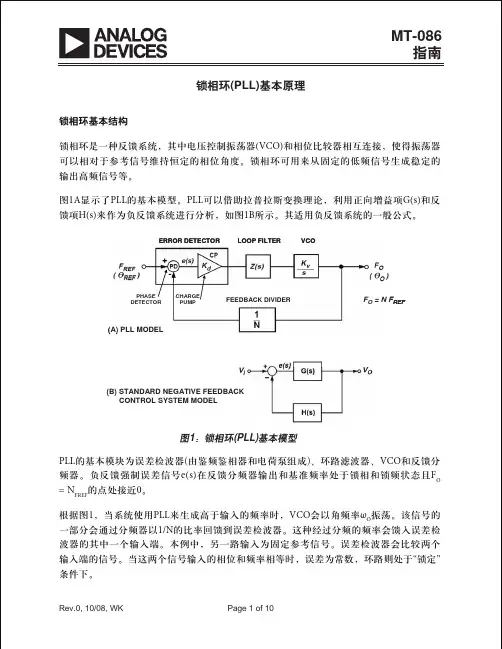

1锁相环的基本原理1.1 锁相环的基本构成锁相环路(PLL )是一个闭环的跟踪系统,它能够跟踪输入信号的相位和频率。

确切地讲,锁相环是一个使用输出信号(由振荡器产生的)与参考信号或者输入信号在频率和相位上同步的电路。

在同步(通常称为锁定)状态,振荡器输出信号和参考信号之间的相位差为零,或者保持常数。

如果出现相位误差,一种控制机理作用到振荡器上,使得相位误差再次减小到最小。

在这样的控制系统中,实际输出信号的相位锁定到参考信号的相位,因而我们称之为锁相环。

锁相环在无线电技术的许多领域,如调制与解调、频率合成、数字同步系统等方面得到了广泛的应用,已经成为现代模拟与数字通信系统中不可缺少的基本部件。

锁相环通常由鉴相器(PD ),环路滤波器(LF )和压控振荡器(VCO )三个基本部件组成。

如图1-1所示:图1-1 锁相环的基本构成在PLL 中,PD 是一个相位比较器,比较基准信号(输入信号)i u (t )与输出信号o u (t )之间的相位偏差()e t ,并由此产生误差信号()d u t ;LF 是一个低通滤波器,用来滤除()d u t 中的高频成分,起滤波平滑作用,以保证环路稳定和改善环路跟踪性能,最终输出控制电压()c u t ;VCO 是一个电压/频率变换装置,产生本地振荡频率,其振荡频率受()c u t 控制,产生频率偏移,从而跟踪输入信号的频率。

整个锁相环路根据输入信号与本地振荡信号之间的相位误差对本地振荡信号的相位进行连续不断的反馈调节,从而达到使本地振荡信号相位跟踪输入信号相位的目的。

1.1.1 鉴相器鉴相器是一个相位比较器,比较两个输入信号的相位,产生误差相位,并转换为误差电压()d u t 。

鉴相器有多种类型,如模拟乘法器型、取样保持型、边沿触发数字型等,其特性也可以是多种多样的,有正弦特性、三角特性、锯齿特性等,作为原理分析,通常使用正弦特性的鉴相器,理由是正弦理论比较成熟,分析简单方便,实际上各种鉴相特性当信噪比降低时,都趋向于正弦特性。

锁相环工作原理.锁相环工作原理锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。

其作用是使得电路上的时钟和某一外部时钟的相位同步。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

锁相环路是一个相位反馈、)PD(鉴相器它由以下三个基本部件组成:自动控制系统。

.环路滤波器(LPF)和压控振荡器(VCO)。

锁相环的工作原理:1. 压控振荡器的输出经过采集并分频;2. 和基准信号同时输入鉴相器;3. 鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4. 控制VCO,使它的频率改变;5. 这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环可用来实现输出和输入两个信号之间的相位同步。

当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。

这时,压控振荡器按其固有频率fv进行自由振荡。

当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。

如果fR和fv相差不uR进行鉴相的结果,输出一个与uv和uR大,鉴相器对.和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。