PLL电路的基本工作原理

- 格式:docx

- 大小:130.33 KB

- 文档页数:4

相位控制器工作原理相位控制器是一种电子设备,它可以精确地调节电信号的相位,从而改变信号的性质和性能。

相位控制器主要应用于通信、雷达、电子干扰、卫星导航等领域,具有非常重要的作用。

相位控制器工作原理相位控制器的工作原理基于相位锁定环路(Phase Locked Loop,PLL)的概念。

PLL是一种基于反馈的电路,可以使输出信号与参考信号保持稳定的相位差。

相位控制器主要由振荡器、相位检测器、环路滤波器和控制电路组成。

振荡器振荡器是相位控制器的关键部分。

它产生一个基准信号,用于与输入信号进行比较,从而控制输入信号的相位。

振荡器主要有晶体管振荡器、陶瓷谐振器、石英晶体振荡器等。

相位检测器相位检测器是相位控制器的另一个重要组成部分。

它将输入信号和基准信号进行比较,从而产生一个误差信号。

相位检测器有多种类型,包括均方根误差检测器、自适应线性判别器、比较器等。

环路滤波器环路滤波器是一种低通滤波器,用于滤除相位检测器输出信号中的高频噪声。

环路滤波器的截止频率应与振荡器的频率相同,以便实现相位锁定。

控制电路控制电路用于根据相位检测器输出的误差信号,调节振荡器的频率和相位,从而实现精确的相位控制。

控制电路主要有比例积分控制器、模糊控制器等。

优点和应用相位控制器具有很多优点。

首先,它可以对信号的相位进行精确控制,从而改变信号的频率、幅度和波形。

其次,相位控制器可以有效消除噪声和干扰,提高信号的质量和稳定性。

最后,相位控制器的结构简单、响应速度快,非常适合于集成电路的制造。

相位控制器主要应用于通信、雷达、卫星导航等领域。

在通信领域,相位控制器可以用于同步传输信号,提高数据传输速率和可靠性;在雷达领域,相位控制器可以用于目标跟踪和识别;在卫星导航领域,相位控制器可以用于卫星信号的接收和处理。

结论相位控制器是一种重要的电子设备,可以精确地调节信号的相位,提高信号的质量和稳定性。

相位控制器的工作原理基于相位锁定环路,主要由振荡器、相位检测器、环路滤波器和控制电路组成。

什么是锁相环(PLL)工作原理及对硬件电路连接的要求锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。

PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz 和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。

对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的10MHz背板时钟同步来实现锁相环同步的。

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

三分频电路原理三分频电路是一种常见的电子电路,它可以将输入信号分成三个相等的频率输出。

在很多电子设备中都会用到三分频电路,比如无线电、通信设备、雷达系统等。

三分频电路的原理和实现方法对于电子工程师来说是非常重要的,下面我们来详细了解一下三分频电路的原理。

首先,我们需要了解一下三分频电路的基本原理。

三分频电路通常采用的是分频器和相位锁定环(PLL)的组合。

分频器是一种电子电路,它可以将输入信号的频率分成几个相等的输出信号。

而PLL是一种控制系统,它可以通过比较输入信号和反馈信号的相位差来调整输出信号的频率,从而实现频率的精确控制。

在三分频电路中,首先输入信号会经过一个分频器,将其频率分成三个相等的部分。

然后,这三个输出信号会分别经过三个相位锁定环,通过精确的相位控制,使得它们的频率和相位保持稳定。

最后,经过相位锁定环调整后的三个信号会作为三分频电路的输出。

三分频电路的实现方法有很多种,其中比较常见的是采用分频器和PLL的组合。

分频器可以采用计数器和触发器等电子元件来实现,而PLL则可以采用锁相环电路和数字控制振荡器等电路来实现。

通过合理的设计和调整,可以实现稳定、精确的三分频电路。

除了分频器和PLL,三分频电路的实现还需要考虑一些其他因素,比如输入信号的幅度、相位噪声、频率稳定度等。

在实际应用中,这些因素都会对三分频电路的性能产生影响,因此需要进行综合考虑和优化设计。

总的来说,三分频电路是一种常见的电子电路,它可以将输入信号分成三个相等的频率输出。

通过分频器和PLL的组合,可以实现稳定、精确的三分频电路。

在实际应用中,需要考虑各种因素对电路性能的影响,进行综合优化设计。

希望本文的介绍能够帮助大家更好地理解三分频电路的原理和实现方法。

第1章PLL工作原理与电路构成1(PLL与频率合成技术简介) 电路的基本工作原理111PLL 电路的三大组成部分1111PLL 的应用与频率合成器3112PLL 电路各部分工作波形3113PLL 电路以及频率合成器的构成412PLL 输出为输入N倍频的方法4121 输出为输入N/M倍频的方法(输入部分接入分频电路)5 122 输出为输入N/M倍频的方法(输出部分接入分频电路)5 123 输出为输入N×M倍频的方法(增设前置频率倍减器)6 124 电路与外差电路的组合方式(输出为(fin×N)+fL)7 125PLL 电路与DDS的组合方式7126PLL13PLL 频率合成器的信号纯正度9 理想频率合成器的输出频谱(1根谱线)9131132 振幅调制的噪声(AM噪声)10 频率调制的噪声(FM噪声)12133 噪声的影响14134FM 的其他应用1614PLL 数字数据恢复为时钟的情况16141【专栏】dBc18 频率电压转换电路(FM解调电路)19142 电动机的转速控制电路19143【专栏】PLL电路的发明者Bellescize20附录APLL电路中负反馈的应用21 电路与运算放大器电路的异同21A1PLL 放大电路中学习的负反馈方式与特性23A2第2章PLL电路的传输特性31(PLL电路的特性由环路滤波器决定) 电路传输特性的理解3121PLL211PLL 电路各部分的传输特性31 简单例题(时钟的50倍频电路)33212 传输特性的求法(除环路滤波器特性以外)35213【专栏】仿真使用SPICE非常方便36 使用的环路滤波器的特性与PLL电路的传输特性37214 PLL电路中施加负反馈的效果39215 环路滤波器设计的基础知识4122 低通滤波器的特性41221RC 具有阶跃特性的RC低通滤波器43222 多级RC滤波器中增益与相位之间关系44223 普通的RC低通滤波器(使用滞后滤波器时环路特性不稳定)46 224 使PLL特性稳定的滞后超前滤波器47225第3章PLL电路中环路滤波器的设计方法51(无源/有源环路滤波器的设计实例与验证) 无源环路滤波器的设计5131 滞后超前滤波器的伯德图51311312PLL 电路与滞后超前滤波器组合的特性53 分频系数的改变情况56313 根据规格化曲线图求出环路滤波器的常数(参照附录B)57 3143210 ~100kHz PLL频率合成器中环路滤波器的设计59 作为实验用频率合成器的概况59321 频率合成器传输特性的求法322(除环路滤波器以外)61 时间常数小、M=-10dB、相位裕量为60°的设计61323324 时间常数中等、M=-20dB、相位裕量为50°的设计64 时间常数大、M=-30dB、相位裕量为50°的设计66325 试做的频率合成器的输出波形68326 试做的频率合成器的输出频谱70327 锁相速度72328 有源环路滤波器7533331 有源环路滤波器75 次有源环路滤波器的伯德图753322 次有源环路滤波器773333 有源环路滤波器的噪声79334 根据规格化曲线图求出有源环路滤波器常数的方法80 335 ~50MHz PLL频率合成器中环路滤波器的设计80 3425 实际电路中设计的有源环路滤波器80341 使用规格化曲线图求出环路滤波器的常数81342 时间常数小、M=0dB、相位裕量为50°的设计85343 时间常数中等、M=-10dB、相位裕量为34450°的设计86 时间常数大、M=-20dB、相位裕量为50°的设计88 345 试做的频率合成器的输出波形89346 试做的频率合成器的输出频谱90347 锁相速度92348 锁相速度的仿真94349【专栏】用于测量频率变化形式的调制磁畴分析仪97 相位裕量不同时PLL电路的特性9735 用作实验的50倍频电路98351 环路滤波器的设计99352 相位裕量为40°的设计99353354 相位裕量为50°的设计100 相位裕量为60°的设计100355356 频率特性的仿真101 输出波形的频谱103357 锁相速度104358 电路最适用的相位裕量(40°~50°)105359PLL第4章4046与各种鉴相器109(PLL电路中使用的重要器件的基础知识) 的重要器件404610941PLL411PLL 的入门器件109 的三种类型1104124046 片内三种鉴相器11041374HC40464144046 片内VCO的特性113 鉴相器的工作要点11542 模拟鉴相器115421 数字鉴相器118422 相位频率型鉴相器120423 中PC2型鉴相器1234244046 死区124425 电流输出型鉴相器126426 高速鉴相器AD 9901127427第5章电压控制振荡器VCO的电路131(VCO要求的特性及各种振荡电路方式) 要求的性能13151VCO 的概况131511VCO 频率可变范围133512 频率控制的线性133513 输出噪声133514 输出波形的失真134515 电源电压变化时的稳定度134516 环境温度变化时的稳定度134517 外界磁场与振动的影响135518 由弛张振荡器构成的VCO13552 函数发生器的基本工作原理135521 由函数发生器构成的VCO138522 函数发生器IC MAX038的应用139523 反馈振荡器14253 反馈振荡器的基本工作原理142531 反馈振荡器振荡稳定的方法142532 由RC构成的反馈振荡器143533 状态可变VCO147534 高频用LC振荡电路及其在VCO中的应用15154 基本的哈脱莱/科耳皮兹振荡电路151541 科耳皮兹的改进型克拉普振荡电路152542 反耦合振荡电路153543 由LC振荡器构成VCO时采用的变容二极管154 544545 市售的LC振荡式VCO电路157 其他的VCO电路15855 由振子构成的反馈振荡器158551 延迟振荡器162552第6章可编程分频器的种类与工作原理163(构成PLL频率合成器的数字电路) 可编程分频器的基本器件(减计数器)1636161174HC19116361274HC40102/40103164613TC919816562 前置频率倍减器168 前置频率倍减器IC168621 脉冲吞没(Pulse Swallow)方式170622 分数(Fractional)-N方式171623 用LSI17263PLL 专用LSI的构成172631PLL632ADF4110/4111/4112/4113173第7章PLL电路的测试与评价方法177(无源/有源环路滤波器的环路增益) 负反馈电路中环路增益的测试17771 难以测试的环路增益177711 施加负反馈时原环路增益的测试178712 负反馈环路测试的仿真180713714 实际注入的信号181 使用频率响应分析仪的测试方法18372 负反馈环路特性的测试183721722FRA 与FFT分析仪的不同之处185 与网络分析仪的不同之处185723FRA 电路中环路增益的测试18673PLL 使用无源环路滤波器的PLL186731 使用有源环路滤波器的PLL188732第8章PLL特性改善技术191(信号纯正度与锁相速度的提高技术) 优质的电源19181 使用CMOS反相器电路进行的实验191811 使用晶体振荡电路进行的实验193812 串联稳压器噪声特性的比较196813 控制电压特性的改善20082VCO 内VCO线性的改善200821CD74HC4046 片内VCO的频率变化范围的扩大204822CD74HC4046 与鉴相器之间的干扰20683VCO 中VCO与鉴相器同在的情况20683174HC4046832 用1个74HC4046进行的实验207 使用2个74HC4046进行的实验(VCO和鉴相器在不同的封装中)209 83384 鉴相器的死区210 用74HC4046进行死区影响的实验211841 与巴厘枚嘎模块VCO的组合使用213842PC28434046 中PC1与巴厘枚嘎模块VCO的组合使用217 与巴厘枚嘎模块VCO的组合使用220 84474HCT9046 锁相速度的改善22185 用二极管切换环路滤波器常数的方法222851 用模拟开关切换环路滤波器常数的方法224852 转换器进行预置电压相加的方法226 用D A853第9章实用的PLL频率合成器的设计与制作229(环路滤波器的详细设计与实测特性) 使用74HC4046的时钟频率合成器22991 替代1Hz~10MHz晶体的频率合成器229911 全部使用CMOS IC构成的频率合成器230912 环路滤波器的设计233913 输出波形235914 频谱235915 锁相速度238916 使用TLC2933构成的脉冲频率合成器23992 系列的概况239921TLC29xx 时钟频率合成器电路239922 环路滤波器的设计241923 输出波形频谱的测试243924 频率合成器24593HF 频率合成器电路245931HF 2环路滤波器常数的计算24893 频谱250933 锁相速度252934 频率基准信号用PLL2559440MHz 频率基准信号用PLL电路25594140MHz 环路滤波器的设计258942 输出波形260943 低失真的低频PLL电路26195951 低失真的低频PLL电路261 环路滤波器的设计264952 输出波形的合成267953附录B环路滤波器设计用规格化曲线图270附图:各公司4046的振荡频率控制电压特性270参考文献282。

锁相环电路设计PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

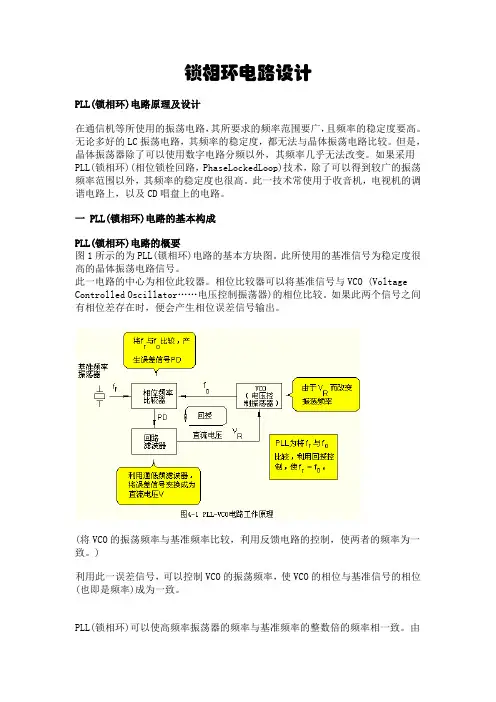

一 PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

如果有相位差存在时,便会产生正或负的脉波输出。

锁相环的工作原理

锁相环(Phase-Locked Loop,简称PLL)是一种用于生成稳定的与参考信号相位相同的输出信号的电子电路。

它的工作原理主要包括三个部分:相位比较器、低通滤波器和控制电压发生器。

1. 相位比较器:相位比较器将参考信号和输出信号进行相位比较,产生一个误差信号。

这个误差信号反映了输出相位和参考相位之间的差异。

2. 低通滤波器:误差信号经过低通滤波器进行滤波处理,去除高频噪声,得到一个平滑的控制信号。

这个控制信号的幅度表示了相位差的大小,而它的符号表示了相位差的正负方向。

3. 控制电压发生器:控制电压发生器根据滤波后的控制信号来调节输出信号的频率和相位,使得输出信号与参考信号保持同步。

控制电压发生器一般会产生一个与相位差成正比的反馈控制电压,通过改变振荡器或频率合成器的控制电压来调整输出信号的频率,使其与参考信号保持同步。

通过不断的相位比较、滤波和控制电压发生器的调节,锁相环能够使输出信号的频率和相位与参考信号保持一致。

这种稳定的相位锁定使得锁相环在很多应用中起到了重要的作用,例如时钟信号同步、频率合成、调制解调等。

认识有理数教学反思

《认识有理数教学反思》

在学习有理数的这段时间里,我感觉自己就像在数学的海洋里遨游,有时风平浪静,有时却波涛汹涌。

一开始,老师在黑板上写下那些数字,正数、负数、零,我眼睛都看直啦!心想:“这都是些啥呀?”特别是负数,那小小的负号,就像一个调皮的小精灵,总是让我迷糊。

记得有一次课堂上,老师问:“同学们,负数表示的意义你们懂了吗?”我心里直打鼓,不敢吭声。

旁边的同桌却自信满满地说:“老师,我懂!负数就是比零还小的数嘛!”老师笑着点头,我心里那个羡慕呀,反问自己:“我咋就没这么快明白呢?”

后来做练习题的时候,那一道道题目就像一个个小怪兽,张牙舞爪地等着我去打败它们。

有时候我能一下子就把它们解决掉,心里那叫一个美,就好像在炎热的夏天吃到了最爱的冰淇淋;可有时候,我却被它们难住了,抓耳挠腮,急得像热锅上的蚂蚁,嘴里嘟囔着:“这题咋这么难啊!”

小组讨论的时候可热闹啦!大家七嘴八舌地说着自己的想法。

“哎呀,这道题我觉得应该这样做!”“不对不对,你那样做错啦!”“那到底该咋办呀?”我们争得面红耳赤,可最后在大家的共同努力下,难题还是被我们攻克了,那种成就感,简直没法形容!

经过这段时间的学习,我发现有理数其实也没那么可怕。

它们就像我的小伙伴,虽然有时候会调皮捣蛋,但只要我用心去了解它们,就能和它们友好相处。

我觉得学习有理数就像爬山,一开始觉得山好高好难爬,但是只要一步一个脚印,坚持往上走,总会到达山顶,看到美丽的风景。

所以呀,遇到困难别害怕,勇敢面对,总会找到解决办法的!。

pll 原理

PLL(Phase Locked Loop)是一种用于在电路中锁相的重要技术。

它由相位比较器、环形混频器、低通滤波器和振荡器组成,用于将输入信号的相位锁定到参考信号的相位。

PLL的原理基于负反馈控制,其中相位比较器用于测量输入信号与参考信号之间的相位差,并输出相关的误差信号。

环形混频器将参考信号和振荡器输出的信号相乘,得到混频后的信号,并将其送入低通滤波器进行滤波处理。

滤波之后的信号作为控制信号,通过调整振荡器的频率和相位来实现与参考信号的相位同步。

PLL主要用于时钟恢复、频率合成、调制解调等应用中。

在时钟恢复方面,PLL可以用于将抖动或失真的时钟信号锁定到参考时钟的相位,使得时钟信号更加稳定和精确。

在频率合成方面,PLL可以根据参考频率和倍频系数生成所需的输出频率。

在调制解调方面,PLL可以通过将调制信号与参考信号进行相乘和滤波,实现解调出原始信号。

总而言之,PLL通过负反馈控制的方式,将输入信号的相位锁定到参考信号的相位,实现了信号的同步和固定相位关系。

它在各种电子设备和通信系统中都得到了广泛的应用。

锁相环的组成和工作原理#11.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

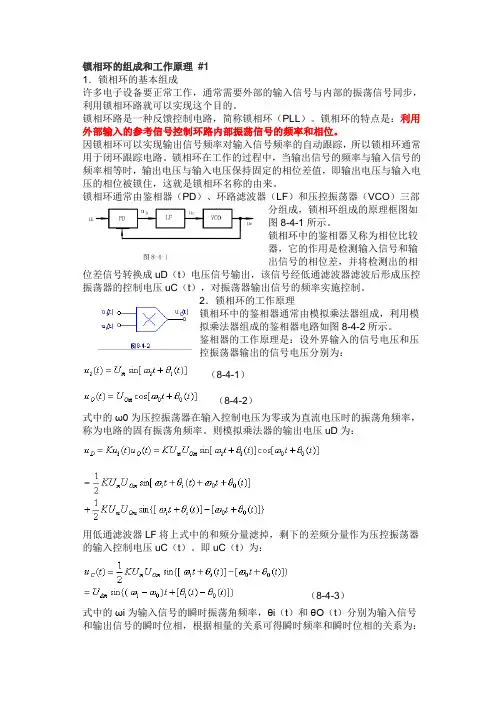

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压uD为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。

即uC(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。

dll锁相环原理DLL(数字锁相环)是一种数字电路,用于锁定输入信号与一定频率的参考时钟信号相位。

它是一种数字PLL(锁相环)的特殊情况,可以广泛应用于数字通信、音频处理以及高速数字系统中。

DLL锁相环的工作原理可以归纳为以下几个步骤:1.将参考时钟信号分频:参考时钟信号通过一系列的分频器,被分成与输入信号相同的频率。

2.产生相位差信号:将分频后的参考时钟信号与输入信号比较,产生一个相位差信号。

3.通过数字滤波器进行滤波:将相位差信号通过数字滤波器进行滤波以去除高频噪声。

4.控制输出时钟信号:根据滤波后的相位差信号的大小和正负,控制VCO(电压控制振荡器)输出的时钟信号的相位和频率。

此时输出的时钟信号与输入信号的相位差被锁定在一个可接受的范围内,从而保证了系统的信号同步性和稳定性。

DLL锁相环有许多优点,如下所述:1.响应速度快:使用数字电路的方式,锁相环的响应速度非常快。

因此,它适用于要求精度高且信号变化频繁的应用。

2.实现简单:数字锁相环相对于传统的模拟锁相环,其电路实现更加简单,而且不需要精密的模拟电路设计。

3.稳定性强:由于数字滤波器可以进行高精度的滤波,因此数字锁相环的稳定性也比模拟锁相环更高。

这使得它适用于对相位稳定性要求高的应用场景,如通信系统中的时钟恢复等。

4.适应性强:数字锁相环可以适应不同频率和相位差的输入信号,因此其应用范围非常广泛。

在音频处理中,它可以被用于对频率和相位进行校正,确保各种波形信号的正确性。

在数字通信中,它可以被用于时钟恢复、卫星通信、调制解调器等领域。

总之,DLL锁相环是一种对精度和性能有高要求的应用具有重要意义和应用价值的技术,它在各个领域有着广泛应用,推动着数字化电子技术的飞速发展。

pll的参数PLL(Phase Locked Loop)是一种广泛应用于通信和控制系统中的重要电路,它可以实现信号的频率和相位同步。

本文将从PLL的基本原理、参数设置、工作过程和应用场景等方面进行详细介绍。

一、PLL的基本原理PLL是由相位比较器、低通滤波器、VCO(Voltage Controlled Oscillator)和分频器等组成的反馈控制系统。

其基本原理是通过不断调节VCO的频率,使其输出信号与输入信号的频率和相位保持一致。

相位比较器会将输入信号与输出信号进行相位比较,产生一个误差信号。

低通滤波器会滤除误差信号中的高频成分,得到一个稳定的控制电压,用于调节VCO的频率。

通过这种方式,PLL可以实现输入信号与VCO输出信号的频率和相位同步。

二、PLL的参数设置在设计PLL时,需要设置一些重要的参数,以满足具体的应用需求。

其中,常见的参数包括参考频率(Reference Frequency)、倍频因子(Multiplication Factor)、环带宽(Loop Bandwidth)和锁定时间(Lock Time)等。

参考频率是输入信号的频率,倍频因子决定了VCO输出信号的频率与输入信号频率的比值,环带宽影响PLL 的动态响应速度,锁定时间则是PLL从失锁状态到锁定状态所需的时间。

三、PLL的工作过程PLL的工作过程可以分为锁定状态和失锁状态两种情况。

在失锁状态下,输入信号的频率和相位与VCO输出信号不一致,相位比较器会产生一个误差信号,经过低通滤波器调节VCO的频率,直到误差信号趋近于零。

当误差信号趋近于零时,PLL进入锁定状态,此时输入信号和VCO输出信号的频率和相位保持一致。

四、PLL的应用场景PLL在通信和控制系统中有着广泛的应用。

在通信系统中,PLL常用于频率合成器、时钟恢复和调制解调器等模块中,用于实现信号的精确同步和调节。

在控制系统中,PLL可以用于时钟同步、频率捕获和相位同步等场景,提高系统的稳定性和可靠性。

pll工作原理PLL,全称为Phase-Locked Loop。

它是一种电子电路,具有频率合成和时钟重构的功能,被广泛应用于通信、控制、测量和工业等领域。

PLL的基本原理是将一个输入信号与一个本地信号进行比较,将比较结果反馈给控制器,以调整本地信号的频率和相位,使其与输入信号保持同步。

下面我们来分步骤阐述PLL的工作原理。

第一步,当输入信号f_in进入PLL时,首先经过一个分频器,将其频率降低到与一个参考信号f_ref相同的频率。

这个参考信号可以是一个参考振荡器产生的稳定信号,也可以是来自于其他源的稳定信号。

分频比为N,即将f_in分频N倍,得到f_p = f_in/N,这样使输入信号与参考信号在频率上保持一致,方便进行比较和调整。

第二步,将分频后的f_p信号与参考信号f_ref进行比较,得到一个误差电压e(t)。

这个误差电压代表了f_p与f_ref之间的相位误差,如果f_p和f_ref相位相同,那么误差电压为0;如果它们相位不同,那么误差电压将是一个正负交替的信号。

第三步,将误差电压e(t)反馈给控制器,其中最常用的控制器是一个环路滤波器(loop filter)。

环路滤波器是一个积分器,它将误差电压e(t)进行积分,并将积分结果作为输出信号V_c(t)。

这个输出信号将被发送给一个控制电压控制振荡器(VCO),作为其输入信号。

第四步,控制器的输出信号(V_c(t))被加到VCO的控制电压输入端,控制VCO的频率。

这样在VCO产生的本地信号f_out的频率将被调整,以减小f_p与f_ref之间的相位误差。

反馈环路会不断地进行调整,直到f_p与f_ref之间的相位差为0,也就是说f_out与f_in频率相同且相位相同。

这就完成了一个PLL的工作过程。

总的来说,PLL是一种非常重要的电子电路,它可以实现高精度的频率合成和时钟重构,可以提高通信系统的稳定性,增强信号质量,扩展数据传输能力等。

PLL电路的基本工作原理PLL(Phase-Locked Loop)电路是一种用于鉴频、频率合成和时钟提取等应用的电路。

其基本组成部分包括相锁环比较器、低通滤波器、VCO (Voltage Controlled Oscillator)和反馈电路。

PLL电路能够通过对输入信号进行锁定,保持输出频率与输入信号频率之间的固定差值。

PLL的基本工作原理可以通过以下步骤描述:1.稳定状态:在PLL电路的初始状态下,VCO的输出频率被设定为一个初始值。

锁相环比较器将输入信号和VCO的输出信号进行比较,然后将比较结果送入低通滤波器。

2.锁定过程:当输入信号的频率略有变化时,比较器的输出信号会发生变化。

低通滤波器通过滤除比较器输出的高频成分,只保留其直流分量,然后将其送入VCO的控制端。

通过控制输入给VCO的直流电压,VCO的输出频率可以随之调整。

3.锁定稳态:经过一段时间后,VCO的输出频率将与输入信号频率之间保持一个固定的差值,这个差值称为相位差。

低通滤波器在此过程中起到平滑响应的作用,保证VCO的控制电压逐渐稳定。

总结起来,PLL的基本工作原理可以概括为通过不断比较输入信号和VCO输出信号的相位差,然后通过调整VCO的输入电压来实现相位差的稳定。

通过反馈电路和低通滤波器的作用,使得VCO的输出频率与输入信号的频率之间相差一个固定的相位差。

1.鉴频功能:PLL电路可以对输入信号进行鉴频,即可以提取输入信号的频率信息。

通过测量输入信号和VCO输出信号的相位差,可以得到输入信号的频率。

2.频率合成:通过改变VCO的控制电压,可以实现VCO输出频率是输入信号频率的整数倍。

这可以用于产生高稳定性的时钟信号或者合成特定的频率信号。

3.时钟提取:PLL电路也可以用于提取时钟信号。

输入信号是待提取的信号,而VCO的输出频率是预定的时钟频率。

通过PLL电路的控制,VCO的输出信号能够与输入信号同步,从而实现时钟信号的提取。

数字移相器的工作原理

数字移相器是一种基于相位控制的电路,在射频和微波电路中广泛应用。

它的主要作用是移动电路中的信号相位,实现相位偏移,相移调节和

频率合成等功能。

数字移相器通常由相位锁定环(PLL)和电子开关(ESW)构成。

数字移相器的工作原理是通过电子开关控制射频信号经过不同的时延

路径,从而改变信号的相位。

当输入的信号经过锁相环(PLL)时,PLL

会将输入信号的频率锁定到一个精准的参考频率上。

然后,电子开关根据

外部控制信号选择一个时延路径,将信号从同一时刻延迟到不同的时刻,

并控制相位的变化。

如果相移器希望按照一定的步进调整相位,可以通过ESW控制第二级信号,机械式的开关是ESW的代表形式,另一种电容向地

分支的芯片也叫做ESW。

一般来说,数字移相器可以实现相位变化步进的

精度可以达到几度甚至更小,且可靠性高和频率节约。

应用方面,数字移相器被广泛应用于相位调制、相位移位键控(PSK)通信、频率合成、成像雷达、数字信号处理等领域。

在通信系统中,它通

常用于频率和相位调制技术,以获得更高的信号传输速率和更好的信号质量。

在雷达中,数字移相器通常用于成像雷达中,以获得更好的成像分辨

率和空间分辨率。

总的来说,数字移相器是一种功能强大的电路,可以实现相位调节、

相位偏移、频率合成和成像雷达等应用。

它的优点是精度高、可靠性好和

使用方便,因此在许多电子领域得到广泛应用。

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。

PLL电路的基本工作原理

1.1PLL电路的三大组成各部分

Phase lock loop锁相环电路适用于生成与输入信号同步的新的信号电路。

PLL电路基本上由三大部分组成:

1)鉴相器(phase detector)

鉴相器用于检测出两个输入信号的相位差。

鉴相器的工作方式多种多样,大部分是数字方式的,也有模拟方式工作的鉴相器,主要方式检测出两个信号上升沿的差。

2)环路滤波器(loop filter)

环路滤波器是将鉴相器输出的含有波纹的直流信号平均化,将次变换为交流成分较少的低通滤波器。

环路滤波器滤除了滤除波纹的功能外,还有一个重要的功能,即决定稳定进行PLL环路控制的传输特性。

稳定的PLL电路的环路滤波特性是非常重要的。

关系到整个系统的性能。

3)压控振荡器(voltage controlled osillator)

压控振荡器就是用输入的直流信号控制振荡频率,它是一种可变频振荡器。

1.1.2PLL的应用与频率合成器

在图中可以看到,将输入信号与VCO输出信号进行比较,控制两个信号使其保持相位同步。

两个输入信号同相位,当然也可以对频率进行同样的控制,这样一来就可以是VCo输出的振荡频率能够跟踪输入信号的频率了。

这时,VcO的振荡频率变化由环路滤波器的时间常数决定。

时间常数越大,频率的变化越慢;时间常数越小,频率变化越快。

这样,VCo的振荡频率同步跟踪输入信号的频率。

在图中若跟踪速度设计得当,由VCO可得到接受信号或与电磁波同步的信号。

例如,接受电磁波信号中叠加有噪声时,VCO立即停止接收该信号,不收噪声影响,VCO与接收信号平品均频率稳定同步,并持续振荡。

另外,在图中,若VCO输出与鉴相器输入之间接入分频器,则输入频率与VCO输出频率的分频频率同步。

也就是说,VCO的振荡频率对输入信号的分频频率进行控制。

因此,若在PLL输入信号中加上由晶振等产生的稳定频率信号,并对分频器的频率进行切换,则由VCO的输出得到与输入频率同样精度的分频信号。

这就是PLL方式频率和成器的原理。

1.2.1PLL电路以及频率合成器的构成

无论是工业还是民用,PLL电路的应用范围都极其广泛

1.2.2输出为输入N倍频的方法

PLL电路是将输入波形与VCo震荡波形的相位进行比较,使其输入频率与VCO振荡频率同步的电路。

VCO输出经过分频器后的信号与输入波形的相位进行比较,输入频率与分频后的频率为相同的频率,即VCO的振荡频率与分频后的频率同步。

具有由外部的任意的整数值部设定分频功能的分频器称为可编程分频器(programabledevider)

1.2.3输出为输入N/M倍频的方法

由图所示,输出频率设定分辨率等于相位比较频率。

因此,PLL电路的输出频率精度由输入信号的精度决定。

为此,对于频率的合成器等,一般由晶振产生输入信号。

然而,廉价的晶振振荡频率的稳定度往往不尽如人意。

为此,想要得到更高的设定分辨率时,采用在回路的鉴相器前增加一个1/M的分频器进行再分频是一个理想的办法。

此外,还可以利用输出部分接入分频电路的方法在图中构成的PLL电路中,为了拓宽频率合成器的输出频率范围,在宽范围内取分频系数,相应的VCO振荡频率也要在带宽的范围内改变。

然而正如前文说的那样,分频的系数范围变宽,作为PLL电路的传输函数也要随着变化,VCO很难输出很高纯度的信号。

另外,可变VCO的振荡频率范围也是有限的。

一般来说,振荡频率的范围宽,则VCO 输出信号纯度的纯正度也随之降低。

输出波形方波形时,在VCO输出部分接入分频器,可以拓宽输出频率范围。

例如,VCo 正当频率范围即使为1~10MHZ,若输出分频器的分频系数N设定为10,100,1000,……..则也可以得到价低的频率。

1.2.4输出为输入的NxM倍频的方法(增设前置频率衰减器)

为了实现数字式切换改变PLL电路的输出频率,可使用的变成分频器,但要自由设定分频系数,分频内部构成变得很复杂,高速响应也难以实现。

通用可编程分频器的上限频率为10MHZ左右。

分频系数固定,而工作的频率扩展到GHZ的电路称为前置频率倍减器,这是如果在vco 与可编程分频器之间接入被称为前置频率倍减器的1/M分频器的方法,频率合成器的频率也可能达到GHZ数量级。

但是,这种评估方法牺牲了前置频率倍减器所有分频系数设定的分辨率。

为此,可采用称为脉冲吞没式的计数器。

1.2.5PLL电路与DDS的组合方式

若提高PLL电路的设定频率,则分频系数变大,相位比较频率变低。

为此,改变设定值时,PLL电路的响应速度变慢。

另外,环路增益随着分频率的增高而下降,输出波形的纯正度变坏。

随着LSI技术的发展,直接数字频率和成器的DDS构成信号发生器已经实用化。

DDS构成的正弦波发生器,它是由加法器与锁存器构成的累加器组成。

每当外来一个时钟脉冲时,则积累计算设定。

经常得到速度与设定值成比例的数字数据,这种数据可作为预先写入正弦波数据ROM的地址加入到电路中。

这样一来就可以从ROM中读取到正弦波数据。

1.3锁相环频率合成器的信号纯度

1.3.1PLL频率合成器的输出频谱

在很多高精度的电子系统中,一个稳定的频率合成器是多么的重要,我的课题也正是由此出发点进行的研究,即运用本科所能驾驭的相对简单的手段,使用先期硬件仿真,而后通用板制作,加之以少量的单片机程控手段来达到一个尽量高精度的目的,更具体来说所谓“高精度信号”,它是一种单一频率的纯净的信号。

若用扫频仪进行观测,观测到的将是一根谱线。

但是令人失望的是,在实际操作中,我们的系统由于各种自扰和工艺的问题会产生许多其他频率的分量,比如(VCO)的输出端便会多多少少含有有些杂波成分。

而这些杂波又有些不同,高次谐波失真是由整数倍频率成分组成,一些不需要的频率成分一般叫做寄生成分。

对于PLL电路,由于相位比较频率成分的泄露导致了整数倍的比较频率偏移振荡频率的高低两侧,存在一些不需要的频率成分。

这其中,又分为振幅调制(AM)的噪声和频率调制(FM)的噪声。

这些信号频率的整数倍波形是多余的波形,也就是高次谐波。

这种谐波可以轻松利用滤波器来去除,所以相对于与载波频率相近的分量来说更容易去除。