DDR3 SDRAM物理层中ADDLL的设计与实现

- 格式:pdf

- 大小:1.44 MB

- 文档页数:6

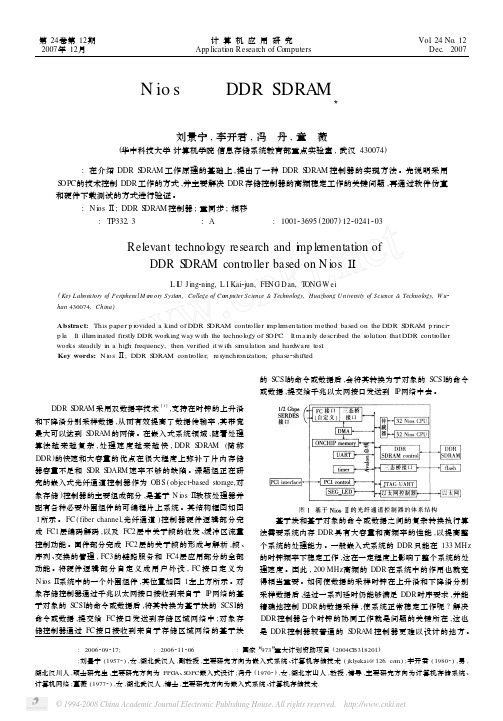

现代电子技术Modern Electronics TechniqueFeb.2022Vol.45No.42022年2月15日第45卷第4期0引言以太网数据要通过E1线路传输就必须对以太网净荷数据进行帧封装,才能从E1线路上恢复出以太网数据帧,完成以太网数据的交换。

使用HDLC 协议进行以太网数据的二次封装,以太网数据在进行HDLC 协议封装的传输过程中,不同数据链路进行数据交互时会出现亚稳态和数据吞吐量差异的问题。

由于已有设计在以太网模块内部完成了跨时钟域的处理,因此本文提出的电路旨在解决跨时钟域数据通信时的吞吐量差异问题。

这个问题的解决通常需要一个存储模块进行缓存,而SDRAM 由于具有较高的读写速率和精度、存储容量大等优点[1⁃4],常用于数据缓存模块中,所以本文设计在利用SDRAM [5]基本的缓存特性基础上,提出一种SDRAM 控制器的新设计思路,运用模块化的设计方法,即双缓存模块IN_FIFO 和OUT_FIFO 的设计,将8bit 的输入数DOI :10.16652/j.issn.1004⁃373x.2022.04.007引用格式:黄海生,党成,李鑫,等.一种SDRAM 控制器的设计电路[J].现代电子技术,2022,45(4):35⁃38.一种SDRAM 控制器的设计电路黄海生,党成,李鑫,叶小艳(西安邮电大学电子工程学院,陕西西安710121)摘要:针对以太网映射器芯片中以太网链路和HDLC 链路之间存在不同速率数据链路通信的相互转换问题,文中提出一种SDRAM 控制器的设计方案并采用Verilog HDL 来实现。

在该设计电路中,仲裁器处理以太网链路和HDLC 链路与SDRAM 之间的数据传送请求,以太网模块将接收到的数据写入IN_FIFO 缓冲区,仲裁器负责将IN_FIFO 中的数据导入SDRAM 。

在约定信息速率(CIR )控制器的作用下,仲裁器将SDRAM 中的数据写入OUT_FIFO 缓冲区,HDLC 模块将OUT_FIFO 中的数据读出。

DDR3-SDRAM控制器设计及FPGA实现李元兵;姚远程;秦明伟【摘要】针对自适应接收机中高速A/D采样数据对高带宽和大容量的需求,提出一种DDR3控制器设计方案.采用在MIG IP核的基础上添加用户接口控制程序的设计方法,利用ZC706评估板实现了DDR3的读写控制.设计方案具有较高的可移植性和简单的用户接口,可以灵活地应用到不同的工程中.仿真和板级测试表明,DDR3可在800 MHz的接口频率工作,传输速度可达1 600 MT/s,验证了系统的可行性和正确性,其将有助于解决海量数据的高速缓存问题.【期刊名称】《自动化仪表》【年(卷),期】2016(037)008【总页数】4页(P5-7,12)【关键词】存储器;控制器;FPGA;高带宽;大容量;用户接口;数据模块;模数转换【作者】李元兵;姚远程;秦明伟【作者单位】西南科技大学信息工程学院,四川绵阳621010;特殊环境机器人技术四川省重点实验室,四川绵阳 621010;西南科技大学信息工程学院,四川绵阳621010;特殊环境机器人技术四川省重点实验室,四川绵阳 621010;西南科技大学信息工程学院,四川绵阳621010;特殊环境机器人技术四川省重点实验室,四川绵阳621010【正文语种】中文【中图分类】TH7;TP332当前,在诸多通信芯片和系统的研发中,经常用到各种大容量、高速读写存储器件。

同步动态随机存储器(synchronous dynamic random access memory,SDRAM)以其价格低、速度快、容量大等特点,广受开发者的青睐[1]。

其中,DDR2和DDR3发展成熟、应用广泛。

DDR3在DDR2的基础上有了进一步的发展和改进,因此更具优势,已成为工程人员的首选方案。

由于DDR3不能直接识别处理器的访问请求[2],所以有必要设计一个DDR3控制器,以控制DDR3的读写。

基于ZC706评估板,针对高速数据通过DDR3缓存的应用背景,利用Xilinx官方的MIG IP核,实现了DDR3控制器的设计,并在板上完成了验证。

基于FPGA的DDR3 SDRAM控制器设计与实现方法丁培培;郑列;李宏【摘要】DDR3 SDRAM作为新一代存储单元,在容量、速率和兼容性方面有很大提高,广泛应用在图像处理和高速数据采集系统中.本文通过研读DDR3 SDRAM的JEDEC标准,简要介绍DDR3 SDRAM的基本结构和工作原理,结合Xilinx公司提供的MIG软件开发环境,采用高传输速率、高可靠性、低成本、低功耗的Kintex-7系列FPGA实现DDR3 SDRAM控制器的设计[1],通过Kintex-7开发套件进行联合仿真,性能达到预期设计目标,并在遥感图像压缩中有实际的应用.【期刊名称】《信息记录材料》【年(卷),期】2018(019)005【总页数】3页(P64-66)【关键词】FPGA;控制接口;DDR3SDRAM;数据传输【作者】丁培培;郑列;李宏【作者单位】西安石油大学<电子工程学院> 陕西西安 710065;西安石油大学<电子工程学院> 陕西西安 710065;西安石油大学<电子工程学院> 陕西西安710065【正文语种】中文【中图分类】TP3321 引言随着现代科技的高速发展,在雷达、无线通信、图像处理等领域需要高速传输大量的数据,高速数据采集作为系统中比较关键的部分,对数据处理的速度、稳定性、实时性以及功耗提出了更高的要求[1]。

从现有的存储器来看,当DDR2内核的工作频率达到200MHz时,数据传输速率将提高到极限值800MHz[2]且不会再有显著提升。

由此可见,一般的存储器已不能满足目前高速度、高宽带、大容量的数据存储和访问,并制约存储器的发展和应用。

DDR3作为一种双倍数据速率的同步动态随机存储器,相比DDR2的不足,DDR3具有高带宽、高可靠性、低功耗和低成本的特点,因此成为高速数据采集系统的首选方案[3]。

Xilinx公司推出新一代低成本Kintex-7系列FPGA与Virtex-6系列FPGA相比[4],其功耗和成本都降低了50%,而性价比却提高了2倍。

基于FPGA的DDR3SDRAM控制器设计及实现DDR3SDRAM是一种高速动态随机存储器,通常用于提供高性能和大容量的内存解决方案。

在本文中,将讨论基于FPGA的DDR3SDRAM控制器的设计和实现,以及其在系统中的重要性。

DDR3SDRAM控制器的设计和实现是一个复杂的任务,它涉及到对DDR3协议进行理解和实现,以及对FPGA硬件资源的有效利用。

首先,需要对DDR3协议进行详细研究。

DDR3协议定义了数据的传输和处理方式,包括时钟信号的生成和数据传输的时序管理。

DDR3协议具有高度的精确性和复杂性,因此在设计控制器时需要仔细考虑各种情况和可能的延迟,并遵循协议的要求。

其次,需要合理利用FPGA硬件资源来实现DDR3SDRAM控制器。

FPGA 通常具有丰富的逻辑资源和存储资源,因此可以很好地满足DDR3控制器的要求。

控制器的核心部分是状态机,它负责生成和管理控制信号,以确保DDR3SDRAM能够正确进行读写操作。

此外,还需要一个缓存来缓存读取或写入的数据,以补偿DDR3的读取和写入延迟。

在设计和实现过程中,还需要考虑时序分析和时序优化。

时序分析是通过对信号时序进行建模和仿真,确定各个信号之间的延迟和关系。

时序优化是通过调整时序参数或重新设计电路来减小延迟,以提高性能和稳定性。

最后,需要进行验证和测试以确保DDR3SDRAM控制器的正确性和稳定性。

验证和测试可以通过模拟器、仿真器和实际硬件测试来进行。

验证和测试过程中需要考虑各种情况和使用场景,以确保控制器在各种情况下能够正常工作。

总结起来,基于FPGA的DDR3SDRAM控制器设计和实现是一个复杂而关键的任务。

它要求对DDR3协议有深入的理解,并合理利用FPGA硬件资源。

同时,还要进行时序分析和优化,并进行验证和测试以确保控制器的正确性和稳定性。

只有经过充分的设计和测试,才能保证DDR3SDRAM在系统中的正常工作。

图1 DDR3 SDRAM控制器的结构框图图2 大容量虚拟FIFO缓存的整体结构框图

和处理,FPGA内FIFO远不能满足性能上的要求。

这就使得将DDR3设计成大容量数据缓冲区成为工程中的必要需求。

然而由物理层模块通过物理引脚与片外DDR3 SDRAM直接进行

图3 写FIFO接口的FPGA内部逻辑实现图图4 读FIFO接口的FPGA内部逻

辑实现图

图5 DDR3 FIFO控制状态机图6 时钟模块的结构图

图7 时钟模块的FPGA内部逻辑实现图

据缓存,考虑到FPGA不仅处理速度高

本文测试所选芯片为Xilinx V6ISE14.6。

在该环境中创建支持DDR3满一行,则跳转到ddr3_ctrl _s1状态,同时将app_en 、app_wdf_wren 和DDR3写FIFO 接口的读使能置为无效;如果写入次图8 ChipScope信号抓取。

ddr3 电路设计

DDR3是一种双数据速率(Double Data Rate)的SDRAM(同步

动态随机存取存储器),它具有高速、高密度和低功耗的特点。

在

进行DDR3电路设计时,需要考虑以下几个方面:

1. 时序设计,DDR3内部时序非常严格,需要精确的时钟控制

和信号同步。

在电路设计中,需要确保时钟信号的准确性和稳定性,同时要考虑数据和控制信号的延迟和对齐。

2. 信号完整性,DDR3的高速传输需要考虑信号完整性,包括

信号的传输线路设计、阻抗匹配、信号串扰和噪声抑制等方面。

在

电路设计中需要合理布局PCB,减小信号传输路径的长度,采用差

分信号传输等方法来提高信号完整性。

3. 电源和接地设计,DDR3需要提供稳定的电源和接地,以确

保芯片的正常工作。

在电路设计中需要考虑电源线和接地线的布局

和连接方式,减小电源噪声和提高电源供电的稳定性。

4. 自校准和时序校准,DDR3内部具有自校准和时序校准的功能,可以校正时钟和数据信号的偏移和延迟。

在电路设计中需要考

虑这些校准功能的实现和控制。

5. 热管理,DDR3在高速运行时会产生较多的热量,需要考虑散热设计,包括散热片的设计和散热风扇等。

总之,DDR3电路设计需要全面考虑时序、信号完整性、电源和接地、自校准和时序校准、热管理等多个方面,以确保DDR3芯片的正常工作和高速稳定传输。

基于FPGA的DDR3SDRAM控制器设计及实现DDR3 SDRAM是一种主流的存储器,广泛应用于计算机和嵌入式系统中。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活性和可重构性。

本文将介绍基于FPGA的DDR3 SDRAM控制器的设计和实现。

DDR3SDRAM控制器的设计主要包括以下几个方面:时序控制、数据读写控制、自动预充电控制和错误检测与纠正。

时序控制是DDR3SDRAM控制器中最关键的部分之一、DDR3SDRAM需要按照特定的时序来进行读写操作。

时序控制模块需要根据DDR3SDRAM的时序要求生成相应的控制信号,包括时钟信号、时钟使能信号、写使能信号、读使能信号等。

数据读写控制是DDR3SDRAM控制器的另一个关键部分。

数据读写控制模块负责将数据从FPGA的内部总线传输到DDR3SDRAM中,或者将数据从DDR3SDRAM中传输到FPGA的内部总线中。

该模块需要处理数据的读写请求,并生成相应的控制信号,包括读写命令、地址信号、数据信号等。

自动预充电控制是DDR3SDRAM中一个重要的功能。

在进行读取或写入操作之前,DDR3SDRAM需要进行自动预充电操作,以确保正确的电荷状态。

自动预充电控制模块需要根据DDR3SDRAM的要求生成相应的预充电命令和控制信号。

错误检测与纠正是DDR3SDRAM控制器中的一个重要功能。

DDR3SDRAM中可能会发生各种错误,例如位翻转、干扰等。

错误检测与纠正模块需要对读取的数据进行校验,并根据校验结果进行错误纠正或报错处理。

在实现过程中,可以使用FPGA开发板进行验证和调试。

通过编写测试程序,可以模拟DDR3SDRAM的读写操作,并检查控制器的功能和性能。

总之,基于FPGA的DDR3SDRAM控制器设计和实现是一个复杂的任务,需要考虑多个方面的因素。

通过合理的设计和实现,可以实现高性能和可靠的DDR3SDRAM控制器,满足计算机和嵌入式系统的存储需求。