数模混合信号电路设计数字电路设计流程

- 格式:pptx

- 大小:1.50 MB

- 文档页数:76

数模混合电路设计流程马昭鑫 2012/5/23本文主要面向模拟电路设计者,讲解了从行为级代码形式的数字电路到数模混合版图之间的流程,默认模拟版图和数字电路的行为级代码、testbench已经完成。

阅读者需确定自己会编写Verilog或Spice格式的网表,熟悉Linux的文件操作,了解Spectre、Virtuoso、Calibre、Modelsim、Design Compiler(dc)、Astro等EDA工具的使用方法。

由于本人才疏学浅,经验不足,难免会在文中出现一些错误,恳请高手给予指正。

数模混合电路的仿真方法一般的设计流程中数字电路和模拟电路是分开进行设计的,但有些时候希望能将数字电路和模拟电路放在一起仿真来验证设计,这就需要用到混合电路的仿真方法。

在Cadence 工具中有专门用作混合电路仿真的仿真器spectreVerilog,其实现方法是首先将模拟模块与数字模块区分开并设置接口电平,然后在ADE中设置数字电路的测试代码,调用不同的仿真器分别对数字模块和模拟模块进行仿真,最后将结果汇总显示或输出。

下面将以一个简单实例的形式讲解混合电路的仿真方法。

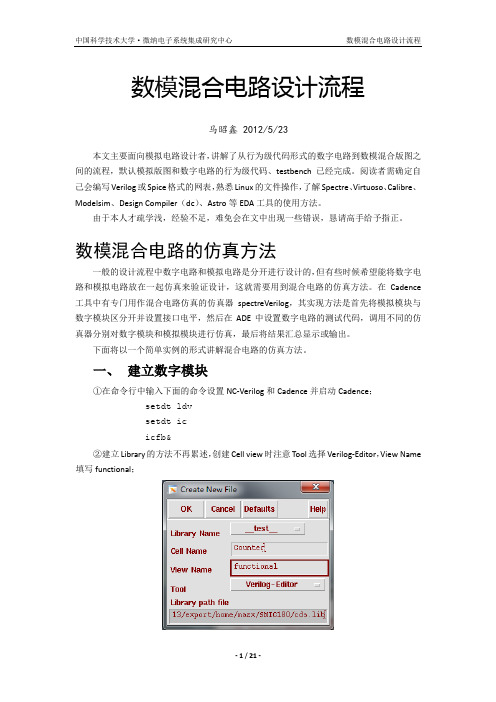

一、建立数字模块①在命令行中输入下面的命令设置NC-Verilog和Cadence并启动Cadence;setdt ldvsetdt icicfb&②建立Library的方法不再累述,创建Cell view时注意Tool选择Verilog-Editor,View Name 填写functional;③点击OK后会弹出有模块代码框架的vi窗口,将设计需要的代码输入或粘贴进去;④保存并关闭后如果没有错误会弹出创建Symbol View的询问对话框,确定后会进入Symbol编辑器,并自动生成了Symbol(注意在Cadence中总线用尖括号<>表示);⑤保存并关闭Symbol编辑器。

至此已经完成了数字模块的创建。

二、建立模拟模块模拟电路的创建方法无需赘述,这里搭建了一个输出频率为10MHz的环形振荡器。

ams数模混合仿真基本流程在模拟和混合信号(AMS)电路设计中,仿真是一个至关重要的环节,它有助于验证电路的功能、性能和可行性。

以下是一个基本的仿真流程,涵盖了从建立电路模型到导出电路版图的各个环节。

1. 建立电路模型在开始仿真之前,首先需要建立一个电路模型。

这个模型应该详细地描述电路的各个部分,包括模拟和数字部分,以及它们之间的交互。

可以使用各种电路仿真软件(如SPICE、PSPICE、Multisim等)提供的元件库来创建模型。

2. 设置仿真参数设置仿真参数是确保仿真结果准确性和可靠性的关键步骤。

这些参数包括仿真类型(直流、交流、瞬态等)、仿真时间、采样率、精度等。

此外,还需要为模拟和数字部分设置适当的参数。

3. 运行仿真在设置好仿真参数后,就可以运行仿真了。

仿真过程中,软件会根据所建立的模型和设置的参数,计算出电路在不同条件下的行为。

这个过程可能需要一些时间,具体取决于电路的复杂性和仿真参数的设置。

4. 分析仿真结果仿真结束后,需要对结果进行分析。

分析的内容可能包括波形图、眼图、频谱图等,以便了解电路的性能和功能。

如果仿真结果与预期不符,可能需要回到设计阶段进行修改。

5. 优化电路设计在分析仿真结果后,如果发现电路性能或功能存在问题,就需要进行优化设计。

优化过程可能涉及调整元件参数、改变电路结构、改进版图布局等。

通过不断迭代和优化,力求使电路性能达到最佳。

6. 验证设计可行在完成优化设计后,需要再次进行仿真验证,以确保改进后的设计是可行的。

这一步通常涉及到更全面的测试和验证,以确保设计的鲁棒性和可靠性。

7. 导出电路版图最后,如果一切顺利,就可以将设计的版图导出,以便进行后续的制程生产。

在导出版图之前,通常还需要进行一些物理验证和一致性检查,以确保版图的正确性和可制造性。

总的来说,数模混合仿真是设计和验证模拟和混合信号电路的重要手段。

通过遵循上述的基本流程,可以有效地进行电路设计和仿真,从而为后续的制程生产提供可靠的依据。

模拟电路混合信号设计混合信号设计是指将模拟信号和数字信号结合起来进行设计和处理的一种技术。

在现代电子系统中,混合信号电路已经成为智能手机、物联网设备、汽车电子和医疗设备等众多应用领域的关键技术。

本文将讨论混合信号设计的基本原理、常用技术和设计流程。

一、混合信号设计的基本原理混合信号设计的基本原理是将模拟信号和数字信号相互转换并进行处理。

模拟信号是连续变化的信号,如声音、光线等;数字信号是离散的信号,通过编码方式将模拟信号转化为二进制数据。

混合信号设计就是利用模拟电路和数字电路相结合的方式,对混合信号进行处理和控制。

二、混合信号设计的常用技术1. 模数转换技术:模数转换器(ADC)将模拟信号转换为数字信号。

常见的ADC技术包括逐次逼近法、逐次逼近逆法和积分法等。

2. 数模转换技术:数模转换器(DAC)将数字信号转换为模拟信号。

常见的DAC技术包括串行DAC、并行DAC和PWM技术等。

3. 混合信号滤波技术:对混合信号进行滤波处理,以去除噪声和干扰。

常用的滤波器包括低通滤波器、高通滤波器和带通滤波器等。

4. 时钟和定时技术:混合信号设计中需要精确的时钟信号和定时技术,以确保模拟信号和数字信号的同步和精度。

三、混合信号设计的流程1. 确定需求和规格:首先确定混合信号设计的需求和规格,包括系统的功能、性能、输入输出参数等。

2. 电路设计:根据需求和规格,进行混合信号电路的设计。

包括模拟电路和数字电路的设计,选择合适的模拟和数字器件。

3. 仿真和验证:利用模拟仿真和数字仿真工具对电路进行仿真和验证,以确保电路的功能和性能。

4. PCB设计和布局:根据电路设计,进行PCB设计和布局,确保信号的良好传输和电磁兼容性。

5. 组件选择和采购:选择合适的组件和器件,并进行采购。

6. 计算和优化:对电路进行计算和优化,以满足设计需求和规格。

7. 测试和调试:对设计的混合信号电路进行测试和调试,以验证电路的功能和性能。

数模混合仿真设计流程详解1.确定仿真对象与目标:首先确定要仿真的对象是什么,比如电路、通信系统等。

然后确定仿真的目标,比如系统的性能评估、故障模拟等。

2.收集仿真所需的数据:根据仿真对象和目标,收集所需的数据,包括电路元件的参数、信号源的特性等。

3.建立数字模型:根据收集到的数据,建立数字系统的数学模型。

这个模型可以是差分方程、状态空间方程等形式。

还可以使用一些仿真软件来建立模型,比如MATLAB、SPICE等。

4.建立模拟模型:根据仿真对象和目标,建立模拟系统的模型。

这个模型可以是电路图、信号流图等形式。

5. 进行系统级仿真:将数字模型和模拟模型结合起来,进行系统级的仿真。

可以使用专门的混合仿真软件,比如Multisim、PSPICE等。

6.分析仿真结果:对仿真结果进行分析,比如观察系统的响应、性能指标等。

根据分析结果,对系统进行优化或改进。

7.优化系统设计:根据仿真结果,对系统进行优化设计。

可以进行参数调整、电路结构改进等操作。

8.重新进行仿真:在优化设计之后,重新进行仿真,以验证优化效果。

9.验证仿真结果:将仿真结果与实际系统进行验证,比较其一致性。

如果两者一致,则说明仿真模型是可靠的。

10.提出改进方案:如果仿真结果与实际系统存在差异,根据差异提出改进方案,并重新进行仿真与验证。

11.输出仿真报告:根据仿真结果,编写仿真报告,包括仿真目标、仿真方法、仿真结果、分析与改进等内容。

总结起来,数模混合仿真设计流程包括确定仿真对象与目标、收集仿真所需数据、建立数字模型与模拟模型、进行系统级仿真、分析仿真结果、优化系统设计、重新进行仿真、验证仿真结果、提出改进方案和输出仿真报告。

这个流程是一个迭代的过程,需要根据实际情况进行调整和修改。

芯片设计中数模混合集成电路设计流程芯片设计包含很多流程,每个流程的顺利实现才能保证芯片设计的正确性。

因此,对芯片设计流程应当具备一定了解。

本文将讲解芯片设计流程中的数字集成电路设计、模拟集成电路设计和数模混合集成电路设计三种设计流程。

数字集成电路设计多采用自顶向下设计方式,首先是系统的行为级设计,确定芯片的功能、性能,允许的芯片面积和成本等。

然后是进行结构设计,根据芯片的特点,将其划分成接口清晰、相互关系明确的、功能相对独立的子模块。

接着进行逻辑设计,这一步尽量采用规则结构来实现,或者利用已经验证过的逻辑单元。

接下来是电路级设计,得到可靠的电路图。

最后就是将电路图转换成版图。

系统功能描述主要确定集成电路规格并做好总体设计方案。

其中,系统规范主要是针对整个电子系统性能的描述,是系统最高层次的抽象描述,包括系统功能、性能、物理尺寸、设计模式、制造工艺等。

功能设计主要确定系统功能的实现方案,通常是给出系统的时序图及各子模块之间的数据流图,附上简单的文字,这样能更清晰的描述设计功能和内部结构。

为了使整个设计更易理解,一般在描述设计可见功能之后,对系统内部各个模块及其相互连接关系也进行描述。

描述从系统应用角度看,需要说明该设计适用场合、功能特性、在输入和输出之间的数据变换。

逻辑设计是将系统功能结构化。

通常以文本、原理图、逻辑图表示设计结果,有时也采用布尔表达式来表示设计结果。

依据设计规范完成模块寄存器传输级代码编写,并保证代码的可综合、清晰简洁、可读性,有时还要考虑模块的复用性。

随后进行功能仿真和FPGA 验证,反复调试得到可靠的源代码。

其中,还要对逻辑设计的RTL 级电路设计进行性能及功能分析,主要包括代码风格、代码覆盖率、性能、可测性和功耗评估等。

电路设计大体分为逻辑实现、版图前验证和版图前数据交付三个阶段。

逻辑实现将逻辑设计表达式转换成电路实现,即用芯片制造商提供的标准电路单元加上时间约束等条件,使用尽可能少的元件和连线完成从RTL描述到综合库单元之间的映射,得到一个在面积和时序上满足需求的门级网表。

数模混合电路的LVS流程1. 首先保证单独的模拟模块的设计完成,并且DRC LVS通过2. 把数字GDS导入生成layout,在导入版图中相应的引脚打上label和电源、地的label,同时将方括号[]改为尖括号<>。

如果数字版图存在结点label,应该将其删除,或者新建一个layout调用数字版图,重新打引脚label和电源、地label。

3. 将数字门级网表转化为cdl网表,Digital.cdl。

打开标准单元库的网表Stand.cdl,对其进行电源地的声明,如果标准单元库的器件类型与LVS文件提取的器件类型冲突则用.EQUIV进行替换。

.GLOBAL VDD.GLOBAL GND.EQUIV NM=NN PM=NP4. 对数字部分进行独立的DRC LVS,需要注意大小写的敏感问题,可通过LVS文件设置解决,在LVS文件中加入SOURCE CASE YESLAYOUT CASE YESLVS COMPARE YES5. 生成一个数字模块的symbol,内部电路为空,仅有端口pin和电源地pin。

假如:该模块的cell name名为Digital,模块的instance名为I2;6. 将数字模块的symbol和模拟模块连接在一起,形成一个完整的电路,顶层电路为MIX,提取混合电路的顶层网表MIX.cdl。

7. 将混合电路的顶层网表MIX.cdl,数字电路的网表Digital.cdl,标准单元库的网表Stand.cdl,放到一个命名为netlist的目录下,以方便管理,同时也需另备份一份。

8. 打开执行6后生成的MIX.cdl的网表,删除描述Digital模块的部分(.SUBCKT Digital)。

9. 打开执行3后生成的Digital.cdl找到电路端口的描述部分(.SUBCKT Digital)将端口的顺序修改为MIX.cdl中最后一部分I2的端口描述顺序,如果端口缺少电源地的描述,则须在此添加VDD和VSS的描述10. 重新建立一个空网表文件如TOP.cdl,在文件中include以下三个Digital.cdl,Stand.cdl,MIX.cdl网表。