数模混合电路的PCB设计

- 格式:docx

- 大小:11.40 KB

- 文档页数:3

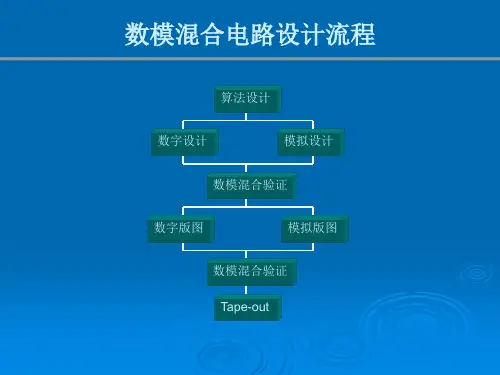

数模混合电路设计流程马昭鑫 2012/5/23本文主要面向模拟电路设计者,讲解了从行为级代码形式的数字电路到数模混合版图之间的流程,默认模拟版图和数字电路的行为级代码、testbench已经完成。

阅读者需确定自己会编写Verilog或Spice格式的网表,熟悉Linux的文件操作,了解Spectre、Virtuoso、Calibre、Modelsim、Design Compiler(dc)、Astro等EDA工具的使用方法。

由于本人才疏学浅,经验不足,难免会在文中出现一些错误,恳请高手给予指正。

数模混合电路的仿真方法一般的设计流程中数字电路和模拟电路是分开进行设计的,但有些时候希望能将数字电路和模拟电路放在一起仿真来验证设计,这就需要用到混合电路的仿真方法。

在Cadence 工具中有专门用作混合电路仿真的仿真器spectreVerilog,其实现方法是首先将模拟模块与数字模块区分开并设置接口电平,然后在ADE中设置数字电路的测试代码,调用不同的仿真器分别对数字模块和模拟模块进行仿真,最后将结果汇总显示或输出。

下面将以一个简单实例的形式讲解混合电路的仿真方法。

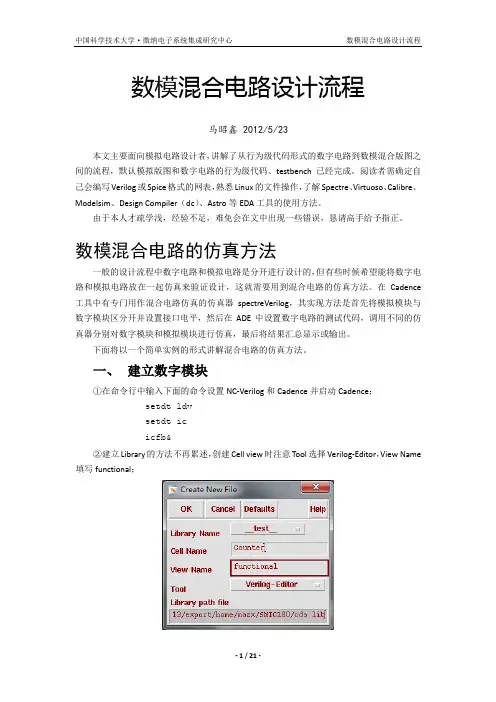

一、建立数字模块①在命令行中输入下面的命令设置NC-Verilog和Cadence并启动Cadence;setdt ldvsetdt icicfb&②建立Library的方法不再累述,创建Cell view时注意Tool选择Verilog-Editor,View Name 填写functional;③点击OK后会弹出有模块代码框架的vi窗口,将设计需要的代码输入或粘贴进去;④保存并关闭后如果没有错误会弹出创建Symbol View的询问对话框,确定后会进入Symbol编辑器,并自动生成了Symbol(注意在Cadence中总线用尖括号<>表示);⑤保存并关闭Symbol编辑器。

至此已经完成了数字模块的创建。

二、建立模拟模块模拟电路的创建方法无需赘述,这里搭建了一个输出频率为10MHz的环形振荡器。

高速数模混合电路信号完整性分析与PCB 设计作者:李莎来源:《电子技术与软件工程》2016年第12期随着科技持续发展,各种电子产品不断涌现,逐渐走上“高集成度、高可靠性”等道路。

在电路板发展中,高速数模混合电路成为新的发展趋势,被广泛应用到不同领域、行业中。

由于高速数模混合 PCB 不同于传统的PCB,需要灵活运用新的方法来合理设计 PCB,确保高速数模混合电路的稳定运行,其信号具有其完整性,更好地发挥自身的作用。

【关键词】PCB设计高速数模混合电路信号完整性分析在电子系统时钟频率逐渐提高的过程中,电路信号完整性问题不断显现,比如,出现错误的时序,传输线的反射不正确,严重影响电路系统的正常运行,而 PCB 上的各线路会更加紧凑,出现串扰噪声,信号传输效果较差。

对于高速数模混合电路来说,需要结合线路运行的实际情况,合理设计 PCB,解决电路信号的完整性问题,不断提高信号传输的质量,为不同行业、领域发展提供重要的信息资源,促进其发展。

1 高速数模混合电路信号完整性分析信号完整性就是在信号线上,信号的质量。

想要保证信号的完整性,必须满足一定的要求,要确保空间的完整性,能够满足电路相关的要求,比如,最大输入的低电平要求。

还要确保时间上的完整性,要能够有效维护电路的最小维持时间等。

1.1 影响电路信号完整性的因素分析就信号完整性而言,受到多种因素的影响。

一是:延迟。

就信号而言,其传输要借助PCB 板的导线,在传输过程中,会出现传输延迟现象。

一旦传输的信号延迟,电路系统时序将会受到影响,进而影响信号的完整性。

就传输延迟来说,会受制于导线的长度、周围介质的介质常数。

二是:反射、串扰噪声。

在电路系统运行中,如果信号线网出现过孔、弯曲等问题,将会产生反射噪声。

如果电路信号网、电源分布系统等之间出现电磁耦合,将会产生串扰噪声,都会干扰信号,影响信号的传输。

1.2 处理电路信号完整性问题的关键1.2.1 电源分布在设计高速数模混合电路板过程中,要全方位分析电源分布网络。

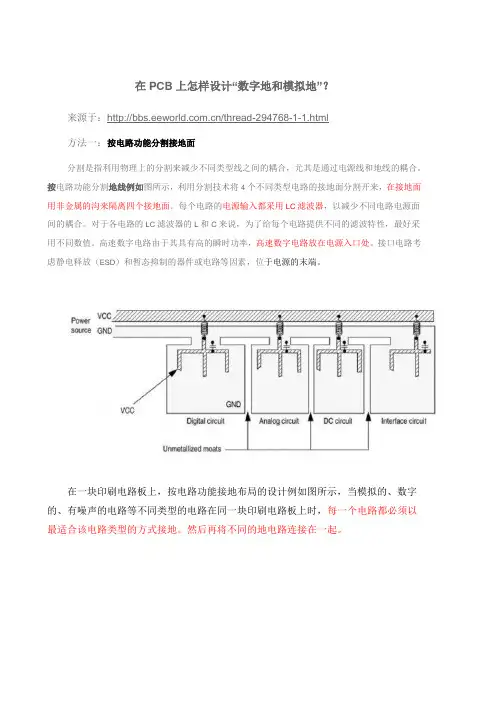

在PCB上怎样设计“数字地和模拟地”?来源于:/thread-294768-1-1.html方法一:按电路功能分割接地面分割是指利用物理上的分割来减少不同类型线之间的耦合,尤其是通过电源线和地线的耦合。

按电路功能分割地线例如图所示,利用分割技术将4个不同类型电路的接地面分割开来,在接地面用非金属的沟来隔离四个接地面。

每个电路的电源输入都采用LC滤波器,以减少不同电路电源面间的耦合。

对于各电路的LC滤波器的L和C来说,为了给每个电路提供不同的滤波特性,最好采用不同数值。

高速数字电路由于其具有高的瞬时功率,高速数字电路放在电源入口处。

接口电路考虑静电释放(ESD)和暂态抑制的器件或电路等因素,位于电源的末端。

在一块印刷电路板上,按电路功能接地布局的设计例如图所示,当模拟的、数字的、有噪声的电路等不同类型的电路在同一块印刷电路板上时,每一个电路都必须以最适合该电路类型的方式接地。

然后再将不同的地电路连接在一起。

二.采用局部接地面振荡器电路、时钟电路、数字电路、模拟电路等可以被安装在一个单独的局部接地面上。

这个局部接地面设置在PCB的顶层,它通过多个通孔与PCB的内部接地层(0V参考面)直接连接,一个设计例如图5.7.20所示。

将振荡器和时钟电路安装在一个局部接地面上,可以提供一个镜像层,捕获振荡器内部和相关电路产生的共模RF电流,这样就可以减少RF辐射。

当使用局部接地面时,注意不要穿过这个层来布线,否则会破坏镜像层的功能。

如果一条走线穿过局部化接地层,就会存在小的接地环路或不连续性电位。

这些小的接地环路在射频时会引起一些问题。

如果某器件应用不同的数字接地或不同的模拟接地,该器件可以布置在不同的局部接地面,通过绝缘的槽实现器件分区。

进入各部件的电源电压使用铁氧体、磁珠和电容器进行滤波。

一个设计例如图5.7.21和图5.7.22所示。

三:PCB采用“无噪声”的I/O地与“有噪声”的数字地分割设计为了使用电缆去耦或屏蔽技术来抑制共模噪声,在PCB设计时,需要考虑为电缆的去耦(将电流分流到地)和屏蔽提供没有受到数字逻辑电路噪声污染的“无噪声”或者“干净”的地。

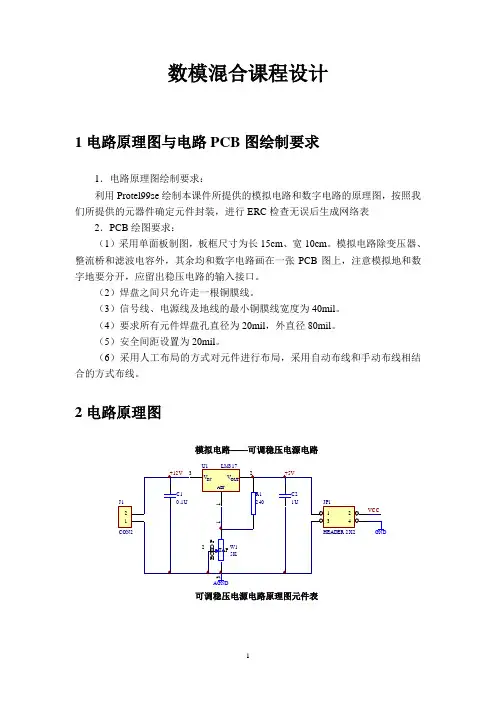

数模混合课程设计1电路原理图与电路PCB 图绘制要求1.电路原理图绘制要求:利用Protel99se 绘制本课件所提供的模拟电路和数字电路的原理图,按照我们所提供的元器件确定元件封装,进行ERC 检查无误后生成网络表2.PCB 绘图要求:(1)采用单面板制图,板框尺寸为长15cm 、宽10cm 。

模拟电路除变压器、整流桥和滤波电容外,其余均和数字电路画在一张PCB 图上,注意模拟地和数字地要分开,应留出稳压电路的输入接口。

(2)焊盘之间只允许走一根铜膜线。

(3)信号线、电源线及地线的最小铜膜线宽度为40mil 。

(4)要求所有元件焊盘孔直径为20mil ,外直径80mil 。

(5)安全间距设置为20mil 。

(6)采用人工布局的方式对元件进行布局,采用自动布线和手动布线相结合的方式布线。

2电路原理图模拟电路——可调稳压电源电路可调稳压电源电路原理图元件表....补充:画原理图时J1、JP1、R1、C1、C2均在Miscellaneous Devices.lib 中查找,而U1、W1则在Simulation Symbols.lib中查找。

画PCB时JP1的封装TS100V2X2在2.54mm Connectors.lib中,其余均在pcbfootprints.lib中。

注意库里的LM317和电位器RPOT的元件引脚和实际元件引脚不一致,应先将元件库里LM317和电位器RPOT元件的引脚进行修改。

数字电路——计数器电路时钟秒计数电路原理图元件表补充:画原理图时S1、H1、R2、R3、R4、R5、R6、C3、C4均在Miscellaneous Devices.lib 中查找;而U2则在TIMER.lib中查找,X1、X2可在7segdisp.lib中查找,并修改引脚与参考图一致;U3在NSC CMOS Logic Databook1988(commercial).lib中查找,U4、U5需自建元件库画元件。

P CB布局的好与否,直接影响产品质量和稳定性,今天就给大家分享几种混合PCB布局的技巧。

一元器件放置在元器件放置的时候要遵循原理图的信号路径,还需要为走线提供空间。

除此之外,要遵循以下放置规则:•电源部分应紧凑地放置在一起,并适当的去耦实现电源完整性•去耦电容应尽可能靠近各个器件放置•连接器应放置在板的边缘•遵循高频组件的原理图流程•大型存储设备和处理器(例如时钟发生器和控制器)应放置在电路板的中心二模拟和数字模块分离为了最大限度地减少模拟和数字信号的公共返回路径,要将模拟和数字模块分开,防止模拟信号与数字信号混合。

模拟和数字电路分离上图显示了模拟和数字电路分离的一个示例。

在划分模拟部分和数字部分时,应牢记以下几点:•建议在模拟平面安装精密的模拟元件,例如放大器和基准电压源。

另一侧/数字平面必须用于噪声数字组件,例如逻辑控制和定时块。

•系统中的模数转换器(ADC) 或数模转换器(DAC) 是混合信号且具有低数字电流,其处理方式与模拟组件在模拟系统中的处理方式类似。

•对于具有大量高电流ADC 和DAC 的设计,建议将模拟电源和数字电源分开。

换句话说,DVDD应该连接到数字部分,而AVCC必须连接到模拟部分。

•微处理器和微控制器产生的空间和热量可能很大。

为了改善散热,这些组件必须放置在电路板的中心,并且必须靠近它们要连接的电路块。

三跟踪路由将所有组件正确放置在最佳位置并建立适当的接地平面后,大多数路线自然会遵循正确的路径。

但是,在跟踪路由时应牢记以下准则:•信号路径应尽可能直接且短•具有高速信号路径的层应有一个与其相邻的接地层,以确保正确的返回信号•高速电路特别敏感,需要遵循原理图中布置的信号路径•通过使用短、直接和宽的走线来减少电源布线中的电感•在布线走线和过孔时不要创建天线•电源布线应该短、紧凑并且应该有宽走线•布线需要保持数字和模拟电路元件之间的隔离•接地很重要,特别是对于连接数字和模拟分区区域的走线四电源模块电源是电路的重要组成部分,需要小心处理。

目录:前言一、数模混合设计的难点二、提高数模混合电路性能的关键三、仿真工具在数模混合设计中的应用四、小结五、混合信号PCB设计基础问答前言:数模混合电路的设计,一直是困扰硬件电路设计师提高性能的瓶颈。

众所周知,现实的世界都是模拟的,只有将模拟的信号转变成数字信号,才方便做进一步的处理。

模拟信号和数字信号的转变是否实时、精确,是电路设计的重要指标。

除了器件工艺,算法的进步会影响系统数模变换的精度外,现实世界中众多干扰,噪声也是困扰数模电路性能的主要因素。

本文通过Ansoft公司的“AD-Mix Si gnal Noise Design Suites” 数模混合噪声仿真设计软件的对数模混合设计PC B的仿真,探索分析数模混合电路的噪声干扰和优化设计的途径,以达到改善系统性能目的。

一、数模混合设计的难点数模混合电路设计当中,干扰源、干扰对象和干扰途径的辨别是分析数模混合设计干扰的基础。

通常的电路中,模拟信号上由于存在随时间变化的连续变化的电压和电流有效成分,在设计和调试过程中,需要同时控制这两个变量,而且他们对于外部的干扰更敏感,因而通常作为被干扰对象做分析;数字信号上只有随时间变化的门限量化后的电压成分,相比模拟信号对干扰有较高的承受能力,但是这类信号变化快,特别是变化沿速度快,还有较高的高频谐波成分,对外释放能量,通常作为干扰源。

作为干扰源的数字电路部分多采用CMOS工艺,从而导致数字信号输入端极高的输入电阻,通常在几十k欧到上兆欧姆。

这样高的内阻导致数字信号上的电流非常微弱,因而只有电压有效信号在起作用,在数模混合干扰分析中,这类信号可以作为电压型干扰源,如CLK信号,Reset等信号。

除了快速交变的数字信号,数字信号的电源管脚上,由于引脚电感和互感引起的同步开关噪声(SSN),也是数模混合电路中存在的重要一类电压型干扰源。

此外,电路中还存在一些电流信号,特别是直流电源到器件负载之间的电源信号上有较大的电流,根据右手螺旋定理,电流信号周围会感应出磁场,进而引起变化的电场,在分析时,直流电源作为电流型干扰源。

MSP430数模混合应用的PCB设计技巧微控论坛原创主贴作者:DC版主以下是我常用MSP430所整理个人心得,希望能给新手们做一些应用参考。

以下纯属个人意见,如网友发现有不当之前还请给予指出和讨论。

关于MSP430数模混合应用中的PCB设计技巧将分3个小节:[1]ADC12相关的几个引脚功能与使用[2]数模混合应用中的PCB布局和电源电路的拓扑结构[3]常见不良的PCB处理与误区[1]ADC12相关的几个引脚功能与使用VREF+/VeREF+为ADC模块的正极参考基准电压源。

分别为内部参考电压输出、或外部正参考电压输入。

VREF-/VeREF- 为ADC模块的负极参考基准电压源。

分别为内部负参考电压、或外部负参考电压输入。

以MSP430F5438为例芯片功能引脚分别为P5.0/VREF+/VeREF+和P5.1/VREF-/VeREF-。

一般情况芯片上电时默认为IO功能。

如果需要使用其相应功能则需要对引脚进行配置。

比如,设置相关的引脚为其应用设置为VREF+和VREF-则执行:ADC12CTL2 &= ~ADC12REFOUT; // 设置ADC12REFOUT位为0P5SEL |= BIT0; // P50设置VREF+内部参考电压输出功能P5SEL |= BIT1; // P51设置VREF-内部参考电压输出功能若使VeREF+和VeREF-则执行:ADC12CTL2 |= ADC12REFOUT; // 设置ADC12REFOUT位为1P5SEL |= BIT0; // P50设置VeREF+外部参考电压输入功能P5SEL |= BIT1; // P51设置VeREF-内部参考电压输入功能对于上面的ADC12CTL2是ADC12_A控制寄存器2,只有MSP430F5系列产品中才使用。

之前的F1、2、4系列未有此寄存器,但有相同的功能引脚。

由于F5的设置方式有小小特别所以本例特以此为例加以说明。

cadence数模混合课程设计一、课程目标知识目标:1. 理解数模混合电路的基本概念,掌握Cadence软件中数模混合电路的设计流程;2. 掌握数模混合电路中模拟电路与数字电路的接口技术,了解其相互影响;3. 学会使用Cadence软件进行数模混合电路的仿真与优化。

技能目标:1. 能够运用Cadence软件设计简单的数模混合电路;2. 能够分析数模混合电路中可能出现的常见问题,并运用所学知识进行解决;3. 具备一定的电路调试与优化能力,提高实际工程应用中的问题解决能力。

情感态度价值观目标:1. 培养学生对数模混合电路设计的兴趣,激发其创新意识;2. 增强学生团队协作意识,培养良好的沟通与协作能力;3. 强化质量意识,使学生认识到严谨的工程态度在电路设计中的重要性。

课程性质:本课程为实践性较强的课程,结合理论知识与实际操作,注重培养学生的动手能力和实际问题解决能力。

学生特点:高年级学生,已具备一定的电子电路基础知识,具有较强的学习能力和自主性。

教学要求:结合学生特点,注重理论与实践相结合,强调实际操作,以项目为导向,提高学生的实际工程能力。

在教学过程中,关注学生的个体差异,针对性地进行指导,确保课程目标的实现。

通过课程学习,使学生能够独立完成数模混合电路的设计与优化,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. 数模混合电路基本概念:包括模拟电路、数字电路特点,数模混合电路的定义及其在电子系统中的应用。

教材章节:第二章 数模混合电路基础2. Cadence软件操作:介绍Cadence软件的基本操作,原理图绘制,电路仿真等。

教材章节:第三章 Cadence软件操作3. 数模混合电路设计流程:讲解从电路设计、原理图绘制、仿真测试到PCB 设计的完整流程。

教材章节:第四章 数模混合电路设计流程4. 接口技术:分析模拟电路与数字电路之间的接口技术,包括信号转换、阻抗匹配等。

教材章节:第五章 接口技术5. 电路仿真与优化:介绍仿真方法,参数设置,优化策略等,提高电路性能。

杭州电子科技大学硕士学位论文高速数模混合电路信号完整性分析与PCB设计姓名:李小荣申请学位级别:硕士专业:电路与系统指导教师:王健20100201摘要现代电子产品正朝着高速、高集成度和高可靠性的方向发展。

带宽高达百MHz甚至GHz 的高速运放与高速数模转换器在视频处理、信号采集、实时检测等电路中的应用越来越多;边沿速率达ps级的高速数字器件已相当普遍。

相应地,高速数模混合电路板(Printed Circuit Board,PCB)成为电路板发展的新趋势。

高速数模混合PCB具有新的特点,传统的PCB设计方法已不能满足需求,这类PCB设计面临着新的挑战,要求采取新的设计方法和手段,来保证产品设计的首件成功率。

信号完整性(signal Integrity,简称SI)是指信号在互连线上的传输质量。

在一个高速互连系统中,信号流经芯片内部连线、芯片封装、PCB布线通道、焊盘、过孔等,任何信号传输路径都有可能引发信号完整性问题,本论文把问题主要集中在板级互连上。

高速系统中,PCB 上高速信号间的互连不再是畅通和透明的,高速的互连线对系统的影响已不能被简单忽略。

互连引起的信号完整性问题可能会导致系统工作不稳定,甚至不能正常工作。

如何处理由高速互连线引起的信号完整性问题,是现代高速混合电路PCB设计能否成功的关键。

信号完整性设计需要贯穿于整个项目设计的各个阶段,需要在设计阶段尽早地解决潜在的问题。

本论文基于高频效应、传输线理论、电磁干扰理论,对反射、串扰、同步开关噪声(SSN)、电磁干扰(EMI)等信号完整性问题进行深入分析,根据理论分析与实际经验给出各种相应问题的解决方法。

笔者通过对一块高速数据采集卡进行信号完整性分析与PCB设计,主要从优化高速模拟电路PCB和高速数字电路PCB的信号完整性出发,来确保各部分的信号质量并减小数模之间的干扰,从而探索出高速数模混合PCB的设计方法和设计流程。

笔者运用Cadence Allegro PCB SI与Ansoft SIwave/Designer SI仿真工具,对采集卡中的关键网络与整板进行仿真分析,通过对高速数字电路中的反射、串扰、同步开关噪声、传导与辐射等进行仿真分析来优化干扰源和干扰途径。

PCB设计之模拟电路数字电路本文就旁路电容、电源、地线设计、电压误差和由布线引起的电磁干扰(EMI)等几个方面,讨论模拟和数字布线的基本相似之处及差别。

工程领域中的数字设计人员和板设计专家在不断增加,这反映了行业的发展趋势。

尽管对数字设计的重视带来了电子产品的重大发展,但仍然存在,而且还会一直存在一部分与模拟或现实环境接口的电路设计。

模拟和数字领域的布线策略有一些类似之处,但要获得更好的结果时,由于其布线策略不同,简单电路布线设计就不再是最优方案了。

本文就旁路电容、电源、地线设计、电压误差和由布线引起的电磁干扰(EMI)等几个方面,讨论模拟和数字布线的基本相似之处及差别。

模拟和数字布线策略的相似之处旁路或去耦电容在布线时,模拟器件和数字器件都需要这些类型的电容,都需要靠近其电源引脚连接一个电容,此电容值通常为0.1uF。

系统供电电源侧需要另一类电容,通常此电容值大约为10uF。

这些电容的位置如图1所示。

电容取值范围为推荐值的1/10至10倍之间。

但引脚须较短,且要尽量靠近器件(对于0.1uF电容)或供电电源(对于10uF电容)。

在电路板上加旁路或去耦电容,以及这些电容在板上的位置,对于数字和模拟设计来说都属于常识。

但有趣的是,其原因却有所不同。

在模拟布线设计中,旁路电容通常用于旁路电源上的高频信号,如果不加旁路电容,这些高频信号可能通过电源引脚进入敏感的模拟芯片。

一般来说,这些高频信号的频率超出模拟器件抑制高频信号的能力。

如果在模拟电路中不使用旁路电容的话,就可能在信号路径上引入噪声,更严重的情况甚至会引起振动。

图1 在模拟和数字设计中,旁路或去耦电容(0.1uF)应尽量靠近器件放置。

供电电源去耦电容(10uF)应放置在电路板的电源线入口处。

所有情况下,这些电容的引脚都应较短图2 在此电路板上,使用不同的路线来布电源线和地线,由于这种不恰当的配合,电路板的电子元器件和线路受电磁干扰的可能性比较大图3 在此单面板中,到电路板上器件的电源线和地线彼此靠近。

数模混合电路的PCB设计

高速PCB 设计中,数模混合电路的PCB 设计中的干扰问题一直是一个难题。

尤其模拟电路一般是信号的源头,能否正确接收和转换信号是PCB 设计要考虑的重要因素。

文章通过分析混合电路干扰产生的机理,结合设计实践,探讨了混合电路一般处理方法,并通过设计实例得到验证。

0 前言

印制电路板(PCB)是电子产品中电路元件和器件的支撑件,它提供电路元件和器件之间的电气连接。

现在有许多PCB 不再是单一功能电路,而是由数字电路和模拟电路混合构成的。

数据一般在模拟电路中采集和接收,而带宽、增益用软件实现控制则必须数字化,所以在一块板上经常同时存在数字电路和模拟电路,甚至共享相同的元件。

考虑到它们之间的相互干扰问题以及对电路性能的影响,电路的布局和布线必须要有一定的原则。

混合信号PCB 设计中对电源传输线的特殊要求以及隔离模拟和数字电路之间噪声耦合的要求,增加了设计时布局和布线的复杂度。

在此,通过分析高密度混合信号PCB 的布局和布线设计,来达到要求的PCB 设计目标。

1 数模混合电路干扰的产生机理

模拟信号与数字信号相比,对噪声的敏感程度要大得多,因为模拟电路的工作依赖连续变化的电流和电压,任何微小的干扰都能影响它的正常工作,而数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,具有一定的抗干扰能力。

但在混合信号环境中,数字信号相对模拟信号而言是一种噪声源。

数字电路工作时,稳定的有效电压只有高低电平两种电压。

当数字逻辑输出由高电压变为低电压,该器件的接地管脚就会放电,产生开关电流,这就是电路的开关动作。

数字电路的速度越快,其开关时间一般也。