EDA实验五 状态机

- 格式:doc

- 大小:123.00 KB

- 文档页数:4

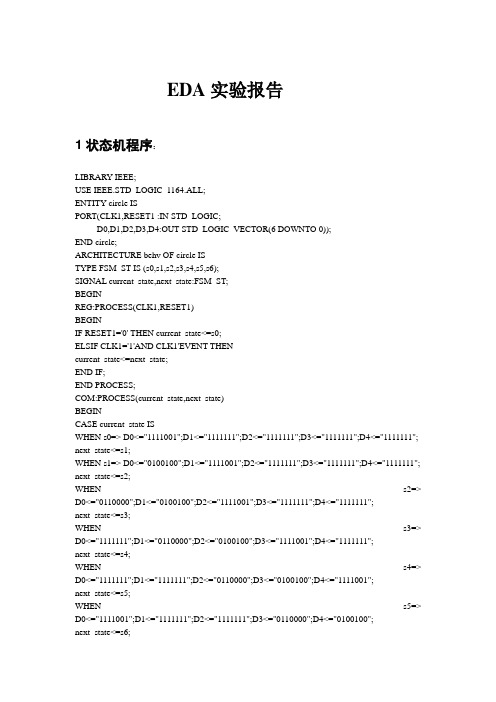

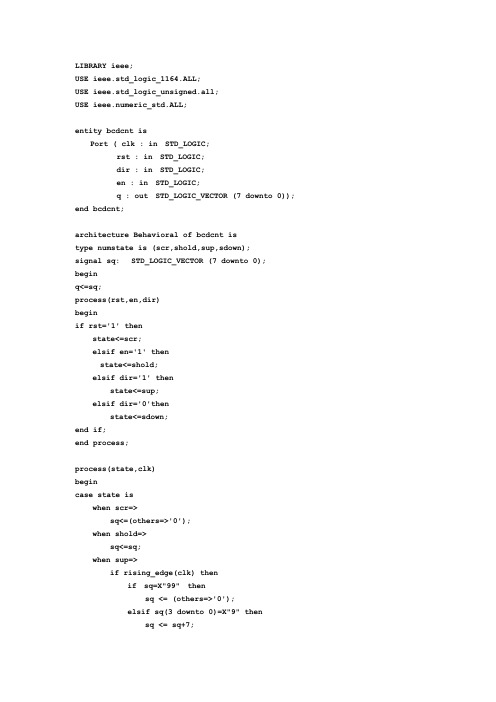

EDA实验报告1状态机程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY circle ISPORT(CLK1,RESET1 :IN STD_LOGIC;D0,D1,D2,D3,D4:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END circle;ARCHITECTURE behv OF circle ISTYPE FSM_ST IS (s0,s1,s2,s3,s4,s5,s6);SIGNAL current_state,next_state:FSM_ST;BEGINREG:PROCESS(CLK1,RESET1)BEGINIF RESET1='0' THEN current_state<=s0;ELSIF CLK1='1'AND CLK1'EVENT THENcurrent_state<=next_state;END IF;END PROCESS;COM:PROCESS(current_state,next_state)BEGINCASE current_state ISWHEN s0=> D0<="1111001";D1<="1111111";D2<="1111111";D3<="1111111";D4<="1111111"; next_state<=s1;WHEN s1=> D0<="0100100";D1<="1111001";D2<="1111111";D3<="1111111";D4<="1111111"; next_state<=s2;WHEN s2=> D0<="0110000";D1<="0100100";D2<="1111001";D3<="1111111";D4<="1111111";next_state<=s3;WHEN s3=> D0<="1111111";D1<="0110000";D2<="0100100";D3<="1111001";D4<="1111111";next_state<=s4;WHEN s4=> D0<="1111111";D1<="1111111";D2<="0110000";D3<="0100100";D4<="1111001";next_state<=s5;WHEN s5=> D0<="1111001";D1<="1111111";D2<="1111111";D3<="0110000";D4<="0100100";next_state<=s6;WHEN s6=> D0<="0010010";D1<="1111001";D2<="1111111";D3<="1111111";D4<="0110000";next_state<=s2;END CASE;END PROCESS;END behv;2.1秒时间程序:USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY timer1 ISPORT(CLK,RESET:IN STD_LOGIC;CONT:OUT STD_LOGIC);END ENTITY timer1;ARCHITECTURE bhv OF timer1 ISBEGINPROCESS(CLK,RESET)V ARIABLE Q:INTEGER RANGE 0 TO 50000000;BEGINIF RESET='0' THEN CONT<='0';ELSIF CLK'EVENT AND CLK ='1' THEN Q:=Q+1;END IF;IF Q=50000000 THEN Q:=0;CONT<='1';ELSE CONT<='0';END IF;END PROCESS;END bhv;3.总程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY circle123 ISPORT(CLK2,RESET2:IN STD_LOGIC;b1,b2,b3,b4,b5:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ENTITY circle123;ARCHITECTURE one OF circle123 ISCOMPONENT timer1PORT(CLK,RESET:IN STD_LOGIC;CONT:OUT STD_LOGIC);END COMPONENT;COMPONENT circlePORT(CLK1,RESET1 :IN STD_LOGIC;D0,D1,D2,D3,D4:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;SIGNAL H:STD_LOGIC;BEGINu1:timer1 PORT MAP(CLK=>CLK2,RESET=>RESET2,CONT=>H);u2:circle PORT MAP(CLK1=>H,RESET1=>RESET2,D0=>b1,D1=>b2,D2=>b3,D3=>b4,D4=>b5);END ARCHITECTURE one;4.时序仿真波形图:5.效果图:。

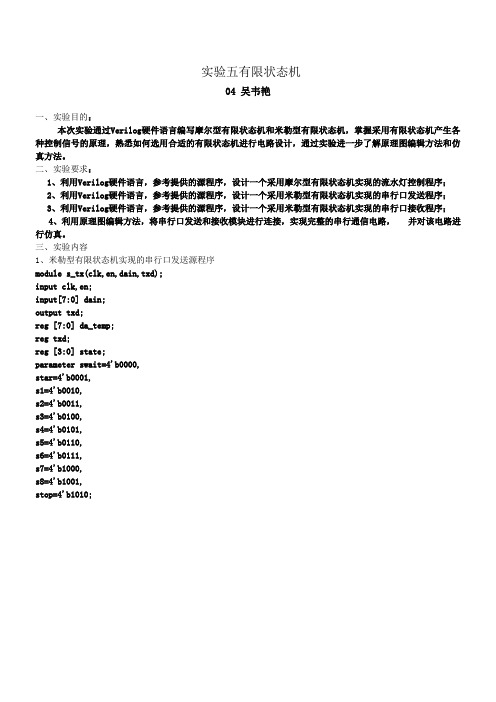

实验五有限状态机04 吴韦艳一、实验目的:本次实验通过Verilog硬件语言编写摩尔型有限状态机和米勒型有限状态机,掌握采用有限状态机产生各种控制信号的原理,熟悉如何选用合适的有限状态机进行电路设计,通过实验进一步了解原理图编辑方法和仿真方法。

二、实验要求:1、利用Verilog硬件语言,参考提供的源程序,设计一个采用摩尔型有限状态机实现的流水灯控制程序;2、利用Verilog硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的串行口发送程序;3、利用Verilog硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的串行口接收程序;4、利用原理图编辑方法,将串行口发送和接收模块进行连接,实现完整的串行通信电路,并对该电路进行仿真。

三、实验内容1、米勒型有限状态机实现的串行口发送源程序module s_tx(clk,en,dain,txd);input clk,en;input[7:0] dain;output txd;reg [7:0] da_temp;reg txd;reg [3:0] state;parameter swait=4'b0000,star=4'b0001,s1=4'b0010,s2=4'b0011,s3=4'b0100,s4=4'b0101,s5=4'b0110,s6=4'b0111,s7=4'b1000,s8=4'b1001,stop=4'b1010;always @(posedge en)da_temp<=dain;always @(posedge clk)if (!en)beginstate<=swait;txd<=1;endelsecase(state)swait: begin state<=star;txd<=1; endstar: begin state<=s1; txd<=0; end //状态转换s1: begin state<=s2; txd<=da_temp[7]; ends2: begin state<=s3; txd<=da_temp[6]; ends3: begin state<=s4; txd<=da_temp[5]; ends4: begin state<=s5; txd<=da_temp[4]; ends5: begin state<=s6; txd<=da_temp[3]; ends6: begin state<=s7; txd<=da_temp[2]; ends7: begin state<=s8; txd<=da_temp[1]; ends8: begin state<=stop; txd<=da_temp[0]; end stop: begin state<=stop; txd<=1; endendcaseendmodule2、米勒型有限状态机实现的串行口接收源程序module s_rx(clk,dain,daout);input clk,dain;output [7:0] daout;reg [7:0] daout;reg [7:0] da_temp;reg [3:0] state;parameter star=4'b0000,s1=4'b0010,s2=4'b0011,s3=4'b0100,s4=4'b0101,s5=4'b0110,s6=4'b0111,s7=4'b1000,s8=4'b1001,stop=4'b1010;always @(negedge clk)case (state)star: if (dain)state<=star;elsestate<=s1; //数据开始位为0s1:begin state<=s2; da_temp[7]<=dain; end //状态转换s2:begin state<=s3; da_temp[6]<=dain; ends3:begin state<=s4; da_temp[5]<=dain; ends4:begin state<=s5; da_temp[4]<=dain; ends5:begin state<=s6; da_temp[3]<=dain; ends6:begin state<=s7; da_temp[2]<=dain; ends7:begin state<=s8; da_temp[1]<=dain; end //8个状态s8:begin state<=stop; da_temp[0]<=dain; end //数据结束位为1 stop:if (!dain)state<=stop;elsebeginstate<=star;daout<=da_temp;endendcaseEndmodule3、由s_tx和s_rx组成的电路4、对以上电路做波形仿真5、状态机6、实验总结通过本次实验我掌握采用有限状态机产生各种控制信号的原理,熟悉如何选用合适的有限状态机进行电路设计,通过实验进一步了解了原理图编辑方法和仿真方法。

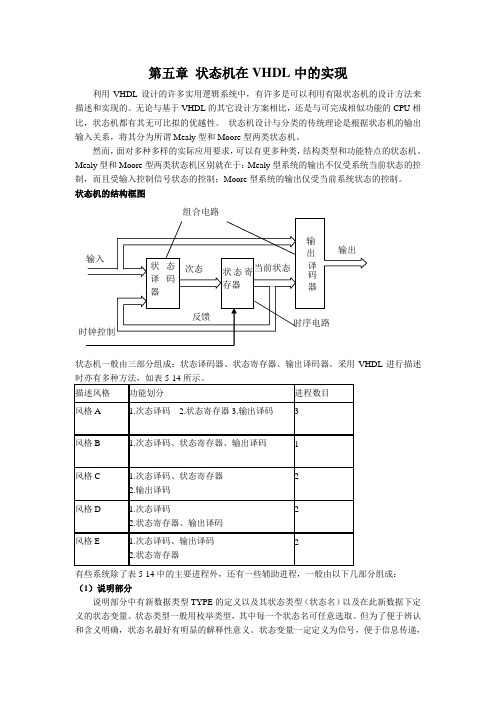

第五章状态机在VHDL中的实现利用VHDL设计的许多实用逻辑系统中,有许多是可以利用有限状态机的设计方法来描述和实现的。

无论与基于VHDL的其它设计方案相比,还是与可完成相似功能的CPU相比,状态机都有其无可比拟的优越性。

状态机设计与分类的传统理论是根据状态机的输出输入关系,将其分为所谓Mealy型和Moore型两类状态机。

然而,面对多种多样的实际应用要求,可以有更多种类,结构类型和功能特点的状态机。

Mealy型和Moore型两类状态机区别就在于:Mealy型系统的输出不仅受系统当前状态的控制,而且受输入控制信号状态的控制;Moore型系统的输出仅受当前系统状态的控制。

状态机的结构框图状态机一般由三部分组成:状态译码器、状态寄存器、输出译码器。

采用VHDL进行描述有些系统除了表5-14中的主要进程外,还有一些辅助进程,一般由以下几部分组成:(1)说明部分说明部分中有新数据类型TYPE的定义以及其状态类型(状态名)以及在此新数据下定义的状态变量。

状态类型一般用枚举类型,其中每一个状态名可任意选取。

但为了便于辨认和含义明确,状态名最好有明显的解释性意义。

状态变量一定定义为信号,便于信息传递,说明部分放在结构体的定义语句区即ARCHITECTURE和BEGIN之间。

例如:ARCHITECTURE ...ISTYPE states IS (st0,st1,st2,st3); --定义新的数据类型和状态名SIGNAL current_state,next_state:states;--定义状态变量...BEGIN...;(2)主控时序进程主控时序进程完成状态转移的功能。

状态机是随外部时钟信号,以同步时序方式工作的,因此,状态机中必须包含一个对工作时钟信号敏感的进程,作为状态机的“驱动泵”。

状态机的下一个状态(包括再次进入本状态)仅仅取决于时钟信号的到来。

根据实际情况来决定,此进程中也可以放置一些同步清零或置位方面的控制信号。

实验一组合电路的设计1. 实验目的:熟悉MAX + plus II 的VHDL 文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2. 实验内容:设计一个2选1多路选择器,并进行仿真测试,给出仿真波形。

3. 实验程序如下:library ieee;use ieee.std_logic_1164.all; entity mux21a isport(a,b,s:in std_logic;y:out std_logic); end entity mux21a; architecture one of mux21a is beginy<=a when s='0' else b ; end architecture one ;4. 仿真波形(如图1-1所示)图1-1 2选1多路选择器仿真波形5. 试验总结:从仿真波形可以看出此2选1多路选择器是当s为低电平时,y输出为b, 当s为高电平时,y输出为a(y<=a when s='0' else b ;),完成2路选择输出。

实验二时序电路的设计1. 实验目的:熟悉MAX + plus II VHDL文本设计过程,学习简单的时序电路设计、仿真和测试。

2. 实验验内容:设计一个锁存器,并进行仿真测试,给出仿真波形。

3. 实验程序如下:library ieee;use ieee.std_logic_1164.all;entity suocun7 isport(clk: in std_logic;en: in std_logic;D: in std_logic_vector(7 downto 0);B:out std_logic_vector(7 downto 0)); end suocun7;architecture one of suocun7 issignal K: std_logic_vector(7 downto 0); beginprocess(clk,en,D)beginif clk'event and clk='1' thenif en ='0'thenK<=D;end if;end if;end process;B<=K;end one;4.仿真波形(如图2-1所示)图2-1 8位锁存器仿真波形此程序完成的是一个8位锁存器,当时钟上升沿到来(clk'event and clk='1')、使能端为低电平(en ='0')时,输出为时钟上升沿时的前一个数,从仿真波形看,实现了此功能。

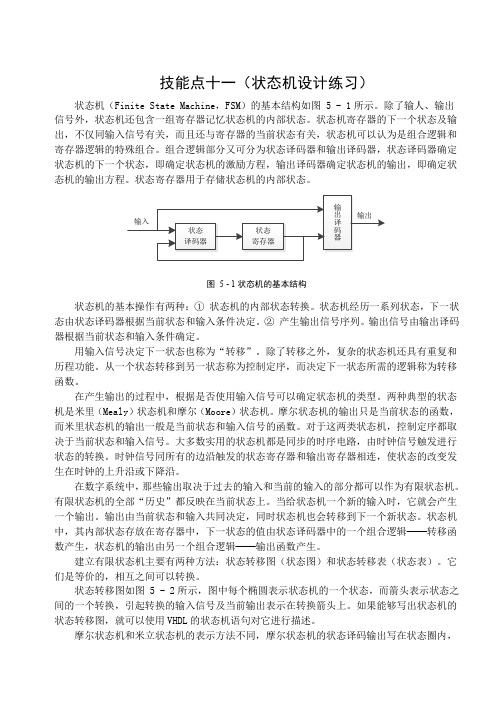

技能点十一(状态机设计练习)状态机(Finite State Machine,FSM)的基本结构如图 5 - 1所示。

除了输人、输出信号外,状态机还包含一组寄存器记忆状态机的内部状态。

状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还与寄存器的当前状态有关,状态机可以认为是组合逻辑和寄存器逻辑的特殊组合。

组合逻辑部分又可分为状态译码器和输出译码器,状态译码器确定状态机的下一个状态,即确定状态机的激励方程,输出译码器确定状态机的输出,即确定状态机的输出方程。

状态寄存器用于存储状态机的内部状态。

图 5 - 1状态机的基本结构状态机的基本操作有两种:①状态机的内部状态转换。

状态机经历一系列状态,下一状态由状态译码器根据当前状态和输入条件决定。

②产生输出信号序列。

输出信号由输出译码器根据当前状态和输入条件确定。

用输入信号决定下一状态也称为“转移”。

除了转移之外,复杂的状态机还具有重复和历程功能。

从一个状态转移到另一状态称为控制定序,而决定下一状态所需的逻辑称为转移函数。

在产生输出的过程中,根据是否使用输入信号可以确定状态机的类型。

两种典型的状态机是米里(Mealy)状态机和摩尔(Moore)状态机。

摩尔状态机的输出只是当前状态的函数,而米里状态机的输出一般是当前状态和输入信号的函数。

对于这两类状态机,控制定序都取决于当前状态和输入信号。

大多数实用的状态机都是同步的时序电路,由时钟信号触发进行状态的转换。

时钟信号同所有的边沿触发的状态寄存器和输出寄存器相连,使状态的改变发生在时钟的上升沿或下降沿。

在数字系统中,那些输出取决于过去的输入和当前的输入的部分都可以作为有限状态机。

有限状态机的全部“历史”都反映在当前状态上。

当给状态机一个新的输入时,它就会产生一个输出。

输出由当前状态和输入共同决定,同时状态机也会转移到下一个新状态。

状态机中,其内部状态存放在寄存器中,下一状态的值由状态译码器中的一个组合逻辑——转移函数产生,状态机的输出由另一个组合逻辑——输出函数产生。

案例5状态机:MOORE机、MEALY机(以序列检测器为主要内容)5.1 预习内容(1)状态机的基本概念,分类,原理,设计方法,时序情况。

(2)状态机的具体设计流程:逻辑抽象--状态定义--状态转换分析,画出状态图--根据状态图写出代码。

5.2 案例目的熟悉利用QuartusⅡ的代码输入方法设计状态机,并掌握编程配置以及硬件测试验证等一系列相关技术,并理解FPGA/CPLD技术中是如何解决生活中实际逻辑问题的。

5.3 案例环境状态机是数字系统设计中重要的内容之一。

无论是简单的译码电路还是复杂的CPU都可以用状态机来实现。

5.4 案例原理序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号这在数字通信领域有广泛的应用当序列检测器连续收到一组串行二进制码后如果这组码与检测器中预先设置的码相同则输出1否则输出0由于这种检测的关键在于正确码的收到必须是连续的这就要求检测器必须记住前一次的正确码及正确序列直到在连续的检测中所收到的每一位码都与预置数的对应码相同在检测过程中任何一位不相等都将回到初始状态重新开始检测如图1所示当一串待检测的串行数据进入检测器后若此数在每一位的连续检测中都与预置的密码数相同则输出A 否则仍然输出B。

图1 8位序列检测器逻辑图comb_outputsstate_inputs resetclkFSM:s_machineCOM next_state current_state PROCESS REG PROCESS图2 一般状态机结构图5.5 案例步骤(1) 按照状态机的设计流程,完成逻辑抽象到状态图表示等一系列流程,根据状态图设计出硬件描述语言代码,完成代码的输入,编译、综合,通过对报错信息的分析调试代码直到代码完全正确。

完成电路的仿真,观察仿真波形是否符合电路的逻辑功能要求。

(2) 完成电路的引脚锁定,分别将各输入引脚锁定到按键或者跳线上,时钟输入端锁定在开发试验系统的时钟输出引脚上,将计数器的输出通过译码电路连接到7段数码管上进行显示。

实验报告(计算机类)1 .了解VHDL 语言编程方法,学会熟练运用quartus 软件2 .了解如何使用状态机方法设计十三进制计数器二、内容与设计思想1.用状态机给出的状态转换图2.十三进制计数器引脚图三、使用环境WinXP 或Win7、quartusii 编程环境四、核心代码及调试过程——状态机方法设计十三进制计数器 ----------------------------------------------------开课学院及实验室:实验时间:一、实验目的年月日Iibraryieee;useieee.std_Iogic_1164.all;useieee.std_Iogic_arith.all;useieee.std_Iogic_unsigned.all ;entityh31isport(cp:instd_logic; -------------- clocksignaIq:outstd_Iogic_vector(3downtoO); ------------------------ stateoutput op:outstd_logic -------------- carryoutput);endh31;architecturert1ofh31istypestateis(sθ,s1,s2,s3,s4,s5,s6,s7,s8,s9t s10,s111s12); ----------------------------------------------------------------------- s tateasenumeration signaIpresentstate:state;signaInextstate:state;signaIqn:std_Iogic_vector(3downtoO);beginswiChtonextstate:Process(cp)beginifcp,eventandcp='1,thenpresentstate<=nextstate;endif;endp rocessswiChtonextstate;changestatemode:process(presentstate)begincasepresentstateiswhens θ=>nextstate<=s1;qn<="OOOΓ,;op<=,0';whens1=>nextstate<=s2;qn<="0010";op<=,0';whens2=>next state<=s3;qn<=,,001Γ,;op<=<0';whens3=>nextstate<=s4;qn<="0100”;op<=,0';whens4=>nextstate<=s5;qn<=,,010Γ';op<=,0';whens5=>nextstate<=s6;qn<="0110";op<=,0';whens6=>nextstate<=s7;qn<="011Γ,;op<=,0';whens7=>nextstate<=s8;qn<二"1000”;op<=,0,;whens8=>nextstate<=s9;qn<=,,100Γ,;op<=,0';whens9=>nextstate<=s10;qn<二“1010”;op<=,0';whens10=>nextstate<=s11;qn<="101Γ,;op<=,0';whens11=>nextstate<=s12;qn<=F100";op<=,0,;whens12=>nextstate<=s0;qn<="0000”;op<='Γ;endcase;endprocesschangestatemode;q<=qn;endrt1;五、总结六、附录(仿真结果)SimulationWaveforms Sinulfttionmod。

实验五有限状态机

0900210204 吴韦艳

一、实验目的:

本次实验通过Verilog硬件语言编写摩尔型有限状态机和米勒型有限状态机,掌握采用有限状态机产生各种控制信号的原理,熟悉如何选用合适的有限状态机进行电路设计,通过实验进一步了解原理图编辑方法和仿真方法。

二、实验要求:

1、利用Verilog硬件语言,参考提供的源程序,设计一个采用摩尔型有限状态机实现的

流水灯控制程序;

2、利用Verilog硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的

串行口发送程序;

3、利用Verilog硬件语言,参考提供的源程序,设计一个采用米勒型有限状态机实现的

串行口接收程序;

4、利用原理图编辑方法,将串行口发送和接收模块进行连接,实现完整的串行通信电路,并对该电路进行仿真。

三、实验内容

1、米勒型有限状态机实现的串行口发送源程序

module s_tx(clk,en,dain,txd);

input clk,en;

input[7:0] dain;

output txd;

reg [7:0] da_temp;

reg txd;

reg [3:0] state;

parameter swait=4'b0000,

star=4'b0001,

s1=4'b0010,

s2=4'b0011,

s3=4'b0100,

s4=4'b0101,

s5=4'b0110,

s6=4'b0111,

s7=4'b1000,

s8=4'b1001,

stop=4'b1010;

always @(posedge en)

da_temp<=dain;

always @(posedge clk)

if (!en)

begin

state<=swait;

txd<=1;

end

else

case(state)

swait: begin state<=star;txd<=1; end

star: begin state<=s1; txd<=0; end //状态转换s1: begin state<=s2; txd<=da_temp[7]; end

s2: begin state<=s3; txd<=da_temp[6]; end

s3: begin state<=s4; txd<=da_temp[5]; end

s4: begin state<=s5; txd<=da_temp[4]; end

s5: begin state<=s6; txd<=da_temp[3]; end

s6: begin state<=s7; txd<=da_temp[2]; end

s7: begin state<=s8; txd<=da_temp[1]; end

s8: begin state<=stop; txd<=da_temp[0]; end stop: begin state<=stop; txd<=1; end endcase

endmodule

2、米勒型有限状态机实现的串行口接收源程序module s_rx(clk,dain,daout);

input clk,dain;

output [7:0] daout;

reg [7:0] daout;

reg [7:0] da_temp;

reg [3:0] state;

parameter star=4'b0000,

s1=4'b0010,

s2=4'b0011,

s3=4'b0100,

s4=4'b0101,

s5=4'b0110,

s6=4'b0111,

s7=4'b1000,

s8=4'b1001,

stop=4'b1010;

always @(negedge clk)

case (state)

star: if (dain)

state<=star;

else

state<=s1; //数据开始位为0

s1:begin state<=s2; da_temp[7]<=dain; end //状态转换

s2:begin state<=s3; da_temp[6]<=dain; end

s3:begin state<=s4; da_temp[5]<=dain; end

s4:begin state<=s5; da_temp[4]<=dain; end

s5:begin state<=s6; da_temp[3]<=dain; end

s6:begin state<=s7; da_temp[2]<=dain; end

s7:begin state<=s8; da_temp[1]<=dain; end //8个状态

s8:begin state<=stop; da_temp[0]<=dain; end //数据结束位为1 stop:if (!dain)

state<=stop;

else

begin

state<=star;

daout<=da_temp;

end

endcase

Endmodule

3、由s_tx和s_rx组成的电路

4、对以上电路做波形仿真

5、状态机

6、实验总结

通过本次实验我掌握采用有限状态机产生各种控制信号的原理,熟悉如何选用合适的有限状态机进行电路设计,通过实验进一步了解了原理图编辑方法和仿真方法。