射频前端本振电路部分设计

- 格式:doc

- 大小:211.50 KB

- 文档页数:3

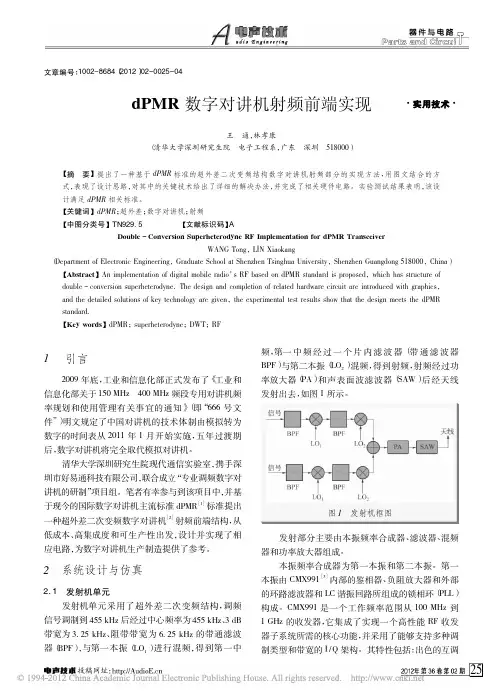

射频接收前端的ADS设计与仿真贾锋;杨瑞民【摘要】As an important part of the Radio Front(RF)signal analyzer, the RF receiver front-end plays a decisive role in the measurement of the RF signal. This paper builds one kind of 860~960 MHz RF receiver front-end system simulation platform of RF signal analyzer using the Advanced Design System(ADS)software. The pre-LNA is used to reduce system noise, and AGC is used to achieve a large dynamic range of the RF receiver front-end in the design. The gain, noise figure, sensitivity, dynamic range and other indicators of RF front-end of the design are calculated, and simulated by the software simulation tools. The simulations show that the RF front-end designed in the paper meets the requirements of the design.%射频接收前端作为射频信号分析仪的重要组成部分,对射频(RF)信号的测量起着决定性的作用。

使用ADS软件,构建了一种860~960 MHz的射频信号分析仪射频接收前端系统仿真平台。

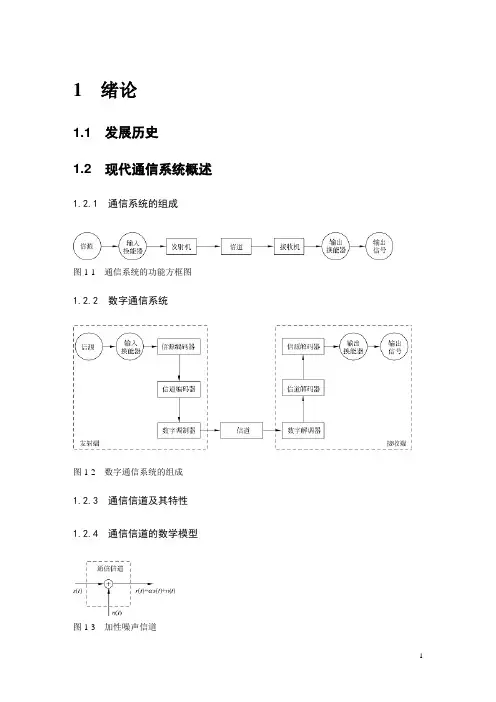

1 绪论1.1 发展历史1.2 现代通信系统概述1.2.1 通信系统的组成图1-1 通信系统的功能方框图1.2.2 数字通信系统图1-2 数字通信系统的组成1.2.3 通信信道及其特性1.2.4 通信信道的数学模型图1-3 加性噪声信道图1-4 带加性噪声的线性滤波信道图1-5 带加性噪声的线性时变滤波器1.3 射频电路在系统中的作用与地位图1-6 射频通信系统示意图图1-7 射频前端方框图1.4 射频电路与微波电路和低频电路的关系1.4.1 频段划分1.4.2 电路的寄生效应1.4.3 电路的设计考虑1.5 应用1.5.1 无线局域网图1-8 Prism Duette双频带收发机芯片组的总体结构图141.5.2 GSM1.5.3 WCDMA1.6 总结参考文献2 线性射频电路的基本特性和分析方法2.1 传输线图2-1 射频电路中常用的均匀传输线2.1.1 传输线波动方程图2-2 一小段传输线的等效电路2.1.2 终端接负载的无损传输线图2-3 以负载处为原点的坐标体系2.1.3 终端接特定负载的无损传输线的工作状态图2-4 短路传输线上电压、电流和输入阻抗的分布图图2-5 开路传输线上电压、电流和输入阻抗的分布图2.1.4 阻抗的周期性和倒置性2.1.5 微带线设计图2-6 微带线的几何结构图2-7 微带线的特性阻抗图2-8 微带线的有效介电常数2.2 Smith圆图2.2.1 阻抗圆图图2-9 阻抗圆图上的归一化阻抗2.2.2 Smith圆图上的反射系数和驻波系数图2-10 阻抗圆图2.2.3 导纳圆图图2-11 导纳圆图上的归一化导纳2.2.4 Smith圆图应用举例图2-12 例2.2的电路图图2-13 利用Smith圆图求解例2.2 2.3 双端口网络2.3.1 网络参量图2-14 双端口网络的电压和电流方向图2-15 双端口网络的入射波和反射波图2-16 S参数的测量2.3.2 网络的互联图2-17 双端口网络的串联图2-18 双端口网络的并联图2-19 双端口网络的串并联图2-20 双端口网络的并串联图2-21 双端口网络的级联2.3.3 信号流图分析法图2-22 信号流图分析法的简化规则图2-23 含电源和负载的双端口网络图2-24 用信号流图分析法分析双端口网络的简化过程2.4 射频电路中的无源分立集总参数元件图2-25 铝金属线归一化电流密度的横截面分布示意图图2-26 铝金属线横截面上的归一化电流密度分布随频率的变化(a=1mm)图2-27 金属铜和铝的趋肤深度随工作频率的变化图2-28 薄膜片上电阻图2-29 炭质电阻图2-30 高频电阻模型图2-31 炭质电阻的阻抗与频率的关系图2-32 表面贴封电容的内部结构图2-33 高频电容模型图2-34 实际电容的阻抗与频率的关系图2-35 高频电感\图2-36 高频电感模型图2-37 实际电感的阻抗与频率的关系2.5 总结参考文献习题图2-38 习题4图图2-39 习题7图图2-40 习题8图3 无源RLC网络和阻抗匹配3.1 无源RLC网络3.1.1 串联RLC网络图3-1 串联RLC网络图3-2 串联RLC网络的阻抗特性图3-3 串联RLC网络中电感储存的磁能、电容储存的电能以及回路储存的总能量随时间的变化情况图3-4 品质因子Q取不同值时回路阻抗的幅频特性和相频特性3.1.2 并联RLC网络图3-5 并联RLC网络图3-6 并联RLC网络的阻抗特性图3-7 品质因子QP取不同值时并联谐振回路阻抗的幅频特性和相频特性3.2 串并联阻抗等效互换图3-8 串并联RLC网络图3-9 电阻R和电抗X的串联形式和并联形式3.3 回路抽头时的阻抗变换图3-10 电感抽头和电容抽头的RLC谐振回路3.4 阻抗匹配图3-11 借以说明阻抗匹配概念的简单电路图3.4.1 L匹配图3-12 L匹配的电路结构图3-13 并/串联电感和电容的阻抗变化轨迹图3-14 利用Smith圆图来求解L匹配问题图3-15 L匹配网络图3-16 Smith圆图上的恒Qn圆3.4.2 T匹配和Pi匹配图3-17 T匹配网络图3-18 利用Smith圆图来设计T匹配网络图3-19 Pi匹配网络图3-20 利用Smith圆图来设计Pi匹配网络3.4.3 微带线匹配图3-21 微带线匹配网络图3-22 利用Smith圆图来设计微带线匹配网络图3-23 归一化阻抗zin=rin+jxin与电容所在位置之间的关系图3-24 更复杂的微带线匹配网络图3-25 全部由微带线组成的匹配网络3.5 总结参考文献习题图3-26 习题3图4 射频集成电路中的基本问题4.1 射频电路的性能度量4.1.1 功率增益和电压增益4.1.2 灵敏度和噪声系数图4-1 电阻的噪声模型4.1.3 线性度和动态范围图4-2 非线性4.1.4 系统设计4.2 射频电路仿真算法及商用仿真软件介绍4.2.1 SPICE模拟器应用于射频领域所遇到的限制4.2.2 射频电路仿真算法4.2.3 射频电路仿真工具4.3 CMOS射频集成电路实现的难点4.4 总结参考文献习题5 集成无源元件5.1 电阻图5-1 有拐角的电阻5.2 电容图5-2 MOS电容的理想C-V曲线图5-3 MIM电容的结构图5-4 三种互连线结构图5-5 “夹心”金属电容5.3 电感图5-6 射频集成电路中电感的典型应用5.3.1 片上平面螺旋型电感图5-7 片上平面螺旋型电感的结构图5-8 接地隔离层图5-9 片上平面螺旋型电感模型图5-10 焊盘的校准结构。

射频功放偏置电路设计需要考虑以下几个因素:

1.工作频率:偏置电路需要与功放的工作频率相匹配,以确保功放能够正常工作。

2.功率容量:偏置电路需要能够承受功放产生的热量和电流,以确保功放能够稳

定工作。

3.稳定性:偏置电路需要具有良好的稳定性,以确保功放的性能和可靠性。

4.线性度:偏置电路需要具有良好的线性度,以确保功放输出的信号质量。

5.易于调试和调整:偏置电路需要易于调试和调整,以便在不同的应用场景下都

能够获得最佳的性能。

基于以上因素,射频功放偏置电路设计可以采用以下几种方法:

1.分立元件法:使用独立的电子元件(如电阻、电容、电感等)搭建偏置电路。

这种方法虽然较为传统,但具有可靠性高、易于调整等优点。

2.集成电路法:使用集成电路芯片搭建偏置电路。

这种方法具有可靠性高、体积

小、易于集成等优点,但成本较高。

3.混合方法:结合分立元件法和集成电路法的方法,使用独立的电子元件搭建部

分电路,使用集成电路芯片搭建其他部分电路。

这种方法可以兼顾成本和性能。

在具体设计时,需要根据实际需求选择合适的方法,并考虑电路的拓扑结构、元件参数、散热设计等因素。

同时,还需要进行仿真和测试,以验证设计的可行性和性能指标。

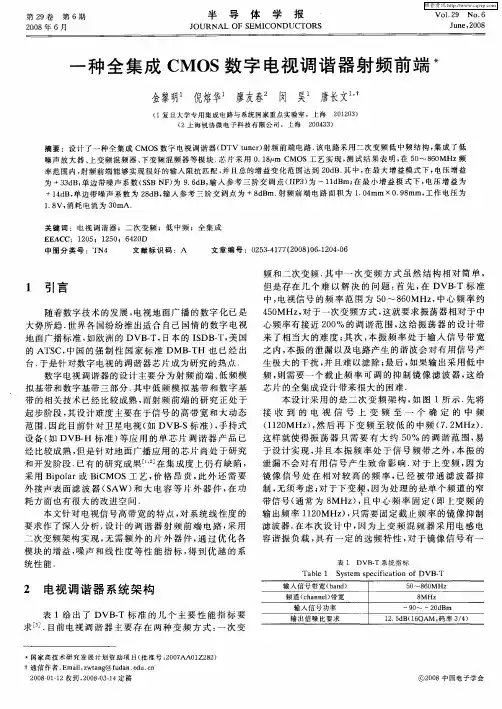

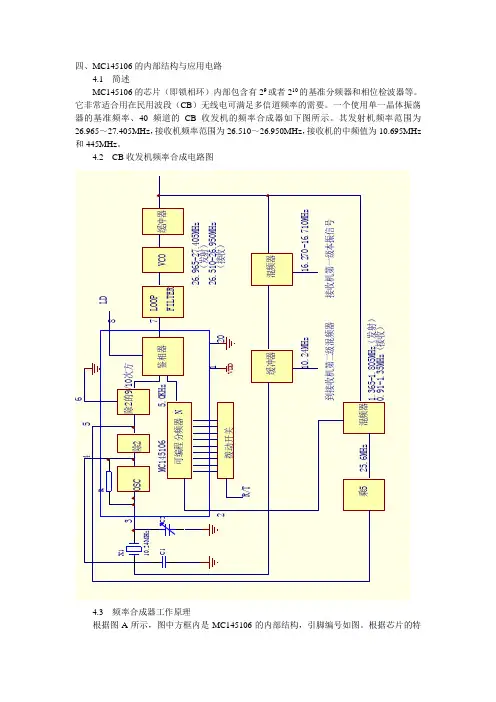

四、MC145106的内部结构与应用电路4.1 简述MC145106的芯片(即锁相环)内部包含有29或者210的基准分频器和相位检波器等。

它非常适合用在民用波段(CB )无线电可满足多信道频率的需要。

一个使用单一晶体振荡器的基准频率、40频道的CB 收发机的频率合成器如下图所示。

其发射机频率范围为26.965~27.405MHz ,接收机频率范围为26.510~26.950MHz ,接收机的中频值为10.695MHz 和445MHz 。

4.2 CB 收发机频率合成电路图X 110.24M H zC 1C 2RO S C除2除2的9/10次方鉴相器L O O PF I L T E RV C O缓冲器混频器混频器缓冲器乘5拨动开关可编程分频器接收机第一级本振信号到接收机第二级混频器16.270-16.710M H z10.24M H z25.6M H z1.365-1.805M H z (发射)0.91-1.35M H z (接收)26.510-26.950M H z (接收)(发射)26.965-27.405M H z L DV D DR /T5.0K H zM C 1451061234567820N4.3 频率合成器工作原理根据图A 所示,图中方框内是MC145106的内部结构,引脚编号如图。

根据芯片的特性,其不能自己产生基准频率,因此电路设计中通过一个晶体振荡器X 1产生10.24MHz 的基准频率,使MC145106芯片内部的振荡器OSC 产生同大小的频率,再将基准频率经过2分频,从5脚输出5.12MHz 到5倍放大器,其内部继续进行分频选择。

当6脚接低电平,5.12MHz 经过29分频,输出5.0KHz 到芯片内部的鉴相器,与可编程分频器的输出频率f IN /N 相比较(N 为可编程分频倍数,可通过拨动开关手动控制),当f IN /N 小于基准频率时,7脚输出高电平,经过低通滤波,迫使压控振荡器VCO 产生频率,输出经过混频等电路到达可编程分频器,通过鉴相器继续进行比较,若f IN /N 仍小于基准频率,于是7脚仍输出高电平,同样的原理,迫使VCO 频率继续增加,直到f IN /N 等于基准频率,琐相环锁定,8脚输出“1”锁定信号,所需频率即合成。

混频器射频和本振对地短路一、混频器的基本原理混频器是一种非线性电路,其主要作用是将两个不同频率的信号进行混合,产生新的频率组合。

混频器的基本原理是利用二极管等非线性元件对输入信号进行非线性变换,从而产生新的频率组合。

二、射频和本振对地短路射频和本振对地短路是混频器中常见的一种技术手段。

其目的是将射频和本振信号分别与地面连接,从而达到隔离、抑制杂散和提高混频效果等目的。

1. 射频对地短路射频对地短路指将输入到混频器中的射频信号与地面连接。

这样做可以防止信号反射和杂散干扰,并且可以提高混频效果。

2. 本振对地短路本振对地短路指将输入到混频器中的本振信号与地面连接。

这样做可以防止信号反射和杂散干扰,并且可以提高混频效果。

三、如何实现射频和本振对地短路实现射频和本振对地短路需要使用相应的元件和技术手段。

常见的实现方法包括:1. 通过电容将射频和本振信号与地面连接这是一种简单而常见的实现方法,可以使用电容将射频和本振信号与地面连接。

具体实现方式包括串联电容、并联电容等。

2. 通过变压器将射频和本振信号与地面连接这是一种更加精确和可靠的实现方法,可以使用变压器将射频和本振信号与地面连接。

具体实现方式包括中心点接地变压器、差模变压器等。

3. 通过PCB布局优化实现对地短路这是一种常见而有效的实现方法,可以通过PCB布局优化来实现对地短路。

具体实现方式包括增加接地铺铜、减小线路长度、合理布置元件等。

四、射频和本振对地短路的注意事项在进行射频和本振对地短路时需要注意以下事项:1. 尽可能选择低阻抗接口在进行射频和本振对地短路时需要选择低阻抗接口,以保证信号传输效果。

2. 防止信号反射在进行射频和本振对地短路时需要防止信号反射,以避免干扰和降低混频效果。

可以采用匹配网络等技术手段来实现。

3. 优化PCB布局在进行射频和本振对地短路时需要优化PCB布局,以提高信号传输效果和抑制杂散干扰。

可以采用增加接地铺铜、减小线路长度、合理布置元件等方法来实现。

电磁兼容与射频技术作业指导书第1章电磁兼容基础理论 (3)1.1 电磁兼容概述 (3)1.2 电磁兼容基本概念 (4)1.2.1 电磁干扰(Electromagnetic Interference, EMI) (4)1.2.2 电磁敏感性(Electromagnetic Susceptibility, EMS) (4)1.2.3 电磁兼容设计 (4)1.2.4 电磁兼容三要素 (4)1.3 电磁兼容测试标准与法规 (4)1.3.1 国际电磁兼容测试标准 (4)1.3.2 我国电磁兼容测试标准 (4)1.3.3 电磁兼容法规 (4)第2章射频技术基础 (5)2.1 射频信号特性 (5)2.1.1 频率特性 (5)2.1.2 辐射特性 (5)2.1.3 耦合特性 (5)2.1.4 衰减特性 (5)2.2 射频电路设计原理 (5)2.2.1 射频放大器设计 (5)2.2.2 混频器设计 (5)2.2.3 滤波器设计 (5)2.2.4 阻抗匹配设计 (6)2.3 射频天线技术 (6)2.3.1 天线类型 (6)2.3.2 天线特性 (6)2.3.3 天线设计 (6)第3章电磁干扰源及其抑制 (6)3.1 电磁干扰源分类 (6)3.1.1 静电干扰 (6)3.1.2 磁场干扰 (7)3.1.3 电磁辐射干扰 (7)3.1.4 电快速脉冲干扰 (7)3.2 电磁干扰抑制技术 (7)3.2.1 静电干扰抑制 (7)3.2.2 磁场干扰抑制 (7)3.2.3 电磁辐射干扰抑制 (7)3.2.4 电快速脉冲干扰抑制 (7)3.3 电磁干扰滤波器设计 (7)3.3.1 选择合适的滤波器类型 (8)3.3.2 确定滤波器参数 (8)3.3.3 优化滤波器布局 (8)3.3.4 选择合适的滤波器材料 (8)3.3.5 考虑滤波器安装方式 (8)3.3.6 测试与优化 (8)第4章电磁兼容性分析与评估 (8)4.1 电磁兼容性分析原理 (8)4.1.1 电磁干扰(EMI)分析原理 (8)4.1.2 电磁抗干扰(EMS)分析原理 (8)4.2 电磁兼容性评估方法 (9)4.2.1 理论分析方法 (9)4.2.2 模拟仿真方法 (9)4.2.3 实验测试方法 (9)4.3 电磁兼容性测试与测量 (9)4.3.1 测试场地与设备 (9)4.3.2 测试标准与规范 (9)4.3.3 测试流程与方法 (10)4.3.4 测试结果分析与应用 (10)第5章射频前端设计与优化 (10)5.1 射频前端概述 (10)5.2 射频放大器设计 (10)5.2.1 射频放大器类型 (10)5.2.2 射频放大器设计原则 (10)5.2.3 射频放大器设计方法 (11)5.3 射频滤波器设计 (11)5.3.1 射频滤波器类型 (11)5.3.2 射频滤波器设计原则 (11)5.3.3 射频滤波器设计方法 (11)5.4 射频阻抗匹配技术 (11)5.4.1 射频阻抗匹配原理 (11)5.4.2 射频阻抗匹配设计方法 (11)5.4.3 射频阻抗匹配技术的应用 (12)第6章射频接收与发射技术 (12)6.1 射频接收技术 (12)6.1.1 射频接收原理 (12)6.1.2 射频接收电路设计 (12)6.1.3 射频接收功能指标 (12)6.2 射频发射技术 (12)6.2.1 射频发射原理 (12)6.2.2 射频发射电路设计 (12)6.2.3 射频发射功能指标 (12)6.3 射频调制与解调 (13)6.3.1 射频调制技术 (13)6.3.2 射频解调技术 (13)6.3.3 调制与解调电路设计 (13)第7章电磁兼容抗干扰技术 (13)7.1 电磁屏蔽技术 (13)7.1.1 电磁屏蔽原理 (13)7.1.2 电磁屏蔽材料 (13)7.1.3 电磁屏蔽设计 (13)7.2 电磁吸收技术 (13)7.2.1 电磁吸收原理 (13)7.2.2 电磁吸收材料 (13)7.2.3 电磁吸收结构设计 (14)7.3 电磁兼容接地技术 (14)7.3.1 接地原理 (14)7.3.2 接地系统设计 (14)7.3.3 接地装置及其应用 (14)第8章射频集成电路设计 (14)8.1 射频集成电路概述 (14)8.1.1 射频集成电路基本概念 (14)8.1.2 射频集成电路分类 (14)8.1.3 射频集成电路在射频系统中的应用 (15)8.2 射频集成电路设计流程 (15)8.2.1 需求分析 (15)8.2.2 电路拓扑选择 (15)8.2.3 电路参数设计 (15)8.2.4 电路仿真与优化 (15)8.2.5 版图设计 (15)8.2.6 设计验证与测试 (15)8.3 射频集成电路版图设计 (16)8.3.1 版图设计原则 (16)8.3.2 版图设计步骤 (16)第9章电磁兼容与射频技术的应用案例 (16)9.1 移动通信系统中的应用 (16)9.2 无线局域网中的应用 (17)9.3 蓝牙与物联网中的应用 (17)第10章电磁兼容与射频技术的发展趋势 (18)10.1 5G通信技术对电磁兼容与射频技术的影响 (18)10.2 新型电磁兼容与射频技术的研发 (18)10.3 未来电磁兼容与射频技术的发展方向 (19)第1章电磁兼容基础理论1.1 电磁兼容概述电磁兼容(Electromagnetic Compatibility, EMC)是指电子设备或系统在电磁环境中能正常工作并不干扰其他设备的能力。

1.1本振电路

1.1.1本振电路框图

框图如下图所示,时钟源部份,单片机控制部份、和本振电路部份三大块,由于有三级混频,本振电路必须提供三个本振频率,第一本振频率是可调的,第二、三本振频率则是固定的。

图1本振电路框图

1.1.2时钟源

时钟源分为外部参考时钟源和内部时钟源,当使用外部参考时钟源时,内部时钟源自动断开,外部时钟源主要的作用就是为了同步,一般是在双通道或多通道测向时需要采用。

外部时钟源的精度稳定度就无法控制。

不作双通道测向时,则主要是靠内部时钟源提供时钟基准。

内部时钟源采用高稳定度时钟,稳定度为10-9-10-7。

同时,也向外提供10MHz的时钟输出。

如下图:

图 2时钟源框图

1.1.3本振电路及噪声分析

接收机本振源采用了DDS+PLL混合合成的技术,如错误!未找到引用源。

所示。

图 3 接收机本振源原理

这个框图只是一个本振的大致框图,具体电路应该根据本方案的要求对电路作相应的改动,以适应要求。

由图可见,参考频率为10㎒,高速DDS根据需要产生所需要的信号,经过滤波器组初步滤除谐波杂散,送入后续的PLL做激励信号。

VCO产生的信号经过合适的分频与激励信号比较,锁定频率和相位。

接收机的相位噪声指标主要取决于本振相位噪声,这个方案其基础相位噪声为参考源相位噪声,而输出信号在此基础上有一定的恶化,恶化程度则主要取决于PLL本身的噪声+分频器分频系数带来的噪声恶化+DDS噪声恶化。

在选取低噪声的鉴频鉴相器和VCO器件后,系统的主要噪声恶化就取决于后两者。

分频器分频系数若为N,其带来的噪声恶化为20Log(N),若M为DDS输出频率与参考频率

比,则DDS的噪声恶化等于20Log(M)。

如当M=0.5,N为50时,此时总噪声恶化约为30dB,若要实现本振输出达到-120dBc/Hz@10㎑的相位噪声指标,则要求参考信号源至少达到-150dBc/Hz@10㎑的相位噪声指标,采用恒温晶振制作的参考源即可满足要求。

采用DDS+PLL的方式,也保证了本振源频率切换时间足够迅速。

经测试切换时间约1㎳左右,完全满足快速扫频的要求。

问题在于切换时间1ms可能还不够,能否做到<0.5ms以内,越小越好,这对于提高整个接收机的扫描速度是很有好处的。

需要弄清楚的问题:(只有一个问题)

1.看懂上面的内容,把图3的框图变成具体的电路。

由于三个本振的频率不同,所以

三个本振电路可能会有差异???输出阻抗为50欧,输出功率为7dBm。

2.图2中的外部时钟和内部时钟的选择电路,要求是当有外部时钟信号进入时,自动

断开内部时钟而接入外部时钟,否则使用内部时钟,根据这个要求设计电路。

内部

标准时钟源为外购。

3.图2标明了参考时钟的输出,增加一个输出缓冲器,输出阻抗为50欧,输出功率

不低于3dBm.

4.图3中,控制器接到指令到VCO作出频率改变的稳态时间约1ms,能否弄清楚图3

中的那个环节对这1ms贡献最大?能否改善?如何改善?。

因为这个指标越小就意

味着扫描速度越快,能否提高到100us以内?(可能的措施:通过提高关键模块的

供电电压是不是可以加快其反应速度?)。