时序计算和Cadence仿真结果的运用

- 格式:pdf

- 大小:460.72 KB

- 文档页数:4

基于Cadence的DDR源同步时序仿真研究作者:唐万明范朝元来源:《现代电子技术》2014年第08期摘要:以DDR高速总线为例,通过对DDR源同步时序的分析,以此提供一个高速PCB 设计中高速总线时序完整的分析方法,从而使设计中的高速总线频率达到真正高速度和大的时序裕量。

在此创新地在时序分析过程打破纯粹的理论公式推导,结合仿真分析软件,采用理论计算和仿真图形相结合的方法,使时序分析变得更加简化和直观。

这种分析方法在其他高速总线分析中也得到广泛应用,并在实践中得到有效验证。

关键词:时序完整性;建立时间;保持时间;飞行时间;缓冲延时中图分类号: TN710⁃34 文献标识码: A文章编号: 1004⁃373X(2014)08⁃0075⁃04 Research of DDR source synchronization time⁃sequence simulation based on CadenceTANG Wan⁃ming, FAN Chao⁃yuan(Chongqing Jinmei Communication Co.,Ltd., Chongqing 400030, China)Abstract:Taking high⁃speed DDR bus as an example, a complete time⁃sequence analysis method about high⁃speed bus in high⁃speed PCB design is proposed according to the DDR source synchronization time⁃sequence analysis to enable the frequency of high⁃speed bus in design to achieve really high⁃speed and large time⁃sequence margin. The innovation of this paper lies in the time⁃sequence analysis process, which breaks the purely theoretical formula derivation and makes time⁃sequence analysis become more simple and intuitive by combining with simulation analysis software and adopting the method of combining theoretical calculation with simulation graphics. This analysis method has been widely used and well proven in practice in other high⁃speed bus analyses.Keywords: time⁃sequence integrity; setup time; hold time; flight time; buffer delay在高速PCB设计中,从广义的角度来看,信号完整性包括时序完整性,时序分析是信号完整性分析中最为复杂的部分[1]。

Cadence Allegro Bus Simulation总线仿真——源同步分析孙海峰随着电子设计的快速进步,总线速度的提高在PCB上的实现越来越难,这样就催生了新的不受时钟制约的时序系统,即源同步时序系统。

源同步时序系统最大的优点,就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

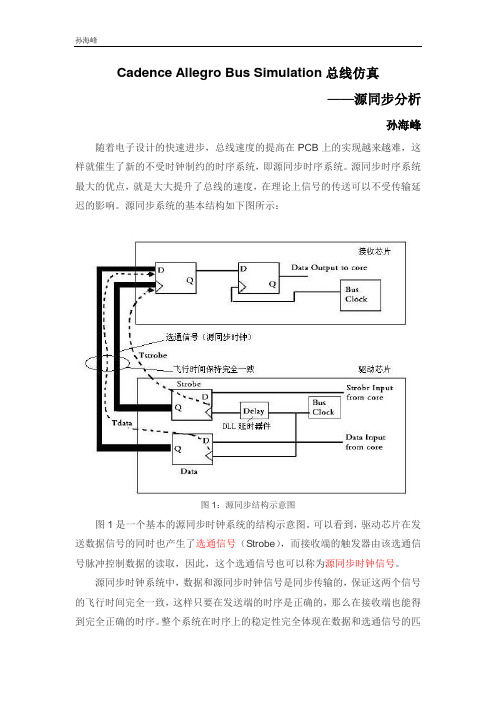

源同步系统的基本结构如下图所示:图1:源同步结构示意图图1是一个基本的源同步时钟系统的结构示意图。

可以看到,驱动芯片在发送数据信号的同时也产生了选通信号(Strobe),而接收端的触发器由该选通信号脉冲控制数据的读取,因此,这个选通信号也可以称为源同步时钟信号。

源同步时钟系统中,数据和源同步时钟信号是同步传输的,保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。

整个系统在时序上的稳定性完全体现在数据和选通信号的匹配程度上,包括传输延迟的匹配,器件性能的匹配等等,只要两者完全匹配,那么我们就可以保证系统时序的绝对正确,。

然而,在实际的PCB设计中,我们往往不可能观察到总线与选通信号的匹配程度,我们就需要借助新的设计仿真软件,来实现这个功能,就此Cadence 顺应电子设计的大潮流,推出了DDR总线仿真工具Bus Simulation用以进行源同步分析仿真。

那么Cadence软件是如何来实现PCB的源同步时序分析的呢,接下来,我将详细阐述这个过程。

1、进入Cadence Allegro SI仿真界面,如下图所示:2、点击OK进入SI仿真界面,并完成SI仿真基本流程,包括:模型库添加、模型赋予、DC网络值定义等等。

图2:模型库添加与管理图3:模型赋予图4:DC直流网络定义3、完成上述SI仿真基本步骤后,就可以开始进行SI分析,包括:反射、串扰、EMI、通道分析等等,这里就不再赘述。

这里主要介绍的是新的PCB源同步时序分析工具Bus Simulation,该总线仿真针对DDR的总线进行源同步时序分析。

引言:随着现代设计技术的逐渐深入,所采用的信号时钟频率的提高以及上升或下降时间的缩短,设计意图也变得较难以实现。

如通过一般的传统设计流程,设计出产品后的效果通常难以达到当初的设计目标,这正是将高速仿真分析加入传统设计流程的契机。

对单板或系统进行高速分析不仅有利于在设计初期发现和解决潜在问题、缩短产品上市时间、降低产品成本、提高产品质量,更是实现设计即正确(Correct by Design:简称CBD)这一终极目标的有力保证。

Cadence公司的设计软件Allegro(或者SpecctraQUEST)就是可以实现高速信号仿真分析的软件。

本文对利用Allegro(或者SpecctraQUEST)进行高速信号仿真分析的过程和每一步操作进行了详细的说明,有助于设计人员对高速信号仿真分析的理解和普及,进一步提高公司的设计水平。

Cadence仿真步骤第一步进行SI仿真的PCB板图的准备仿真前的准备工作主要包括以下几点:1、仿真板的准备●原理图设计;● PCB封装设计;● PCB板外型边框(Outline)设计,PCB板禁止布线区划分(Keepouts);●输出网表(如果是用CADENCE的Concept HDL设计的原理图,可将网表直接Export 到brd文件中;如果是用PowerPCB设计的板图,要将其转换到allegro中的板图,其操作见附录一的说明);●器件预布局(Placement):将其中的关键器件进行合理的预布局,主要涉及相对距离、抗干扰、散热、高频电路与低频电路、数字电路与模拟电路等方面;● PCB板布线分区(Rooms):主要用来区分高频电路与低频电路、数字电路与模拟电路以及相对独立的电路。

元器件的布局以及电源和地线的处理将直接影响到电路性能和电磁兼容性能;2、关键器件资料及模型的准备●收集器件的IBIS模型(网上下载、向代理申请、修改同类型器件的IBIS模型等)●收集器件的关键参数,如Tco、Tsetup、Tholdup等及系统有关的时间参数Tclock、Tskew、Tjitter●对IBIS模型进行整理、检查、纠错和验证(该步骤可通过使用一些独立的小软件进行,也可利用整合到Cadence 中的模块进行,具体步骤见下面第二步)。

时序计算和Cadence仿真结果的运用时序计算和Cadence仿真结果的运用时间:2007-06-25 来源: 作者:余昌盛刘忠亮摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。

一、前言通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在cadence仿真中,我们也获得了一系列的仿真结果,怎样把仿真结果正确的运用到公式中,仿真结果的具体含义是什么,是我们正确使用Cadence仿真工具的关键。

下面对时序计算公式和仿真结果进行详细分析。

二.时序关系的计算电路设计中的时序计算,就是根据信号驱动器件的输出信号与时钟的关系(Tco——时钟到数据输出有效时间)和信号与时钟在PCB上的传输时间(Tflytime)同时考虑信号驱动的负载效应、时钟的抖动(Tiitter)、共同时钟的相位偏移(Tskew)等,从而在接收端满足接收器件的建立时间(Tsetup)和保持时间(Thold)要求。

通过这些参数,我们可以推导出满足建立时间和保持时间的计算公式。

时序电路根据时钟的同步方式的不同,通常分为源同步时序电路(Source-synchronous timing)和共同时钟同步电路(common-clock timing)。

这两者在时序分析方法上是类似的,下面以源同步电路来说明。

源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。

图1中,时钟信号是由CPU驱动到SDRAM方向的单向时钟,数据线Data是双向的。

图2是信号由CPU向SDRAM驱动时的时序图,也就是数据与时钟的传输方向相同时的情况。

图中参数解释如下:•Tft_clk:时钟信号在PCB板上的传输时间;•Tft_data:数据信号在PCB板上的传输时间;•Tcycle:时钟周期•Tsetup':数据到达接收缓冲器端E1时实际的建立时间;•Thold':数据到达接收缓冲器端E1时实际的保持时间;•Tco_max/T co_min:时钟到数据的输出有效时间。

第1篇一、实验目的1. 理解时序电路的基本概念和组成,掌握时序电路的设计方法和分析方法。

2. 掌握计数器、寄存器、移位寄存器等时序电路的应用。

3. 熟悉FPGA开发环境,能够使用Quartus II设计工具进行时序电路的设计和仿真。

二、实验原理时序电路是数字电路中的一种重要电路,它能够根据输入信号的变化,产生一系列有序的输出信号。

时序电路主要由触发器、逻辑门和时钟信号组成。

1. 触发器:触发器是时序电路的基本单元,具有存储一个二进制信息的功能。

常见的触发器有D触发器、JK触发器、T触发器等。

2. 逻辑门:逻辑门用于实现基本的逻辑运算,如与、或、非、异或等。

3. 时钟信号:时钟信号是时序电路的同步信号,用于控制触发器的翻转。

三、实验内容1. 计数器设计(1)设计一个3位同步二进制加计数器。

(2)设计一个3位同步二进制减计数器。

2. 寄存器设计使用74LS74触发器设计一个双向移位寄存器。

3. 移位寄存器设计使用74LS74触发器设计一个单向移位寄存器。

4. 环形计数器设计使用74LS74触发器设计一个环形计数器。

5. 可控分频器设计使用Verilog HDL语言设计一个可控分频器,实现时钟信号的分频功能。

四、实验步骤1. 使用Quartus II设计工具创建工程,并添加所需的设计文件。

2. 根据实验原理,编写时序电路的Verilog HDL代码。

3. 编译代码,并生成测试平台。

4. 在测试平台上进行仿真,验证时序电路的功能。

5. 将设计下载到FPGA,进行硬件实验。

6. 记录实验结果,分析实验现象。

五、实验结果与分析1. 计数器实验结果(1)3位同步二进制加计数器:按照时钟信号的变化,计数器能够从000计数到111。

(2)3位同步二进制减计数器:按照时钟信号的变化,计数器能够从111减到000。

2. 寄存器实验结果使用74LS74触发器设计的双向移位寄存器,能够实现数据的左移和右移功能。

3. 移位寄存器实验结果使用74LS74触发器设计的单向移位寄存器,能够实现数据的左移功能。

电子电路的仿真与测试方法电子电路的仿真与测试是电子工程领域中非常重要的一部分。

通过仿真与测试,工程师可以预测和评估电子电路在实际运行中的性能,发现和解决潜在的问题。

本文将介绍电子电路的仿真与测试方法,以及实施这些方法的步骤。

一、仿真方法1. 数学仿真:通过数学建模,使用计算机软件模拟电路的工作原理和性能。

常用的数学仿真工具包括MATLAB、Simulink和PSPICE等。

使用数学仿真方法可以快速评估电路的性能,并进行参数优化。

2. 电路仿真:通过使用电路仿真软件,如CircuitMaker、Multisim、LTspice等,可以将电子电路的元件和拓扑结构输入到软件中,通过执行仿真操作,模拟电路的工作情况。

电路仿真可以帮助工程师验证电路设计的正确性,并发现电路中的问题。

3. 时序仿真:对于数字电路或时序相关的电路,时序仿真非常重要。

通过时序仿真,可以模拟电子电路中的时钟信号、时序逻辑等情况,评估电路的时序性能。

常用的时序仿真工具包括ModelSim、Xilinx ISE等。

二、测试方法1. 实验室测试:通过实验室中的仪器设备,直接对电子电路进行测试。

常用的测试方法包括使用示波器、信号发生器、频谱分析仪等进行信号采集和分析。

实验室测试可以提供准确的电路参数和性能数据。

2. 无屏蔽测试:对于微弱信号或高频信号测试,需要进行无屏蔽测试。

无屏蔽测试可以消除外部干扰对测试结果的影响。

常用的无屏蔽测试方法包括开路测试、短路测试和50欧姆测试等。

3. PCB布线测试:在电子电路设计中,PCB布线是一个关键环节。

通过使用PCB测试仪器,可以检查电子电路在PCB布线中的连接是否正确,是否存在导通和短路等问题。

常用的PCB测试仪器包括针床、触探卡等。

三、实施步骤1. 确定仿真或测试的目的和需求。

根据电子电路的设计要求和性能要求,确定仿真或测试的目标。

2. 收集电路参数和元件模型。

收集所需的电路元件参数和模型,保证仿真或测试的准确性。

Cadence仿真介绍第一部分:仿真流程第二部分:IBIS模型IBIS模型和SPICE模型比较:SPICE模型:(1)电压/电流/时间等关系从器件图形、材料特性得来,建立在低级数据的基础上(2)每个buffer中的器件分别描述/仿真(3)仿真速度很慢(4)包含芯片制造工艺信息IBIS模型:(1)电压/电流/时间关系建立在IV/VT数据曲线上(2)没有包括电路细节(3)仿真速度快,是SPICE模型的25倍以上(4)不包含芯片内部制造工艺信息基于上述原因,对于在系统级的设计,我们更倾向于使用IBIS模型。

目前IBIS主要使用的有V1.1,V2.1,V3.2及V4.0等版本。

模型结构如下图:C_pkg,R_pkg,L_pkg为封装参数;C_comp为晶片pad电容;Power_Clamp,GND_Clamp 为ESD结构的V/I曲线。

输出模型比输入模型多一个pull-up,pull-down的V/T曲线。

Cadence的model integrity工具负责对IBIS模型进行语法检查、编辑以及进行DML格式转换。

Cadence仿真不直接使用IBIS模型,而必须先把IBIS转换成DML。

<实例操作演示>第三部分:电路板设置电路板设置包括:(1)叠层设置;(2)DC电压设置;(3)器件设置;(4)模型分配;上述步骤可以通过setup advisor向导设置。

1,叠层设置2,DC电压设置3,器件设置4,模型分配电阻、电容、电感等无源器件的模型可以通过建立ESPICE模型来获得。

<实例操作演示>第四部分:设置仿真参数模型分配完成后,就可以进行仿真了。

在进行仿真之前,需要对仿真的参数进行设置。

Pulse cycle count:通过指定系统传输的脉冲数目来确定仿真的持续时间。

Pulse Clock Frequency:确定仿真中用来激励驱动器的脉冲电压源的频率。

Pulse Duty cycle:脉冲占空比。

cadence原理图仿真

在进行Cadence原理图仿真时,我们需要注意以下几点,以确保仿真结果的准确性和可靠性:

1. 确认所使用的元件符合仿真要求,并正确地添加到原理图中。

这包括在仿真库中选择合适的元件模型,并将其与其他元件正确地连接起来。

2. 确认仿真的电源和接地连接正确无误。

确保电源和地线的连接不会导致任何不良影响,如电压下降或噪声干扰。

3. 设置仿真参数,如仿真时间、仿真步长等。

根据所需的仿真精度和仿真效率,选择适当的仿真参数。

4. 进行信号源的设置。

这包括选择合适的信号源类型(如AC

信号、脉冲信号等)、设置信号源的频率和振幅等参数。

5. 添加测量器件,以便在仿真过程中监测所需的电压或电流。

这些测量器件可以是电压表、电流表或示波器等。

6. 设置仿真分析类型。

根据需要进行直流分析、交流分析或者是时域分析等。

选择适当的仿真分析类型以获得所需的结果。

7. 运行仿真并分析结果。

运行仿真过程,等待仿真完成后,通过分析仿真结果来获取我们所需的电压、电流或其他信号参数。

通过遵循以上步骤,我们可以在Cadence中进行原理图仿真,并获取准确可靠的仿真结果,以验证电路设计的正确性和性能。

2006·9·http://www.cicmag.com(总第88期)ChinalntegratedCircult一.前言通常我们在时序仿真中,首先通过时序计算公式得到数据信号与时钟信号的理论关系,在Ca-dence仿真中,我们也获得了一系列的仿真结果,怎样把仿真结果正确的运用到公式中,仿真结果的具体含义是什么,是我们正确使用Cadence仿真工具的关键。

下面对时序计算公式和仿真结果进行详细分析。

二.时序关系的计算电路设计中的时序计算,就是根据信号驱动器件的输出信号与时钟的关系(Tco———时钟到数据输出有效时间)和信号与时钟在PCB上的传输时间(Tflytime)同时考虑信号驱动的负载效应、时钟的抖动(Tjitter)、共同时钟的相位偏移(Tskew)等,从而在接收端满足接收器件的建立时间(Tsetup)和保持时间(Thold)要求。

通过这些参数,我们可以推导出满足建立时间和保持时间的计算公式。

时序电路根据时钟的同步方式的不同,通常分为源同步时序电路(Source-synchronoustiming)和共同时钟同步电路(common-clocktiming)。

这两者在时序分析方法上是类似的,下面以源同步电路来说明。

源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。

图1中,时钟信号是由CPU驱动到SDRAM方向的单向时钟,数据线Data是双向的。

图2是信号由CPU向SDRAM驱动时的时序图,也就是数据与时钟的传输方向相同时的情况。

中兴通讯康讯研究所EDA设计部余昌盛刘忠亮时序计算和Cadence仿真结果的运用摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest时序仿真方法的分析,推导出了使用SPECCTRAQuest进行时序仿真时的计算公式,并对公式的使用进行了说明。

关键词:时序仿真源同步时序电路时序公式图1图257图中参数解释如下:■Tft_clk:时钟信号在PCB板上的传输时间;■Tft_data:数据信号在PCB板上的传输时间;■Tcycle:时钟周期■Tsetup’:数据到达接收缓冲器端口时实际的建立时间;■Thold’:数据到达接收缓冲器端口时实际的保持时间;■Tco_max/Tco_min:时钟到数据的输出有效时间。

由图2的时序图,我们可以推导出,为了满足接收芯片的Tsetup和Thold时序要求,即Tsetup’>Tsetup和Thold’>Thold,所以Tft_clk和Tft_data应满足如下等式:Tft_data_min>Thold-Tco_min+Tft_clk(公式1)Tft_data_max<Tcycle-Tsetup-Tco_max+Tft_clk(公式2)当信号与时钟传输方向相反时,也就是图1中数据由SDRAM向CPU芯片驱动时,可以推导出类似的公式:Tft_data_min>Thold-Tco_min-Tft_clk(公式3)Tft_data_max<Tcycle-Tsetup-Tco_max-Tft_clk(公式4)如果我们把时钟的传输延时Tft_clk看成是一个带符号的数,当时钟的驱动方向与数据驱动方向相同时,定义Tft_clk为正数,当时钟驱动方向与数据驱动方向相反时,定义Tft_clk为负数,则公式3和公式4可以统一到公式1和公式2中。

三.Cadence的时序仿真在上面推导出了时序的计算公式,在公式中用到了器件手册中的Tco参数,器件手册中Tco参数的获得,实际上是在某一种测试条件下的测量值,而在实际使用上,驱动器的实际负载并不是手册上给出的负载条件,因此,我们有必要使用一种工具仿真在实际负载条件下的信号延时。

Cadence提供了这种工具,它通过仿真提供了实际负载条件下和测试负载条件下的延时相对值。

我们先来回顾一下CADENCE的仿真报告形式。

仿真报告中涉及到三个参数:FTSmode、SwitchDelay和SettleDelay。

其中Cadence时序仿真的结果是通过SwitchDelay和SettleDelay两个参数反映出来的。

在解释FTSmode、SwitchDelay和SwitchDelay前先解释一下BufferDelay曲线的含义。

BufferDelay曲线是Cadence仿真器断开实际负载,带上驱动芯片器件手册提供的测试负载条件下获得的一条曲线。

测试负载是在IBIS仿真模型库中设置的。

Cadence仿真报告中的延时测量是以BufferDelay为基准曲线,以VMeasure为起始测量点获得的相对延时值。

FTSmode:定义了当前仿真驱动器的特性,分为Fast、Type和Slow。

该三种特性是在IBIS模型中定义的,Fast是驱动器沿最快的模式,Slow是驱动器沿最慢的模式,从而定义了驱动器在正常工作条件下的两种极限特性。

SwitchDelay:定义为SwitchDelayFall和SwitchDelayRise两者的最小值。

图3给出了SwitchDelayFall和SwitchDelayRise的图形解释。

SwitchDelayFall:是从BufferDelay下降沿的Vmeasure点开始到接收波形下降曲线第一次穿过高电平阈值时的延时值。

SwitchDelayRise:是从BufferDelay上升沿的Vmeasure点开始到接收波形上升曲线第一次穿过低电平阈值时的延时值。

SettleDelay:是SettleDelayFall和SettleDelayRise两者的最大值。

图3给出了SettleDelayFall和Set-tleDelayRise的图形解释。

SettleDelayFall:是从BufferDelay下降沿的Vmeasure点开始到接收波形下降曲线最后一次穿过低电平阈值时的延时值。

SettleDelayRise:是从BufferDelay上升沿的58(总第88期)http://www.cicmag.com2006·9·http://www.cicmag.com(总第88期)ChinalntegratedCircultVmeasure点开始到接收波形上升曲线最后一次穿过高电平阈值时的延时值。

从SwitchDelay和SettleDelay的定义我们可以看出,SettleDelay是一个与输入端的建立时间(Tsetup)有关的量,SwitchDelay是一个与输入端保持时间有关的量(Thold)。

公式1和公式2中的Tft_data与Tft_clk在Ca-dence仿真工具中是通过仿真获得的数据,它与Ca-dence仿真中fast和slow状态下的SwitchDelay与SettleDelay参数有关。

为了了解Cadence仿真中的SwitchDelay和SettleDelay与时序公式中参数的关系,我们重新分析一下包含有BufferDelay曲线的时序图。

在图4中,时钟输出和数据输出使用的是BufferDelay曲线,此时Tco是时钟BufferDelay曲线和数据BufferDelay曲线之间的延时关系,这种定义符合“手册中的Tco是在特定负载下测得的”说法。

在图4中,CPUCLKOUT(BufferDelay)和CPUSignalsOUT(Bufferdelay)是在测试负载条件下的信号输出波形(对应于图3中的BufferDelay曲线,而不是驱动端输出曲线),SDRAMCLKIN和SDRAMSignalsIN是在实际负载条件下输入端口的仿真波形。

在器件手册中给出时序关系时,对于时钟信号,通常以某一测量电压为时间测量点,如图4中的Vmeas1和Vmeas2,对于驱动端测量电压点为驱动器件手册中定义的测量点,对于接收端测量电压点为接收器件手册中定义的测量点。

在Cadence仿真时,对于接收端电压测量点的设置,通常在接收器件模型中,把输入高低门限电平定义成Vmeas2来实现。

对于驱动端电压测量点的设置,是在驱动器件模型参数中设置的。

此时对于时钟仿真的结果是,时钟信号的SettleDelay和SwitchDelay值相等。

对于数据信号的测量点就稍微有点复杂了,这要根据手册中Tco的测量方式来确定,有的器件手册Tco是从时钟的Vmeas到数据的Vmeas来测量的,有的手册是从时钟的Vmeas到数据的门限电平来测量的。

如果采用从时钟的Vmeas到数据的门限电平来测量的,则在Cadence仿真中,要对高低电平门限分别作为测量点仿真,然后取最恶劣的仿真结果。

对于公式中数据的延时Tft_data,从Cadence仿真中对SettleDelay和SwitchDelay的定义和图4中的时序关系可以看出,Tft_data就是仿真结果中的SettleDelay和SwitchDelay参数,并且SettleDelay是与建立时间(Tsetup)有关,SwitchDelay是与保持时间(Thold)有关,因此公式中的Tft_data_min对应仿真结果中的SwitchDelay,Tft_data_max对应仿真结果中的SettleDelay,考虑到通常Slow状态的延时比Fast状态的延时要大,因此,公式中的Tft_data_min对应仿真结果中Fast状态的SwitchDelay,Tft_da-ta_max对应仿真结果中Slow状态的SettleDelay。

对于公式中时钟的延时,从测量方式中可以看出Tft_clk=SettleDelay=SwitchDelay,考虑到同一公式(下转第56页)图3图4592006·9·(总第88期)http://www.cicmag.com中仿真状态的一致,因此,公式中与Thold有关的不等式中的Tft_clk对应于Fast状态的仿真值,与Tsetup有关的不等式中的Tft_clk对应Slow状态的仿真值。

写成公式就是:Tft_data_fast_switchdelay>Thold–Tco_min+Tft_clk_fast(公式5)Tft_data_slow_settledelay<Tcycle-Tsetup–Tco_max+Tft_clk_slow(公式6)在实际仿真中,我们只要保证仿真结果满足公式5和公式6的时钟和数据关系,也就保证了单板工作时序的正确性。

四.总结Cadence公司的AllegroSI和SigXplor设计工具为硬件开发工程师提供了一个功能强大的高速PCB仿真手段,通过仿真设计,可以设计出符合要求的信号时序和信号完整性,从而提高单板和系统的工作稳定性,降低开发风险和开发成本。

参考文献【1】CadenceDesignSystemInc.,“High-SpeedDe-signUsingSPECCTRAQuest”【2】CadenceDesignSystemInc.,“SPECCTRAQuestFoundations”,July,2003应用在HyperTransport和并行RapidIO等协议之中,其数据率可以达到1.6Gbps.锁定前向时钟前向有一个缺点,由于它的时钟一直运行,因此有电源消耗和电磁干扰的问题。