分析图示组合逻辑电路的功能

- 格式:doc

- 大小:352.50 KB

- 文档页数:1

数字逻辑复习题⼭东理⼯⼤学成⼈⾼等教育数字逻辑复习题⼀、分析下图所⽰组合逻辑电路的功能。

要求写出逻辑函数表达式,列出真值表,最后分析功能。

⼆、⽤异或门和与⾮门设计⼀个全加器。

(要求:列出真值表,写出表达式,最后画出逻辑电路图)三、⽤3-8线译码器74138和适当的与⾮门实现逻辑函数C AB C A C B A F +=),,(1。

四、分析下图所⽰的同步时序逻辑电路的功能。

写出输出函数和激励函数表达式、次态真值表、状态图,最后分析出电路的逻辑功。

y 2CPXy 1五、⽤卡诺图化简法求出下列逻辑函数的最简与-或表达式。

C B ACD C A B A D C B A F +++=),,,(六、分析下图所⽰组合逻辑电路的功能。

A BCS七、⽤多路4选1选择器MUX 实现4变量逻辑函数∑=)13,10,9,8,7,3,2,0(),,,(m D C B A F的功能,选⽤变量C 和D 作为选择控制变量,画出电路图。

F⼋、把下列不同进制数写成按权展开形式。

(1) (4517.239)10 (3) (325.744)8 (2) (10110.0101)2 (4) (785.4AF)16九、写出下列各数的原码、反码和补码。

(1) 0.1011 (2) –10110⼗、图⽰电路均为TTL 门,各电路在实现给定的逻辑关系时是否有错误,如有错误请改错。

BF AB=F A B=+A B (2)F AB=A B (3)⼗⼀、由集成四位⼆进制同步步计数器74161和8选1数据选择器74LS151组成的电路如图所⽰。

试按要求回答:(15分)CPF(1)74161组成⼏进制计数器电路;(2)画出计数状态转换图;(3)写出输出Y 的序列信号的⼀个周期;⼭东理⼯⼤学成⼈⾼等教育数字逻辑复习题答案⼀.分析下图所⽰组合逻辑电路的功能⽤代数法对输出函数F 的表达式化简如下:C A B A F ⊕+⊕=功能评述:由真值表可知,该电路仅当A,B,C 取值同时为0或同为1时输出F 的值为0,其他情况下输出F 为1。

分析图示组合逻辑电路

的功能

本页仅作为文档封面,使用时可以删除

This document is for reference only-rar21year.March

A B

H S H C A B C

F

分析图示组合逻辑电路的功能。

A B

C

F

分析图所示逻辑电路的逻辑功能,要求写出逻辑式,列出真值表并分析逻辑功能。

某公司有A 、B 、C 三个股东,分别占公司50%、30%、20%的股份。

一个议案要获得通过,必须有超过50%股权的股东投赞成票。

试列出该公司表决电路的真值表。

解:用1表示股东赞成议案,用 0表示股东不赞成议案; 用F 表示表决结果,且用1表示议案获得通过, 用0表示议案未获得通过。

根据这些假定,不难列

1-10所示。

F=ABC+ABC+ABC=AC+AB

3、由逻辑式画出逻辑图。

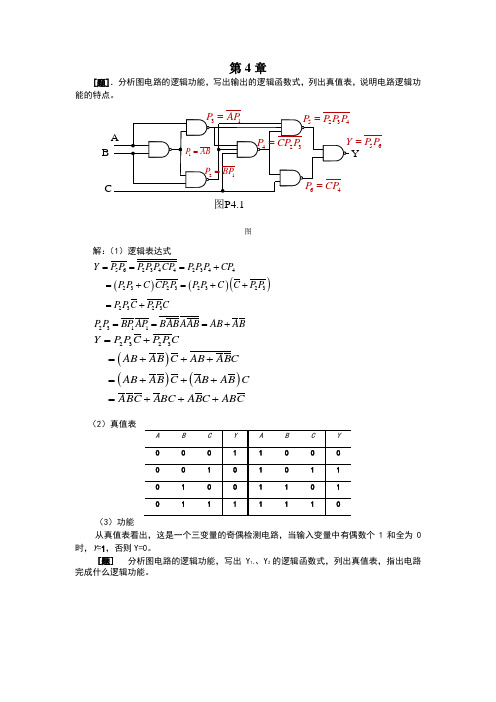

第4章[题4.1].分析图P4.1电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图P4.2解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题4.3] 分析图P4.3电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题4.4] 图P4.4是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP =0、Z=0的真值表从略。

[题4.5] 用与非门设计四变量的多数表决电路。

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

(√,× ) 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未达到最简 B .电路有多个输出 C .电路中的时延 D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲 12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→01 13.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .010 14.数据分配器和 有着相同的基本电路结构形式。

实验二 组合逻辑电路功能分析与设计一、 实验目的:1、了解组合逻辑电路的特点;2、掌握组合逻辑电路功能的分析方法;3、学会组合逻辑电路的连接方法;4、掌握组合逻辑电路的设计方法。

二、实验原理:1、组合逻辑电路的特点:组合逻辑电路可以有一个或多个输入端,也可以有多个输出端;在组合逻辑电路中,数字信号是单向传递的,只有从输入到输出的传递; 输出信号只与输入的即时状态有关2、组合逻辑电路的分析方法:真值表法;卡洛图法;逻辑表达式法;逻辑电路图法;3、组合逻辑电路的设计步骤:实际的逻辑问题→定义输出和输入变量→真值表→选定器件类型→化简→最简表达式→逻辑图 三、实验器件集成块:74LS00、74LS04、74LS08、74LS32 四、实验内容: (一)、组合逻辑电路功能分析分析图4-1所示电路的逻辑功能: 由电路图所得的逻辑表达式:Y=AB+A B =A ☉B逻辑功能:用与门和与非门实现同或(二)、组合逻辑电路设计(根据组合逻辑电路的设计步骤,分别写出各个组合逻辑电路的设计步骤。

)1、设计一个举重裁判表决器。

设举重比赛有三个裁判,一个主裁判和两个副裁判。

杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。

只有当两个或两个以上裁判(其中必须有主裁判)判明成功时,表示“成功”的灯才亮。

(要求用与非门实现)设A 为主裁判的判定;B ,C 分别为两位副裁判的判别(0为裁判不确定,1为裁判确定);Y=0表示不成功,Y=1表示成功。

1图4-1由真值表得到的逻辑表达式为:Y=AB+AC=ACAB∙电路图为:2、某设备有开关A、B、C,要求仅在开关A接通的条件下,开关B才能接通;开关C 仅在开关B接通的条件下才能接通。

违反这一规程,则发出报警信号。

设计一个由与非门组成的能实现这一功能的报警控制电路。

(要求用与非门实现)设A,B,C分别为三个开关(0表示开关断开,1表示开关闭合);Y=0表示不违反规程,Y=1表示违反规程,将发生报警信号。