组合逻辑电路

- 格式:ppt

- 大小:1.17 MB

- 文档页数:116

第1篇一、实验目的1. 理解组合逻辑电路的基本概念和组成原理;2. 掌握组合逻辑电路的设计方法;3. 学会使用逻辑门电路实现组合逻辑电路;4. 培养动手能力和分析问题、解决问题的能力。

二、实验原理组合逻辑电路是一种在任意时刻,其输出仅与该时刻的输入有关的逻辑电路。

其基本组成单元是逻辑门,包括与门、或门、非门、异或门等。

通过这些逻辑门可以实现各种组合逻辑功能。

三、实验器材1. 74LS00芯片(四路2输入与非门);2. 74LS20芯片(四路2输入或门);3. 74LS86芯片(四路2输入异或门);4. 74LS32芯片(四路2输入或非门);5. 逻辑电平转换器;6. 电源;7. 连接线;8. 实验板。

四、实验步骤1. 设计组合逻辑电路根据实验要求,设计一个组合逻辑电路,例如:设计一个3位奇偶校验电路。

2. 画出逻辑电路图根据设计要求,画出组合逻辑电路的逻辑图,并标注各个逻辑门的输入输出端口。

3. 搭建实验电路根据逻辑电路图,搭建实验电路。

将各个逻辑门按照电路图连接,并确保连接正确。

4. 测试电路功能使用逻辑电平转换器产生不同的输入信号,观察输出信号是否符合预期。

五、实验数据及分析1. 设计的3位奇偶校验电路逻辑图如下:```+--------+ +--------+ +--------+| | | | | || A1 |---| A2 |---| A3 || | | | | |+--------+ +--------+ +--------+| | || | || | |+-------+-------+||v+--------+| || F || |+--------+```2. 实验电路搭建及测试根据逻辑电路图,搭建实验电路,并使用逻辑电平转换器产生不同的输入信号(A1、A2、A3),观察输出信号F是否符合预期。

(1)当A1=0,A2=0,A3=0时,F=0,符合预期;(2)当A1=0,A2=0,A3=1时,F=1,符合预期;(3)当A1=0,A2=1,A3=0时,F=1,符合预期;(4)当A1=0,A2=1,A3=1时,F=0,符合预期;(5)当A1=1,A2=0,A3=0时,F=1,符合预期;(6)当A1=1,A2=0,A3=1时,F=0,符合预期;(7)当A1=1,A2=1,A3=0时,F=0,符合预期;(8)当A1=1,A2=1,A3=1时,F=1,符合预期。

第3章组合逻辑电路3.1 组合逻辑电路的概述按照逻辑功能的不同特点,可以把数字电路分成两大类,一类叫做组合逻辑电路,另一类叫做时序逻辑电路。

什么叫组合逻辑电路呢?在t=a时刻有输入X1、X2、……Zn,那么在t=a时刻就有输出Z1、Z2、……Zm,每个输出都是输入X1、X2、……Zn的函数,Z1=f1(X1、X2、……Xn)Z1=f2(X1、X2、……Xn)Zm=fm(X1、X2、……Xn)从以上概念可以知道组合逻辑电路的特点就是即刻输入,即刻输出。

任何组合逻辑电路可由表达式、真值表、逻辑图和卡诺图等四种方法中的任一种来表示其逻辑功能。

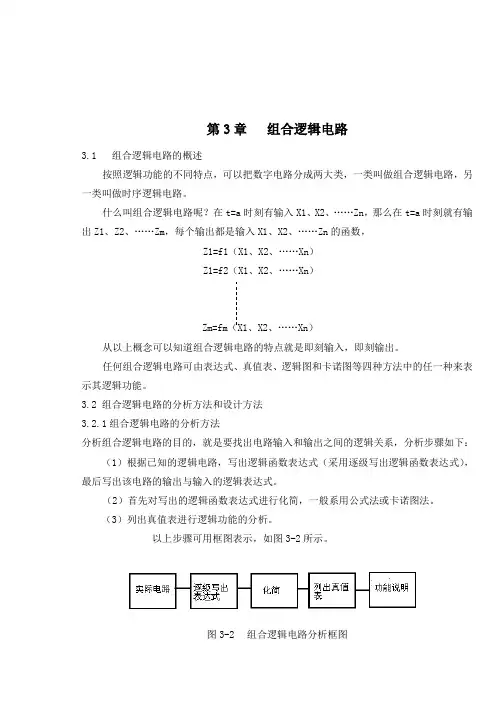

3.2 组合逻辑电路的分析方法和设计方法3.2.1组合逻辑电路的分析方法分析组合逻辑电路的目的,就是要找出电路输入和输出之间的逻辑关系,分析步骤如下:(1)根据已知的逻辑电路,写出逻辑函数表达式(采用逐级写出逻辑函数表达式),最后写出该电路的输出与输入的逻辑表达式。

(2)首先对写出的逻辑函数表达式进行化简,一般系用公式法或卡诺图法。

(3)列出真值表进行逻辑功能的分析。

以上步骤可用框图表示,如图3-2所示。

图3-2 组合逻辑电路分析框图下面举例说明对组合逻辑电路的分析,掌握其基本思路及方法。

【例3-1】 分析图3-3所示电路的逻辑功能图3-3 [例3-1]逻辑电路解:(1)写出输出Z 的逻辑表达式: Z1=B A , Z2=B AZ=21Z Z •=B A B A • (2)化简Z=B A B A •=A B +A B=A ⊕B (3)列出真值表进行逻辑功能说明 列出该函数真值表,如表3.1所示: 表3-1 [例3-1]真值表 A B Z 0 0 0 0 1 1 1 0 1 1 13.2.2组合逻辑电路的设计方法组合逻辑电路的设计步骤与分析步骤相反,设计任务就是根据逻辑功能的要求设计逻辑电路,其步骤如下:(1)首先对命题要求的逻辑功能进行分析,确定哪些是输入变量,哪些为输出函数,以及它们之间的相互逻辑关系,并对它们进行逻辑赋值。