组合逻辑电路原理概述及作用分析

- 格式:pdf

- 大小:82.29 KB

- 文档页数:3

组合逻辑电路工作原理组合逻辑电路是数字电路中的一类重要电路,它由与门、或门、非门等基本逻辑门组合而成,能够实现各种布尔函数的逻辑运算。

本文将详细介绍组合逻辑电路的工作原理。

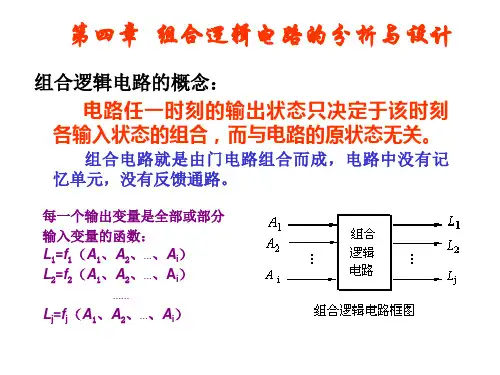

一、组合逻辑电路的基本概念组合逻辑电路是一种没有存储功能的数字电路,其输出仅取决于当前输入信号的状态,而与历史输入信号的状态无关。

组合逻辑电路的输出完全由输入决定,是一种纯粹的函数关系。

组合逻辑电路由逻辑门组成,逻辑门是数字电路中最基本的逻辑运算单元。

与门、或门、非门是最常见的逻辑门。

与门的输出只有当所有输入都为1时才为1,或门的输出只要有一个输入为1即可为1,非门的输出与输入相反。

二、组合逻辑电路的实现方法组合逻辑电路可以通过三种方法来实现:基于逻辑门的实现、基于真值表的实现和基于卡诺图的实现。

1. 基于逻辑门的实现基于逻辑门的实现是最常用的方法之一。

逻辑门可以相互连接,通过组合连接不同的逻辑门,可以实现各种布尔函数的逻辑运算。

例如,若要实现A与B的逻辑与运算,可以将A和B分别与一个与门的两个输入端相连接,结果输出为与门的输出端。

2. 基于真值表的实现真值表是一种列出各种可能输入情况下的输出值的表格。

通过观察真值表的规律,可以得出逻辑关系,从而确定实现组合逻辑电路所需的逻辑门类型和连接方式。

3. 基于卡诺图的实现卡诺图是一种图形化的逻辑运算方法,通过在二进制表示的状态图上进行操作,可以快速找到最简化的布尔表达式。

通过卡诺图,可以确定逻辑门类型和连接方式,进而实现组合逻辑电路。

三、组合逻辑电路的工作原理组合逻辑电路的工作原理可以简单归纳为以下几个步骤:1. 输入信号传递组合逻辑电路的输入信号通过输入端传入电路中。

输入信号可以是开关、传感器等外部输入。

2. 逻辑运算输入信号进入逻辑门后,根据逻辑门的类型进行相应的逻辑运算。

与门、或门、非门等逻辑门按照事先设定的布尔运算规则对输入信号进行逻辑运算,得出运算结果。

3. 输出信号生成逻辑运算的结果将成为组合逻辑电路的输出信号。

组合逻辑电路的分析在分析组合逻辑电路时,我们可以使用真值表、卡诺图或布尔代数等方法。

下面将分别介绍这些方法的基本原理和应用。

1.真值表分析法真值表是列出电路的所有可能输入和对应输出的表格。

通过逐行检查真值表的输出列,可以确定电路的功能。

真值表分析法适用于较小规模的电路,但对于较复杂的电路可能不够实用。

2.卡诺图分析法卡诺图是一种图形表示方法,用于描述逻辑函数之间的关系。

它将所有可能的输入组合表示为一个方格矩阵,每个方格代表一个状态。

相邻的方格表示输入之间只有一个位不同。

通过合并相邻的方格,我们可以找到简化逻辑函数的最小项或最小项组合。

卡诺图分析法可以用来优化逻辑电路,减少门的数量和延迟。

3.布尔代数分析法布尔代数是一种用符号和运算规则描述逻辑函数的代数系统。

我们可以使用布尔代数的运算规则来简化和优化逻辑电路。

常见的布尔代数运算包括与运算、或运算、非运算和异或运算等。

通过应用这些运算规则,我们可以将复杂的逻辑函数简化为最小项或最小项组合,从而简化电路。

在进行组合逻辑电路的分析时,我们首先需要确定电路的输入和输出。

然后,我们可以根据电路的功能和输出要求,绘制真值表或卡诺图。

通过分析真值表或卡诺图,我们可以找到逻辑函数的最小项或最小项组合。

接下来,我们可以将这些最小项或最小项组合转化为逻辑门的输入方式。

最后,我们可以使用布尔代数的运算规则来简化逻辑函数和电路。

组合逻辑电路的分析是电路设计和优化的重要一步。

通过应用不同的分析方法,我们可以更好地理解电路的功能和性质,从而更好地设计和优化电路。

在分析组合逻辑电路时,我们需要注意电路的输入和输出要求,合理选择和配置逻辑门,以及优化电路的延迟和开销。

组合逻辑电路设计组合逻辑电路是数字电路中的一种基本电路类型,它由逻辑门组合而成,能够实现特定的逻辑功能。

本文将探讨组合逻辑电路设计的基本原理和方法,介绍一些常见的设计技巧。

一、组合逻辑电路的基本原理组合逻辑电路是由逻辑门(如与门、或门、非门等)按照特定的逻辑关系组成的。

它的输入信号经过逻辑门的运算后,得到输出信号。

组合逻辑电路的输出完全取决于当前的输入信号,与之前的输入信号或状态无关。

因此,它是一种无记忆性的电路。

组合逻辑电路的设计需要确定输入和输出之间的逻辑关系,即真值表。

通过真值表,我们可以得到逻辑门的布尔代数表达式,进而确定电路的结构和连接方式。

常用的逻辑门包括与门、或门、非门、异或门等。

二、组合逻辑电路的设计方法1. 确定逻辑功能:根据需求确定电路应该实现的逻辑功能。

可以通过文字描述或真值表的形式进行规定。

2. 按照真值表确定布尔代数表达式:通过真值表,我们可以得到电路的逻辑关系,进而推导出逻辑门的布尔代数表达式。

例如,一个与门的真值表为:| 输入A | 输入B | 输出 ||------|------|-----|| 0 | 0 | 0 || 0 | 1 | 0 || 1 | 0 | 0 || 1 | 1 | 1 |由此可得与门的布尔代数表达式为:输出 = A·B。

3. 设计逻辑门电路:根据上一步得到的布尔代数表达式,选择适当的逻辑门进行组合设计。

将逻辑门按照表达式和电路的连接关系进行布局。

4. 优化电路结构:对电路进行优化,以减少逻辑门的数量和延迟。

常见的优化技术包括代数化简、费诺定理、卡诺图等。

5. 进行验证和仿真:使用逻辑仿真软件对设计的电路进行验证和调试。

通过输入不同的信号组合,检查输出是否符合预期结果。

三、组合逻辑电路的设计技巧1. 使用多级逻辑门:为了减少电路的延迟和功耗,可以使用多级逻辑门的方式来实现复杂的逻辑功能。

将多个逻辑门级联,形成一个级性结构。

2. 使用寄存器:当需要存储中间结果时,可以使用寄存器来保存数据。

数字电路中的组合逻辑分析数字电路是由多个数字逻辑门组成的电路,用于实现逻辑函数的计算和处理。

其中的组合逻辑是指电路中的输出仅取决于当前的输入,而不受到过去输入的影响。

本文将对数字电路中的组合逻辑进行深入分析和探讨。

一、组合逻辑的定义与特点组合逻辑电路是一种基于当前输入产生输出的电路,它通过各个输入端的逻辑信号来控制输出端的电平状态。

与之相对的是时序逻辑电路,后者的输出还会受到过去输入的影响。

组合逻辑的特点是:输出只与当前输入相关,没有时序要求,其状态由逻辑门的逻辑运算决定。

逻辑门是指基于布尔代数进行逻辑函数运算的元件,常见的有与门、或门、非门等。

二、组合逻辑的基本原理组合逻辑电路的设计离不开布尔代数和逻辑函数的运算。

布尔代数是一种数学分支,用于描述逻辑关系和运算,逻辑函数则是布尔代数的基础,通过与、或、非等运算来定义。

在数字电路中,通过配置逻辑门的输入和输出,我们可以实现各种复杂的逻辑运算。

比如,通过与门实现逻辑与运算,通过或门实现逻辑或运算,通过非门实现逻辑非运算等。

三、常见的组合逻辑电路1. 逻辑门逻辑门是组合逻辑电路的基本构建模块,常见的有与门、或门、非门等。

与门输出的结果只有当所有输入同时为高电平时才为高电平,否则为低电平;或门输出的结果只有当任何一个输入为高电平时才为高电平,否则为低电平;非门则是将输入反转输出。

2. 多路选择器多路选择器是一种用于实现逻辑运算的组合逻辑电路。

它有多个输入端和一个输出端,通过控制信号选择其中一个输入信号输出。

多路选择器的选择功能可用于实现多种逻辑运算,如优先级编码器、译码器、地址编码器等。

3. 数字加法器数字加法器是一种用于实现数字加法运算的组合逻辑电路。

常见的数字加法器有半加器、全加器、级联加器等。

通过组合和级联这些加法器,可以实现任意长度数字的加法运算。

4. 译码器译码器是一种将有限的输入状态转换成特定的输出状态的组合逻辑电路。

它通常用于将二进制编码转换成对应的控制信号,实现多路选择、显示等功能。

组合逻辑电路概念引言组合逻辑电路是数字电路中最基本的电路之一,它由逻辑门组成,根据输入信号的不同组合产生相应的输出信号。

本文将介绍组合逻辑电路的基本概念、工作原理、常见的逻辑门和设计方法。

一、组合逻辑电路概述组合逻辑电路是指电路中的输出仅取决于当前输入信号的组合,与电路之前的状态无关。

它利用逻辑门来实现不同的布尔逻辑功能,常用于数字电子设备中的逻辑运算、数据处理、控制和计算等领域。

组合逻辑电路的特点是输出仅取决于当前的输入状态,具有简单、稳定、可靠等优点。

二、逻辑门逻辑门是组合逻辑电路的基本构建单元,它能够根据输入信号的不同组合产生相应的输出信号。

常见的逻辑门有与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)等。

2.1 与门(AND)与门是一种多输入、一输出的逻辑门,只有当所有输入信号同时为高电平时,输出信号才为高电平,否则输出信号为低电平。

2.2 或门(OR)或门是一种多输入、一输出的逻辑门,只要有一个输入信号为高电平,输出信号就为高电平,否则输出信号为低电平。

2.3 非门(NOT)非门是一种一输入、一输出的逻辑门,输出信号与输入信号相反,即当输入信号为高电平时,输出信号为低电平,反之亦然。

2.4 异或门(XOR)异或门是一种多输入、一输出的逻辑门,当输入信号中的高电平个数为奇数时,输出信号为高电平,否则输出信号为低电平。

三、组合逻辑电路的设计组合逻辑电路的设计包括电路的逻辑功能设计和物理实现设计。

3.1 逻辑功能设计逻辑功能设计是指根据需求确定组合逻辑电路的逻辑功能,选择适当的逻辑门和其输入输出关系,以满足特定的逻辑要求。

这需要对问题进行抽象和分析,将问题转化为逻辑表达式或真值表,再根据逻辑表达式进行电路设计。

3.2 物理实现设计物理实现设计是指将逻辑电路转化为具体的电子元器件组合,并布线在PCB板上的设计。

这一过程需要根据逻辑功能设计的结果选择合适的逻辑门芯片或者设计自定义逻辑门电路,然后进行元器件布局和连线设计,最终形成一个满足逻辑要求的组合逻辑电路。

组合逻辑电路原理引言组合逻辑电路是现代电子技术中最基本的电路之一,广泛应用于数字系统中。

组合逻辑电路由多个逻辑门组成,能够根据输入信号的组合产生相应的输出信号。

本文将深入探讨组合逻辑电路的原理及其应用。

什么是组合逻辑电路组合逻辑电路是指在没有时钟信号的控制下,根据输入信号的组合产生相应的输出信号的电路。

组合逻辑电路由逻辑门、开关、电阻等元件组成,其输出仅取决于当前输入的状态,与之前的输入状态无关。

组合逻辑电路的基本元件逻辑门逻辑门是组合逻辑电路的基本构建单元,它实现了逻辑运算的功能。

常见的逻辑门有与门、或门、非门、异或门等。

•与门:当所有输入信号都为高电平时,与门的输出为高电平;否则,输出为低电平。

•或门:当任意输入信号为高电平时,或门的输出为高电平;否则,输出为低电平。

•非门:非门只有一个输入信号,当输入为低电平时,输出为高电平;当输入为高电平时,输出为低电平。

•异或门:当输入信号的数量为奇数时,异或门的输出为高电平;当输入信号的数量为偶数时,输出为低电平。

开关开关用于输入信号的控制,可以打开或关闭电路的通路。

开关可以是手动操作的按钮,也可以是自动控制的传感器。

电阻电阻用于限制电流的流动,保护电路不受损坏。

电阻的阻值决定了电流通过的大小。

组合逻辑电路的实现原理组合逻辑电路的实现原理是基于逻辑门的工作特性。

逻辑门接收输入信号,并根据逻辑运算规则产生输出信号。

组合逻辑电路的设计过程通常包括以下几个步骤:1.确定逻辑功能:根据具体的需求,确定所需的逻辑功能,例如与门、或门、非门等。

2.设计真值表:根据逻辑功能的定义,设计真值表,列出所有可能的输入组合及其对应的输出。

3.确定逻辑方程:根据真值表,可以得到逻辑方程,即输出信号与输入信号之间的逻辑关系。

4.实现逻辑电路:根据逻辑方程,使用逻辑门、开关和电阻等元件来实现逻辑电路。

5.电路测试:对设计的逻辑电路进行测试,验证其功能是否符合预期。

组合逻辑电路的应用组合逻辑电路广泛应用于数字系统中,例如计算机、通信系统、工业控制等领域。

组合逻辑电路的逻辑功能特点1. 什么是组合逻辑电路?组合逻辑电路,听起来挺复杂的,但其实它就像我们生活中的小工具,随处可见,功能却相当强大。

简单来说,组合逻辑电路是一种电路,输出的结果完全依赖于输入的状态,而不是过去的历史。

就好比你点了外卖,今天想吃炸鸡,那你就会得到一份炸鸡,明天想吃寿司,你点的就变成了寿司。

没错,组合逻辑电路就是这么灵活,能根据输入“立马”给出对应的输出。

想象一下,一个小型餐厅的厨师,如果你告诉他今天想吃意大利面,他立刻就会准备意大利面,而不是再问你昨天吃了什么。

这种实时响应的特性就是组合逻辑电路的魅力所在。

它不需要记忆,不受以前的影响,只看当下的输入,这种特点让它在各种应用中大放异彩,比如计算机、汽车电子和家电控制等。

2. 组合逻辑电路的基本功能2.1 逻辑运算说到组合逻辑电路,逻辑运算是它的“主菜”。

像是“与”、“或”、“非”等基本运算,就像我们日常生活中常用的调味料,虽然简单,但缺一不可。

想象一下,两个开关,一个是“灯”,一个是“开关”。

如果你想开灯,两个开关都得“开”,这就是“与”运算。

而如果你只想要其中一个开,那就用“或”运算,任意一个开关打开,灯就亮了。

2.2 选择与优先级在组合逻辑电路中,还有个有趣的概念就是“选择”。

当输入有多种选择时,电路会根据预设的规则来决定输出,想象一下在快餐店排队,今天想吃汉堡,明天想吃沙拉。

这个“选择”的过程就像是电路中的选择器,确保你每次都能点到想要的食物。

而优先级就像是妈妈的叮嘱,总是有些事儿比其他事儿更重要。

比如说,如果你在厨房里炒菜,同时还想煮汤,结果你发现锅太小,那就得优先炒菜,再煮汤,这就是组合逻辑电路处理输入时会遵循的优先级原则。

3. 组合逻辑电路的应用场景3.1 计算器组合逻辑电路最常见的应用之一就是计算器,没错,就是你每天都在用的那个。

你输入“2 + 3”,瞬间就能看到“5”。

这里的每一步都是一个组合逻辑电路在为你服务,尽管你看不见,但它却默默在你身边,帮你完成数学的“魔法”。

组合逻辑电路组合逻辑电路是电子电路中最为基础的一种电路类型,其输入变量与输出变量之间的关系完全由它们之间的逻辑关系所决定。

组合逻辑电路可以简单描述为:“输入端口的电信号经过一个逻辑门,输出变量就随之产生并由输出端口发送出去”,组合逻辑电路中不包括概念上的时钟或记忆单元,实现逻辑功能的电路的输出只涉及当前输入状态。

本文将从组合逻辑电路的概念、组成部分及功能三个方面进行介绍。

一、组合逻辑电路的概念组合逻辑电路,是指由一些逻辑门以及它们之间的互连所组成的电路。

其中,逻辑门代表着一种或多种逻辑函数,其输入与输出可以是单个或多个电平或电位信号。

这些逻辑门能够执行特定的布尔运算,其结果可以反映在其输出端口上,也就是根据输入数据的逻辑关系进行处理和输出。

组合逻辑电路的工作原理是使逻辑门之间的信号通过特定逻辑关系进行耦合,形成逻辑闭环,并根据不同的逻辑输出操作信号产生先进的逻辑功能。

同时,组合逻辑电路具有很强的普适性和可扩展性,能够处理各种逻辑运算,是数字电路设计的基本组成部分。

二、组合逻辑电路的组成部分组合逻辑电路共由逻辑门、施密特触发器、数字比较器等构成,每个组合逻辑电路都是由若干个逻辑门以及它们之间的互连所组成,其中逻辑门的种类有三种。

1、与门(AND-Gate):两个或多个输入信号都为高电平时,输出信号才为高电平,否则输出为低电平。

2、或门(OR-Gate):两个或多个输入信号中只要有一个为高电平,则输出信号为高电平,否则输出为低电平。

3、非门(NOT-Gate):只有一个输入信号,当该输入信号为高电平时,输出信号为低电平;反之,输出为高电平。

通常情况下,组合逻辑电路包括三种类型:多路选择器、编码器和译码器。

其中,多路选择器的功能是在输入端口中有多个数据源的情况下选择其中之一的数据源;编码器的功能是将一个多位码转换为其代表的唯一数字;而译码器是将一个数字转换为其代表的多位码。

组合逻辑电路中用到的施密特触发器常常用于扩大输入信号的幅度,同时也可以用于提高抗干扰能力。

组合逻辑电路原理概述及作用分析

组合逻辑电路概述:

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

1.半加器与全加器

①半加器

两个数A、B相加,只求本位之和,暂不管低位送来的进位数,称之为半加。

完成半加功能的逻辑电路叫半加器。

实际作二进制加法时,两个加数一般都不会是一位,因而不考虑低位进位的半加器是不能解决问题的。

②全加器

两数相加,不仅考虑本位之和,而且也考虑低位来的进位数,称为全加。

实现这一功能的逻辑电路叫全加器。

2.加法器

实现多位二进制数相加的电路称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器两种。

①四位串行加法器:如T692。

优点:电路简单、连接方便。

缺点:运算速度不高。

最高位的计算,必须等到所有低位依此运算结束,送来进位信号之后才能进行。

为了提高运算速度,可以采用超前进位方式。