版图之一

版图之二

上面的版图有些复杂,看不清图形的细节,下面 我们先从认识简单的单元电路的版图开始,学习 版图的设计方法.

NMOS 管的版图

Poly-silicon N select

Active

P select

Metal

P-sub

PMOS

Nwell

CMOS-工艺的 横向-PNP

N-Well

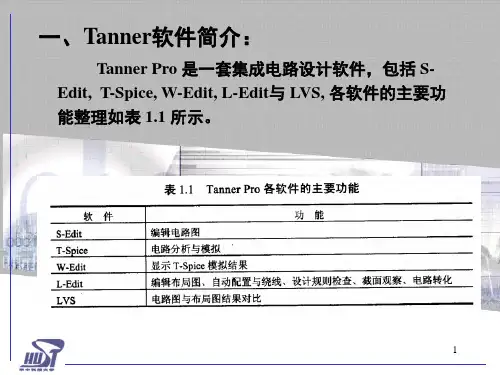

第6章 版图设计概述及L-Edit简介

集成电路版图设计工作非常复杂,掌握集成电路 的版图设计技术不可能毕其功于一役,必须循序 渐进。在学习中不可能一次将所有细节都搞清楚, 有时我们需要忽略一些细节,而只关心问题的主 要方面,细节问题待以后学习。 下面我们先认识一下实际版图。 看两个用L-Edit设计的版图的例子:

Device Extract

组件特性提取器,可以生成电路串接文件,可以从布局 图形中,提取组件特性,包括电阻、电容、组件长度、 组件宽度和面积。 L-Edit/Extract 可将由 L-Edit 所画出的 layout 生成出 SPICE netlist,用来作 LVS 比对或者是用 T-SPICE 去做 layout 后段仿真。它能够提取出组件和使用者自己定义 的子电路,支持 90 度和 45 度的对象。电路中去标示组 件及节点对于寻找layout 里面的元素可以达到快速的提 取。 对 于 大 多 数 共 同的组 件 参数都 可 提取出 来 , 像 是 MOSFET 长 , 宽, 源极/ 汲极面积和周长。 Diodes, BJTs, MESFETs, JFETs 的面积。对于有阶层的子电路也能提 取,还包含电容和电阻。

APR (Standard Cell Place & Route)