利用Timing closure floorplan 分析和优化设计

- 格式:pdf

- 大小:1.32 MB

- 文档页数:52

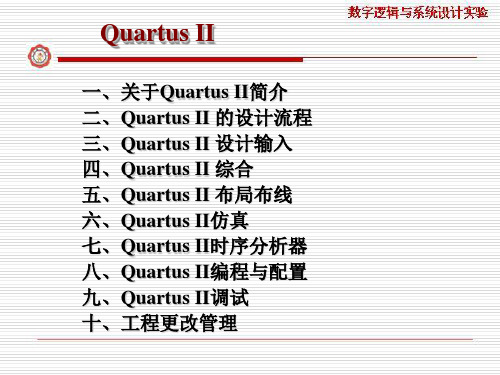

6.3 Quartus II操作指南6.3.1简介Altera技术领先的Quartus II设计软件配合一系列可供客户选择的IP核,可使设计人员在开发和推出FPGA、CPLD和结构化ASIC设计的同时,获得无与伦比的设计性能、一流的易用性以及最短的市场推出时间。

这是设计人员首次将FPGA移植到结构化ASIC 中,能够对移植以后的性能和功耗进行准确的估算。

Quartus II软件支持VHDL和Verilog硬件描述语言(HDL)的设计输入、基于图形的设计输入方式以及集成系统级设计工具。

Quartus II软件可以将设计、综合、布局和布线以及系统的验证全部都整合到一个无缝的环境之中,其中还包括和第三方EDA工具的接口。

Quartus II的主要特性有:<1>基于模块的设计方法提供工作效率<2>更快集成IP<3>在设计周期的早期对I/0引脚进行分配和确认<4>存储器编译器<5>支持CPLD、FPGA和基于HardCopy 的ASIC<6>使用全新的命令行和脚本功能自动化设计流程<7>高级教程帮助深入了解Quartus II的功能特性。

Altera公司的Quartus II软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证和仿真。

Quartus II设计软件根据设计者需要提供了一个完整的多平台开发环境,它包括整个FPGA和CPLD设计阶段的解决方案。

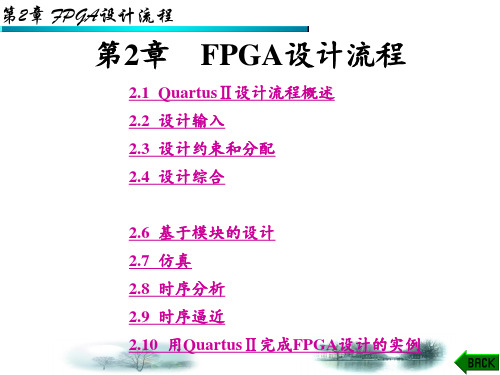

有关Quartus II的典型设计流程如图6-43所示。

1图6-43 Quartus II的典型设计流程此外,Quartus II软件为设计流程的每个阶段提供了Quartus II图形用户界面、EDA 工具界面和命令行界面。

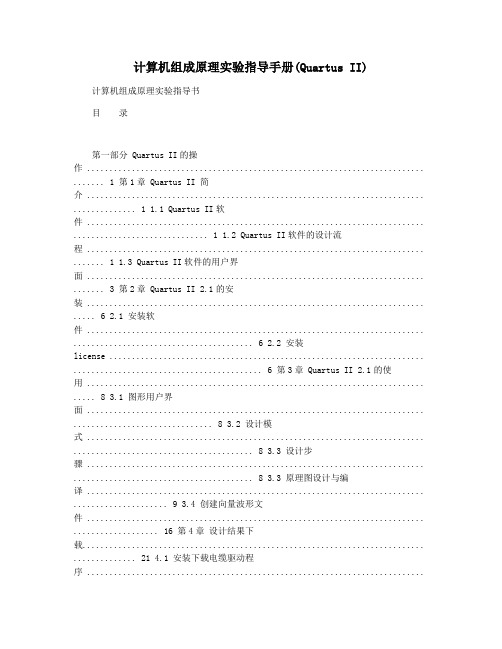

计算机组成原理实验指导手册(Quartus II) 计算机组成原理实验指导书目录第一部分 Quartus II的操作 ........................................................................... ....... 1 第1章 Quartus II 简介 ........................................................................... .............. 1 1.1 Quartus II软件 ........................................................................... .............................. 1 1.2 Quartus II软件的设计流程 ........................................................................... ....... 1 1.3 Quartus II软件的用户界面 ........................................................................... ....... 3 第2章 Quartus II 2.1的安装 ........................................................................... ..... 6 2.1 安装软件 ........................................................................... ........................................ 6 2.2 安装license ...................................................................... .......................................... 6 第3章 Quartus II 2.1的使用 ........................................................................... ..... 8 3.1 图形用户界面 ........................................................................... ............................... 8 3.2 设计模式 ........................................................................... ........................................ 8 3.3 设计步骤 ........................................................................... ........................................ 8 3.3 原理图设计与编译 ........................................................................... ..................... 9 3.4 创建向量波形文件 ........................................................................... ................... 16 第4章设计结果下载............................................................................ .............. 21 4.1 安装下载电缆驱动程序 ..................................................................................... 21 4.2 器件的选择与引脚的锁定与下载 ................................................................... 28 4.3 实验箱的设置与I/O引脚 ........................................................................... ....... 31 第二部分实验内容............................................................................ .................. 46 实验1 Quartus Ⅱ的使用 ........................................................................... ........... 46 实验2 运算器组成实验............................................................................ ........... 47 实验3 半导体存储器原理实验...........................................................................50 实验4 数据通路的组成与故障分析实验 (51)- 1 -计算机组成原理实验指导书第一部分 Quartus II的操作第1章 Quartus II 简介1.1 Quartus II软件Quartus II软件是Altera公司的综合开发工具,它集成了Altera的FPGA/CPLD(复杂可编程逻辑器件Complex Programmable Logic Device,CPLD/现场可编程器件Field Programmable Gate Array,FPGA)开发流程中所涉及的所有工具和第三方接口。

IC课堂:Timing ECO技巧和策略总结本文档主题其实就是介绍如何修Timing。

首先明确什么时候开始fix Timing?下面这三种情况下都可以应用。

1、deadline要到了2、PR tool已经尽力帮你做到最好还是不行3、Signoff STA timing 接近meet ,具体点讲就是:timing violation条数不能太多和slack不能太差;transition、fanout、capacitance、routing drc violation、IR drop、EM violation不能有一项很差。

Timing ECO 常用Strategy 和Skills通常是先修setup,后修hold。

那先看下修setup的策略:1、remove noise on clock path if 存在,可以在PT里面查看clock path上的noise。

具体指令如下所示:PT 指令:report_timing -nos -path_typefull_clock_expanded -crosstalk通常launch clock上的delta那一栏代表noise,如果是正的就是具体的noise大小capture clock上delta那一栏如果是负值就代表具体的noise 值,如果超过5ps就应该要修。

那为何产生clock noise?主要原因有:小buffer推很长的线;clock和signal线靠太近;clock routing 频繁地换层。

如果noise数量只有几根,可以考虑手修,如果太多,就应该要回去重新run CTS。

下面介绍手修clock noise的方法:(1)add shielding nets(2)增加clock 和其他nets的space(3)可以考虑用上层的金属走clock net,甚至可以用最top 层的metal,因为顶层的线noise最小;更甚至可以cut power stripe if 绕线真的已经完全挤不开空间可以这么尝试。

![5.6.3 Chip Editor视图[共2页]](https://img.taocdn.com/s1/m/0fa069cb59eef8c75ebfb39e.png)

第5章 Quartus II 的常用辅助设计工具1625.6.3 Chip Editor 视图Chip Editor 中包含有很多快速有效地修改设计的特性,主要集成在以下工具中。

∙ Chip Editor 底层布局,它允许用户检查设计的FPGA 使用资源情况。

∙ 资源特性编辑器,它允许用户对设计布局布线后的数据库做修改。

∙ 更改管理器,它允许用户跟踪所有的设计修改。

本节主要介绍Chip Editor 底层布局(Chip Editor 视图)和资源特性编辑器。

Chip Editor 使用户可以快速便捷地查看设计全编译后的布局布线信息。

选择【Tools 】/【Chip Editor 】命令,打开Chip Editor 视图。

Chip Editor 是以层次图来表示目标Altera 器件的底层布局布线信息的,随着层次图越深入,其底层布线信息就越详细。

一、 第一层视图Chip Editor 的第一层视图提供了整个器件的布局视图,此视图同Timing Closure Floorplan 的视图相似,它允许用户在设计中对某一个节点在Chip Editor 中进行定位。

Chip Editor 类似于Timing Closure Floorplan ,使用颜色来区别器件资源,以不同的蓝色来表示MRAM 、M4K 和M512存储快,DSP 块用橙色来表示,逻辑单元以浅蓝色表示。

图5-43所示为一个设计全编译后的Chip Editor 视图,Chip Editor 以黄色来表示已使用的逻辑资源和布线通道(图中的行列细线即为设计布线)。

图5-43 设计全编译后的Chip Editor 第一层视图二、 第二层视图Chip Editor 的第二层视图与第一层视图相似,器件的每个资源都以特殊的颜色高亮显示,如图5-44所示。

第二层视图提供的提示信息也同第一层视图相似,只是多了布线通道的详细信息。

在第二层视图中使用提示信息,可以知道此布线通道在器件中的位置以及使用情况等。

FPGA时序优化方法下面是几种常见的FPGA时序优化方法:1.约束优化:约束是指对电路时序和布局的设计要求。

通过正确地设置约束,可以促使FPGA布局工具在布局时考虑到电路的时序需求。

约束优化包括设置正确的时钟频率、引脚延迟、最小路径延迟等。

2.时钟优化:在FPGA设计中,时钟是非常重要的元件,也是时序优化的关键。

对时钟进行优化可以改善电路的时序性能。

时钟优化包括降低时钟频率、减少时钟路径长度、优化时钟布线和时钟分配等。

3.逻辑优化:逻辑优化是指通过优化电路的逻辑结构来改善时序性能。

逻辑优化可以包括逻辑分解、逻辑合并、信号复用、逻辑约简等。

通过逻辑优化可以减少电路的延迟和面积。

4.流水线优化:流水线是一种常见的时序优化技术,可以将复杂的计算过程分解为多个互相依赖的阶段,以提高电路的并行性和时序性能。

通过合理地设置流水线阶段的数量和互连方式,可以使电路的运行速度加快。

5.资源共享:资源共享是指将不同的计算单元共享一个硬件资源以优化电路的时序性能。

例如,将多个逻辑门共享同一个LUT(查找表)可以减少逻辑路径的延迟。

6.布线优化:布线是指将逻辑元件和时钟信号进行物理连线的过程。

布线优化可以通过选择合适的布线工艺规则、调整布线优先级、减少布线路径长度等方式来改善电路的时序性能。

7.时序仿真和分析:时序仿真和分析工具可以帮助设计人员了解电路的时序关系,并通过一系列的优化方法来改善时序性能。

通过仿真和分析可以发现潜在的时序问题,并指导设计人员进行优化。

综上所述,FPGA时序优化方法包括约束优化、时钟优化、逻辑优化、流水线优化、资源共享、布线优化和时序仿真分析等多个方面。

这些方法可以同时应用于FPGA设计中,以提高电路的时序性能和整体质量。

对于特定的设计需求和约束条件,设计人员需要结合实际情况选择适当的时序优化方法。

从大学时代第一次接触FPGA至今已有10多年的时间。

至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。

当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

后来读研究生,工作陆陆续续也用过Quartus II,Foundation,ISE,Libero,并且学习了verilogHDL语言,学习的过程中也慢慢体会到verilog的妙用,原来一小段语言就能完成复杂的原理图设计,而且语言的移植性可操作性比原理图设计强很多。

工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的。

逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。

在逻辑方面,我觉得比较重要的规范有这些:1.设计必须文档化。

要将设计思路,详细实现等写入文档,然后经过严格评审通过后才能进行下一步的工作。

这样做乍看起来很花时间,但是从整个项目过程来看,绝对要比一上来就写代码要节约时间,且这种做法可以使项目处于可控、可实现的状态。

2.代码规范。

如果在另一个设计中的时钟是40ns,复位周期不变,我们只需对CLK_PERIOD进行重新例化就行了,从而使得代码更加易于重用。

b.信号命名要规范化。

1)信号名一律小写,参数用大写。

2)对于低电平有效的信号结尾要用_n标记,如rst_n。

3)端口信号排列要统一,一个信号只占一行,最好按输入输出及从哪个模块来到哪个模块去的关系排列,这样在后期仿真验证找错时后方便很多。

4)一个模块尽量只用一个时钟,这里的一个模块是指一个module或者是一个entity。

4.如何提高电路工作频率对于设计者来说,我们当然希望我们设计的电路的工作频率(在这里如无特别说明,工作频率指FPGA片内的工作频率)尽量高。

我们也经常听说用资源换速度,用流水的方式可以提高工作频率,这确实是一个很重要的方法,今天我想进一步去分析该如何提高电路的工作频率。

我们先来分析下是什么影响了电路的工作频率。

我们电路的工作频率主要与寄存器到寄存器之间的信号传播时延及clock skew有关。

在FPGA内部如果时钟走长线的话,clock skew很小,基本上可以忽略, 在这里为了简单起见,我们只考虑信号的传播时延的因素。

信号的传播时延包括寄存器的开关时延、走线时延、经过组合逻辑的时延(这样划分或许不是很准确,不过对分析问题来说应该是没有可以的),要提高电路的工作频率,我们就要在这三个时延中做文章,使其尽可能的小。

我们先来看开关时延,这个时延是由器件物理特性决定的,我们没有办法去改变,所以我们只能通过改变走线方式和减少组合逻辑的方法来提高工作频率。

1.通过改变走线的方式减少时延。

以altera的器件为例,我们在quartus里面的timing closure floorplan可以看到有很多条条块块,我们可以将条条块块按行和按列分,每一个条块代表1个LAB,每个LAB里有8个或者是10个LE。

它们的走线时延的关系如下:同一个LAB中(最快)< 同列或者同行< 不同行且不同列。

我们通过给综合器加适当的约束(不可贪心,一般以加5%裕量较为合适,比如电路工作在100Mhz,则加约束加到105Mhz 就可以了,贪心效果反而不好,且极大增加综合时间)可以将相关的逻辑在布线时尽量布的靠近一点,从而减少走线的时延。

(注:约束的实现不完全是通过改进布局布线方式去提高工作频率,还有其它的改进措施)2.通过减少组合逻辑的减少时延。

上面我们讲了可以通过加约束来提高工作频率,但是我们在做设计之初可万万不可将提高工作频率的美好愿望寄托在加约束上,我们要通过合理的设计去避免出现大的组合逻辑,从而提高电路的工作频率,这才能增强设计的可移植性,才可以使得我们的设计在移植到另一同等速度级别的芯片时还能使用。

Floorplan注意事项Floorplan注意事项Floorplan的好坏直接决定了Design的成败,需要反复迭代找出最优三要素:Timing,Power, RoutableTiming:内部数据流向合理:横向对⽐出最佳⽅案,可根据No module情况使⽤最少量的module调整标准单元摆放density均匀合理,区域最好⼤⽚相连:设置module时注意TU,对Fence和Region注意 EU;过于密集可以设置区域density或者使⽤blockagePower:Block摆放井然有序,根据亲疏分布:使⽤ToolBox对Block与Module供电充分:power stripe摆好后检查微调⼀下它们的位置,followpin摆完不要随便移动,power plan后verify power via没有供电死⾓,贴边贴⾓摆放,⼤的Block之间channel要有与followpin正交的power stripe: power plan前后要仔细检查局部供电单元过多则增加Power Stripe,避免IR-drop太⼤:Power stripe通常是不规则和不均匀分布的Power rings保证均匀供电,可以避免Hot spot和EM等问题部分信号通过tie cell接到power上,提供ESD保护Routable:长条形Block尽量与最近电源线正交,否则会占⽤布线资源⾛线密度刚好达到congestion可以承受的上限:可以试探⼀下Block间的临界距离;Halo最⼩多少合适添加Blockage时要谨慎考虑:避免引起cut spacing,short等viols⼩的Block之间可以没有空间,设置Halo防⽌⼲扰:不要直接贴Block边靠着互连线很多的Block之间⼀般要留⼀些空间给std cell,因为跨过⼤的Block可能需要空间插buffer。