7

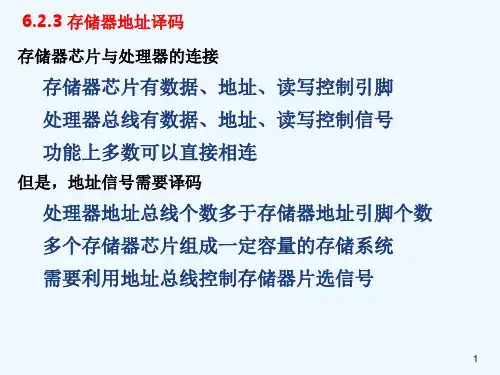

2. 译码器 3-8译码器:138译码器 3个控制输入引脚: G1,G2A*和G2B* 有些资料上 E3, E2* E1*

(我们的教材这样表示)

都有效,才能实现译码功能

3个编码输入引脚:C,B和A

8种编码各对应一个译码输出引脚 C B A=000编码使Y0*低有效,其他高电平无效 C B A=001编码使Y1*低有效,其他高电平无效 …… C B A=111编码使Y7*低有效,其它高电平无效E3

24

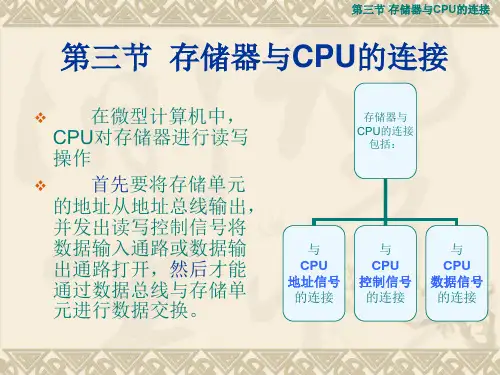

3. 8086的16位存储结构 对称的两个存储体(Bank)所构成 偶存储体(A0=0)

对应所有的偶地址单元 (0、2、4、……FFFEH) 接处理器低8位数据总线D7~D0

奇存储体(BHE*=0)

对应所有的奇地址单元 (1、3、5、……FFFFH) 接处理器高8位数据总线D15~D8

两个存储器芯片的片选端连接在一起

Y0 Y1 Y2 Y3

A17=0或1 A18=0 A19=0

2-4译码器

14

RD WR

A19 BHE A0 A18 D7~D0 A16~A1

D15~D8

M/IO

A16 A15 A15 A14 A2 A1 A1 A0

≥1

A17不参与译码

…

C Y0 Y1 Y2 Y3 A17=0或1 A18=0 A19=0 地址空间? A0

8

译码器74LS138

9

译码器译码 对于存储器访问,M/IO* =1,将该信号接到3-8译码器的G1 (E3)引脚,则只有执行存储器访问指令(存储器读或写指令) MOV mem, src MOV src, mem 时,存储器的地址译码器才有效。 在执行 端口访问指令 IN OUT 时,M/IO*=0,存储器译码器输出Y7*~Y0*全部无效(为1), 这样就将存储器地址与I/O端口地址区分开来。 一个例子如下: