06第六章输入-输出接口

- 格式:ppt

- 大小:180.00 KB

- 文档页数:24

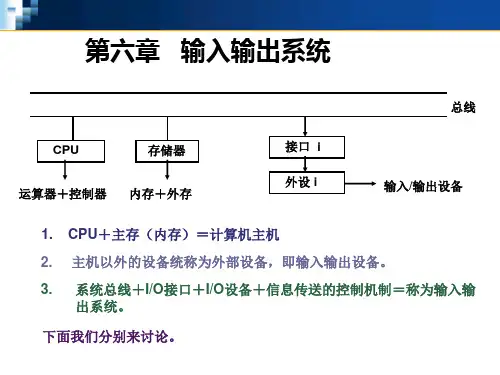

第六章I/O接口和总线本章介绍1.I/O接口I/O接口的功能简单的输入输出接口芯片I/O端口及其寻址方式CPU与外设间的数据传送方式 PC机的I/O地址分配2.总线IBM PC总线AT总线或ISA总线6-1、I/O接口一.I/O接口的功能1.采用I/O接口的必要性计算机和外设之间的信息交换带来一些问题:速度不匹配信号电平不匹配信号格式不匹配时序不匹配因此I/O设备不能直接与CPU的系统总线相连,必须在CPU与外设之间设置专门的接口电路来解决这些问题。

可编程输入输出接口芯片随着大规模集成电路技术的发展,出现了许多通用的可编程接口芯片,可用它们来方便地构成接口电路。

后面几章将介绍常见的可编程I/O接口芯片的原理、编程方法及与CPU的连接方法。

可编程中断控制器8259A可编程计数器/定时器8253可编程外围接口芯片8255A串行通信和可编程接口芯片8253AA/D和D/A转换芯片。

本章介绍最常用的简单I/O接口芯片,主要有缓冲器(Buffer)和锁存器(Latch)。

二、简单的输入输出接口芯片1.缓冲器74LS244和74LS245连接在总线上的缓冲器都具有三态输出能力。

在CPU或I/O接口电路需要输入输出数据时,在它的使能控制端EN(或G)作用一个低电平脉冲,使它的内部的各缓冲单元接通,即处在输出0或1的透明状态。

数据被送上总线。

当使能脉冲撤除后,它处于高阻态。

这时,各缓冲单元像一个断开的开关,等于将它所连接的电路从总线脱开。

74LS244和74LS245就是最常用的数据缓冲器。

除缓冲作用外,它们还能提高总线的驱动能力。

8个三态缓冲单元,分成两组,分别由门控信号为低电平时,数据传送;高电平时,输出高阻态。

单向缓冲器,只能从端。

OE 2.锁存器74LS3731. I/O端口1.数据端口(Data Port)用来存放CPU与外设之间交换的数据,长度一般为1-2个字节,主要起缓冲作用。

2.状态端口(Status Port)用来指示外设的当前状态。

第六章PL的基本原理及组成PL(Programmable Logic)是可编程逻辑器件,是一种集成电路芯片,由逐行可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)两种类型组成。

PL的基本原理是通过组合逻辑和时序逻辑的组合,根据用户的需求进行逻辑运算和控制,实现各种数字电路的功能。

PL器件根据所需要的功能和规模的不同,可以灵活地进行编程和配置。

PL的组成主要包括:1. 逻辑单元(Logic Elements):也称为查找表(Look-up Table),是PL中最基本的组件。

逻辑单元负责实现布尔函数和逻辑运算,每个逻辑单元可以实现多个逻辑门的功能。

2. 管理电路(Routing Circuitry):用于连接逻辑单元之间的信号线,将不同逻辑单元之间的输入和输出进行连接。

3. 配置存储器(Configuration Memory):用于存储逻辑单元的配置信息,包括逻辑单元的功能和连接方式。

配置存储器可以进行编程和擦除,以实现不同数字电路的配置。

4. 输入/输出接口(IO Interface):用于与外部系统进行通信,将外部信号输入到PL中,或将PL中的输出信号输出到外部系统中。

5. 时钟管理电路(Clock Management Circuitry):用于产生和管理时钟信号,控制逻辑单元的时序运算。

6. 测试和调试电路(Test and Debug Circuitry):用于进行PL器件的测试和调试操作,对逻辑运算结果进行验证。

PL的工作过程包括配置和工作两个阶段:1. 配置阶段:将用户设计好的逻辑电路的功能和连接方式编写成其中一种配置文件,通过编程器(Programmer)将配置文件写入配置存储器中。

在配置阶段,配置存储器被编程为实现特定的逻辑功能和连接方式。

2.工作阶段:在配置阶段完成后,PL器件进入工作阶段,根据配置存储器中的配置信息,逻辑单元开始进行逻辑运算和控制。

通过输入接口,PL器件接收外部信号,并根据配置存储器中的配置信息进行逻辑运算,输出结果通过输出接口输出到外部系统中。

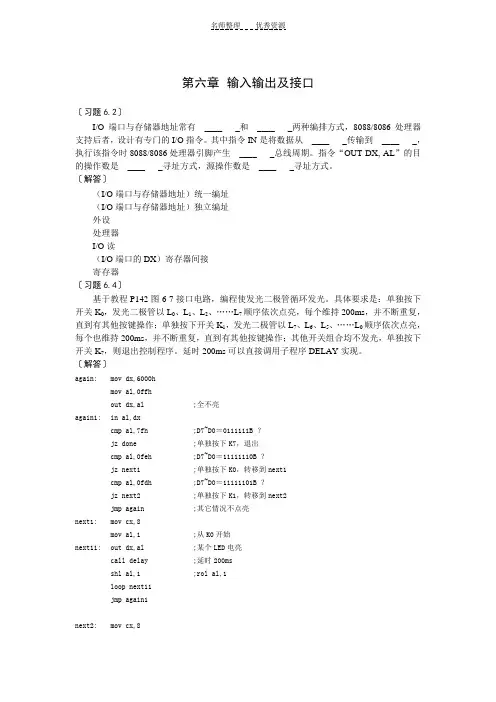

第六章输入输出及接口〔习题6.2〕I/O端口与存储器地址常有__⎽⎽⎽⎽___⎽和__⎽⎽⎽⎽___⎽两种编排方式,8088/8086处理器支持后者,设计有专门的I/O指令。

其中指令IN是将数据从__⎽⎽⎽⎽___⎽传输到__⎽⎽⎽⎽___⎽,执行该指令时8088/8086处理器引脚产生__⎽⎽⎽⎽___⎽总线周期。

指令“OUT DX, AL”的目的操作数是__⎽⎽⎽⎽___⎽寻址方式,源操作数是__⎽⎽⎽⎽___⎽寻址方式。

〔解答〕(I/O端口与存储器地址)统一编址(I/O端口与存储器地址)独立编址外设处理器I/O读(I/O端口的DX)寄存器间接寄存器〔习题6.4〕基于教程P142图6-7接口电路,编程使发光二极管循环发光。

具体要求是:单独按下开关K0,发光二极管以L0、L1、L2、……L7顺序依次点亮,每个维持200ms,并不断重复,直到有其他按键操作;单独按下开关K1,发光二极管以L7、L6、L5、……L0顺序依次点亮,每个也维持200ms,并不断重复,直到有其他按键操作;其他开关组合均不发光,单独按下开关K7,则退出控制程序。

延时200ms可以直接调用子程序DELAY实现。

〔解答〕again: mov dx,6000hmov al,0ffhout dx,al ;全不亮again1: in al,dxcmp al,7fh ;D7~D0=0111111B ?jz done ;单独按下K7,退出cmp al,0feh ;D7~D0=11111110B ?jz next1 ;单独按下K0,转移到next1cmp al,0fdh ;D7~D0=11111101B ?jz next2 ;单独按下K1,转移到next2jmp again ;其它情况不点亮next1: mov cx,8mov al,1 ;从K0开始next11: out dx,al ;某个LED电亮call delay ;延时200msshl al,1 ;rol al,1loop next11jmp again1next2: mov cx,8mov al,80h ;从K7开始next21: out dx,al ;某个LED电亮call delay ;延时200msshr al,1 ;ror al,1loop next21jmp again1done: mov al,0ffhout dx,al ;全不亮〔习题6.5〕有一个查询输入接口电路类似图6-9,但其数据端口为8F40H、状态端口为8F42H。

第六章输入/输出方式与接口芯片第一节输入/输出方式第二节中断第三节可编程定时/计数器8254及其应用第四节可编程并行I/O接口芯片8255A及其应用第五节可编程中断控制器8259及其应用第一节输入/输出方式●教学目标介绍I/O 接口的基本概念介绍I/O端口的编址方式介绍CPU与外设间的数据传送关系●学习要求掌握I/O接口的基本功能,了解接口的一般结构熟悉I/O端口的编址方式,了解IN/OUT指令的执行过程掌握微机与外设的各种传送方式,了解DMA传送过程一、I/O接口1)I/O接口的基本概念I/O接口是连接CPU与外设的逻辑控制部件,它主要在CPU与外设间起着传输状态与命令信息,实现数据的缓冲、数据格式转换等作用。

它的主要功能有:选择外设对外设进行控制和监视进行数据寄存和缓冲进行数据格式转换进行信号电平转换I/O接口的分类并行I/O接口和串行I/O接口可编程接口和不可编程接口专用接口和通用接口2)I/O接口的基本结构主要包含有数据端口、状态端口和控制端口数据端口用于存放数据信息,包括数据输入寄存器和数据输出寄存器,主要作用是协调CPU和外设之间的数据传输速度。

控制端口用于存放控制信息,控制信息是CPU通过接口传送给外设的,其主要作用是控制外设工作,如控制输入输出装置的启/停等。

状态端口用于存放状态信息,即反映外设当前工作的状态信息,CPU可通过读取这些信息,了解外设当前的工作情况。

3)I/O端口的寻址方式在一个微机系统中既有存储单元地址又有I/O端口地址,根据两者地址的不同安排可分为以下两种寻址方式。

存储器统一编址在这种方式中,把I/O端口作为存储器的一个单元来对待,即每个端口占用一个存储单元地址。

此时,对I/O端口操作可以使用全部的存储器指令,而不必另设专门的I/O指令。

由于该方式是将I/O地址映射到了存储器地址空间,所以也称为存储器映像方式。

I/O端口独立编址在这种方式下,I/O端口与存储器各自独立编址,这样存储器地址和I/O端口地址可以重叠。