第10章 DSP Builder设计深入

- 格式:ppt

- 大小:1.19 MB

- 文档页数:73

DSP Builder系统设计工具DSP Builder是Altera推出的一个数字信号处理(DSP)开发工具,它在Quartus Ⅱ FPGA设计环境中集成了MathWorks的Matlab和Simulink DSP开发软件。

Altera的DSP系统体系解决方案是一项具有开创性的解决方案,它将FPGA的应用领域从多通道高性能信号处理扩展到很广泛的基于主流DSP的应用,是Altera第一款基于C代码的可编程逻辑设计流程。

在Altera基于C代码的DSP设计流程中,设计者编写在Nios Ⅱ嵌入处理器上运行的C代码。

为了优化DSP算法的实现,设计者可以使用由Matlab和Simulink工具开发的专用DSP指令。

这些专用指令通过Altera的DSP Builder和SOPC Builder工具集成到可重配置的DSP设计中。

对DSP设计者而言,与以往FPGA厂商所需的传统的基于硬件描述语言(HDL)的设计相比,这种流程会更快、更容易。

除了全新的具有软件和硬件开发优势的设计流程之外,Altera DSP系统体系解决方案还引入了先进的S tratix和Stratix Ⅱ系列FPGA开发平台。

Stratix器件是Altera第一款提供嵌入式DSP块的FPGA,其中包括能够有效完成高性能DSP功能的乘法累加器(MAC)结构。

Stratix Ⅱ FPGA能够提供比Stratix器件高四倍的DSP带宽,更适合于超高性能DSP应用。

6.1 DSP Builder安装6.1.1 软件要求使用DSP Builder创建HDL设计需要有下面的软件支持:? Matlab 6.1或6.5版本;? Simulink4.1或5.0版本;? Quartus Ⅱ 2.0以上版本;? Synplify 7.2以上版本或LeonardoSpectrum 2002c以上版本(综合工具);? ModelSim5.5以上版本(仿真工具)。

6.1.2 DSP Builder软件的安装在安装DSP Builder之前,首先安装Matlab和Simulink软件以及Quartus Ⅱ软件。

电子131 XXX XXXXXX1、说明DSP Builder 的主要功能DSP Builder 是Altera 公司提供的一种DSP 系统设计工具,是Matlab/Simulink 设计工具和QuartusII 设计工具之间的一个桥梁,把Matlab/Simulink 中的DSP系统设计转化为HDL文件,在QuartusII 工具中实现到具体的器件中。

产生于Matlab\DSP Builder\Quartus II 流程的DSP 模块或其他功能模块可以成为单片FPGA 电路系统中的一个组成部分,担任某个局部电路的功能;通过Matlab\DSP Builder ,可以直接为Nios II 嵌入式处理器设计各类加速器,成为Nios II 系统的一个接口设备,与整个片内嵌入式系统融为一体。

DSP Builder 是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级和RTL 级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势。

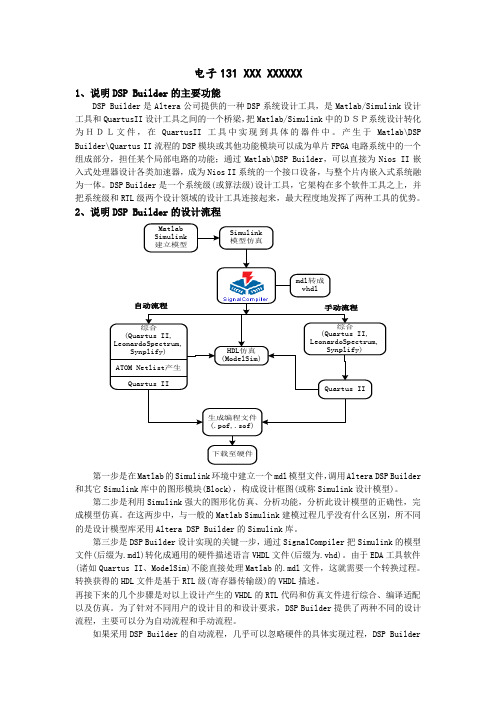

2、说明DSP Builder 的设计流程 Simulink 模型仿真综合(Quartus II,LeonardoSpectrum,Synplify)ATOM Netlist产生Quartus II HDL仿真(ModelSim)综合(Quartus II,LeonardoSpectrum,Synplify)Quartus II 生成编程文件(.pof,.sof)下载至硬件自动流程手动流程mdl转成vhdlMatlabSimulink建立模型第一步是在Matlab 的Simulink 环境中建立一个mdl 模型文件,调用Altera DSP Builder 和其它Simulink 库中的图形模块(Block),构成设计框图(或称Simulink 设计模型)。

第二步是利用Simulink 强大的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真。

1.说明DSP Builder的主要功能DSP Builder在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征,从而缩短了DSP设计周期。

已有的MATLAB函数和Simulink模块可以和Altera DSP Builder模块以及Altera知识产权(IP)MegaCore功能相结合,将系统级设计实现和DSP 算法开发相链接。

DSP Builder支持系统、算法和硬件设计共享一个公共开发平台。

设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件。

DSP Builder包括比特和周期精度的Simulink模块,涵盖了算法和存储功能等基本操作。

可以使用DSP Builder模型中的MegaCore功能实现复杂功能的集成。

Altera还提供DSP Builder高级模块集,这一Simulink库实现了时序驱动的Simulink综合。

Altera MegaCore是高级参数化IP功能,例如有限冲击响应(FIR)滤波器和快速傅立叶变换(FFT)等,经过配置能够迅速方便的达到系统性能要求。

MegaCore功能支持Altera的IP评估特性,使您在购买许可之前,便可以验证功能及其时序。

Altera IP MegaStore网站上为DSP Builder和IP评估流程提供DSP IP完整介绍DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

图示为DSP Builder设计流程。

DSP Builder是一个系统级(或算法级)设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势【10】。

DSP Builder依赖于Math Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可以在Simulink中进行图形化设计和仿真,同时又通过Signal Compiler可以把Matlab/Simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的TCL脚本。

基于dspbuilder的数字滤波器设计方法摘要:FPGA正在替代ASIC和PDSP用于前端数字信号处理的运算,采用FPGA进行算法运算比PDSP器件具有更高的效率,更低的成本和功耗。

文章以设计一个32阶fir滤波器为例,验证采用MATlab的DSPbuider工具可大大提高FPGA 编程效率,省去了底层代码编写时间,使设计者更专注于系统级算法的设计。

关键词:dspbuilder;FPGA;数字滤波器数字滤波器应用于修正或改变时域或频域中信号的属性,最普通的数字滤波器就是线性时间不变量(LTI)滤波器,LTI通过与输入信号相互作用经过线性卷积,表示为,其中f是滤波器的脉冲相应,x是输入信号,而y是卷积输出。

线性卷积过程的正式定义为:y[n]=x[n]※f[n]=x[k]f[n-k]=f[k]x[n-k] (1)1模块构建及仿真利用DSPbuilder进行滤波器算法设计,并进行仿真,需设置系统参数,构建信号处理模块、信号源、频谱分析及时波器等外围模块,以及仿真功能。

1.1设置系统参数在MATLAB中新建FIR_32tap_setup.m文件。

在其中设置如下:clock_freq = 100e6;sample_time = 1/clock_freq;clock_period = 1/(clock_freq*1e-9);fir_coeff = firpm(31,[0 0.1 0.2 0.5]*2,[1 1 0 0]);fir_coeff = round(fir_coeff.*(2-1));点击运行按钮,并关闭编辑器。

1.2外围激励的设计在simulink中新建FIR_32tap_ex2.mdl模块。

Sine Wave 0.33及sine wave 0.01分别产生两个正弦波信号,经过ADD模块叠加后输入Fir 32滤波器模块中进行处理,处理前的信号频谱可由input Spectrum观察,处理后的结果由scope模块显示模拟波形,频谱可由output Spectrum观察。

基于DSP Builder的高精度正弦信号发生器的设计闫璞【摘要】该文基于DSP Builder设计了一款新型高精度、高性能、宽频率范围的正弦信号发生器;通过DSP builder设计一个幅度调制模型使正弦波发生器产生的波形能够进行幅度调制.系统通过调试后,能成功产生正弦波形信号,其精度高、波形稳定、失真小.【期刊名称】《中国新技术新产品》【年(卷),期】2018(000)023【总页数】2页(P46-47)【关键词】信号发生器;DSP技术;DSP Builder【作者】闫璞【作者单位】兰州理工大学技术工程学院,甘肃兰州730050【正文语种】中文【中图分类】TN9110 前言在现代电子测量中,人们对于信号源的要求不断提高,除了频率准确度和稳定的要求外,还要求输出有较宽的频率范围和更高的稳定度和准确度。

本论文基于DSP Builder设计了一款新型高精度、高性能、宽频率范围的正弦信号发生器。

1 正弦信号发生器的预期要求及设计原理该文运用DSP Builder设计正弦波发生器和幅度调制器并将正弦波发生器产生的正弦波通过幅度调制器进行调制,预期达到的要求见表1。

表1 预期要求预期要求预期性能正弦波输出频率范围 10 Hz~10 MHz具有频率设置功能,频率步进 100 Hz输出信号频率稳定度优于10-4输出电压幅值无明显失真本设计中,为了一步步罗列DSP Builder 基于手动流程的的使用方法,我们列举了一个正弦波发生模块的设计,并且这个正弦波是可控的。

如图1所示是一个正弦波发生器。

图1 正弦波发生器模块原理图1.1 设计流程设计流程如下:1)打开 Matlab工作环境。

2)完成工作库的建立。

3)了解simulink 库管理器。

4)simulink 的模型文件。

5)放置 SignalCompiler。

6)添加 Increment Decrement模块。

7)设置 IncCount。

8)添加 SinLUT 模块:( LUT)。

基于DSP Builder的调频信号发生器一、设计要求利用DSP Builder设计一个能输出调频信号的DDS发生器。

1、调制信号由外部输入。

2、最大频偏30KHZ。

3、载波频率为100KHZ。

二、设计分析(1)Matlab/DSP Builder设计流程图一:DSP Builder设计流程图(2)DDS原理及参数DDS即Direct Digital Synthesizer,直接数字合成器,是从相位的概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器由相位累加器、加法器、波形存储器ROM、D/A转换器和低通滤波器LPF构成。

原理图如下:图二:DDS 原理框图其K 为频率控制字,P 为相位控制字、fc 为参考时钟频率,N 为相位累加器的字长,D 为ROM 数据位及D/A 转换器的字长。

相位累加器在时钟fc 的控制下以步长K 作累加,输出的N 位二进制码与相位控制字P 相加后作为波形ROM 的地址,对波形ROM 进行寻址,波形ROM 输出D 位的幅度码S (n )进D/A 转换器变成阶梯波S (t ),再经过低通滤波器平滑后就可以得到合成的信号波形。

相位寄存器每经过2N/M 个s f 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波的频率计算: 0f =M 2s N f 先确定系统的分辨率f ∆,最高输出频率max f ,相位累加器位数N ,频率控制字M 。

(3)FM 调制原理设调制信号为t A t m m m ωcos )(=,载波信号为)cos()(t A t V c c ω=,则调频信号为]sin cos[)(t m t A t S m f c FM ωω+=。

三、电路设计四、Simulink仿真仿真结果如下:由上图可清楚得看到,输出信号的频率随着调制信号的变化而变化。

在调制信号的波峰处,输出信号频率达到最大值130KHZ;相应的,在调制信号的波谷处,输出信号频率为最小值70KHZ。