第15讲DSPBuilder设计实例

- 格式:ppt

- 大小:970.00 KB

- 文档页数:18

DSP Builder系统设计工具DSP Builder是Altera推出的一个数字信号处理(DSP)开发工具,它在Quartus Ⅱ FPGA设计环境中集成了MathWorks的Matlab和Simulink DSP开发软件。

Altera的DSP系统体系解决方案是一项具有开创性的解决方案,它将FPGA的应用领域从多通道高性能信号处理扩展到很广泛的基于主流DSP的应用,是Altera第一款基于C代码的可编程逻辑设计流程。

在Altera基于C代码的DSP设计流程中,设计者编写在Nios Ⅱ嵌入处理器上运行的C代码。

为了优化DSP算法的实现,设计者可以使用由Matlab和Simulink工具开发的专用DSP指令。

这些专用指令通过Altera的DSP Builder和SOPC Builder工具集成到可重配置的DSP设计中。

对DSP设计者而言,与以往FPGA厂商所需的传统的基于硬件描述语言(HDL)的设计相比,这种流程会更快、更容易。

除了全新的具有软件和硬件开发优势的设计流程之外,Altera DSP系统体系解决方案还引入了先进的S tratix和Stratix Ⅱ系列FPGA开发平台。

Stratix器件是Altera第一款提供嵌入式DSP块的FPGA,其中包括能够有效完成高性能DSP功能的乘法累加器(MAC)结构。

Stratix Ⅱ FPGA能够提供比Stratix器件高四倍的DSP带宽,更适合于超高性能DSP应用。

6.1 DSP Builder安装6.1.1 软件要求使用DSP Builder创建HDL设计需要有下面的软件支持:? Matlab 6.1或6.5版本;? Simulink4.1或5.0版本;? Quartus Ⅱ 2.0以上版本;? Synplify 7.2以上版本或LeonardoSpectrum 2002c以上版本(综合工具);? ModelSim5.5以上版本(仿真工具)。

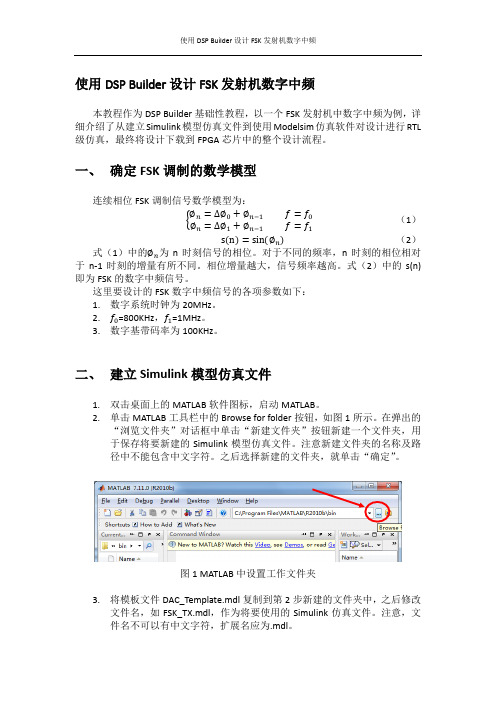

6.1.2 DSP Builder软件的安装在安装DSP Builder之前,首先安装Matlab和Simulink软件以及Quartus Ⅱ软件。

利用MatlabDSPBuilder实现DDS的设计匿簟受圈堕遵匿噩圜PLDCPLDFPGA设计与应用文章编号:1008-0570(2006)07—2_0211.02利用Matlab/DSPBuilder实现DDS的设计RealizestheDDSdesignusingMatlab/DSPBuilder(鼋庆文理学院)杨守良Yang。

¥houliang摘要:介绍了一种自行设计的基于HlGA芯片的DDS信号发生器设计的解班方案.根据DDS的基本原理.利用MaLlab/DSPBuilder建立DDS基本模型.熊詹利用AL'11ERA公司提供的Singacompler工具对其进行编译.产生QUARTUSII能够识别的VHDL源程序.并且格出了采用AUi'ERA公司的cyclone系列的FPGA芯片EPlCl2Q240C8进行直接数字频率各成器的实现方法.关键词:Matlab/DSPBuilder;FPGA:直接数字频率台成:设计中图分类号:TP271+.82文献标识码:AAbstract:IntroducedooekindindependentlydesignedthesolutionwhichsignalgeneratingdevicedesignedbasedonFPGAthechipDDS,accordingtotheDDSbasicprinciple,establishedtheDDSbasicmodelusingMatlah/DSPBuilder,thentheSingaeomplertoolwhichprovidedusingtheALTERACorporationtoitcarriesOHthetranslation,hasVHDLsourceprogramwhichQUARTUSHcoulddistinguish,andproducedusesAUI'ERACorporationcycloneseriesFPGAchipEPlCl2Q240G8carriesonthedirectdigitalfrequen—cysynthesizertherealizationmethod.Keywords:Matlab/DSPBuilder,FPGA,Directdigitalfrequencysynthesis,Designs1引言自1971年.美国学者J.Tierney等人撰写的“ADigitalFrequencySynthesizer”一文首次提出了以全数字技术实现数字频率合成以来,构成DDS元器件的速度的限制和数字化引起的噪声这两个主要缺点阻碍了DDS的发展与实际应用。

基于dspbuilder的数字滤波器设计方法摘要:FPGA正在替代ASIC和PDSP用于前端数字信号处理的运算,采用FPGA进行算法运算比PDSP器件具有更高的效率,更低的成本和功耗。

文章以设计一个32阶fir滤波器为例,验证采用MATlab的DSPbuider工具可大大提高FPGA 编程效率,省去了底层代码编写时间,使设计者更专注于系统级算法的设计。

关键词:dspbuilder;FPGA;数字滤波器数字滤波器应用于修正或改变时域或频域中信号的属性,最普通的数字滤波器就是线性时间不变量(LTI)滤波器,LTI通过与输入信号相互作用经过线性卷积,表示为,其中f是滤波器的脉冲相应,x是输入信号,而y是卷积输出。

线性卷积过程的正式定义为:y[n]=x[n]※f[n]=x[k]f[n-k]=f[k]x[n-k] (1)1模块构建及仿真利用DSPbuilder进行滤波器算法设计,并进行仿真,需设置系统参数,构建信号处理模块、信号源、频谱分析及时波器等外围模块,以及仿真功能。

1.1设置系统参数在MATLAB中新建FIR_32tap_setup.m文件。

在其中设置如下:clock_freq = 100e6;sample_time = 1/clock_freq;clock_period = 1/(clock_freq*1e-9);fir_coeff = firpm(31,[0 0.1 0.2 0.5]*2,[1 1 0 0]);fir_coeff = round(fir_coeff.*(2-1));点击运行按钮,并关闭编辑器。

1.2外围激励的设计在simulink中新建FIR_32tap_ex2.mdl模块。

Sine Wave 0.33及sine wave 0.01分别产生两个正弦波信号,经过ADD模块叠加后输入Fir 32滤波器模块中进行处理,处理前的信号频谱可由input Spectrum观察,处理后的结果由scope模块显示模拟波形,频谱可由output Spectrum观察。

基于DSP Builder的调频信号发生器一、设计要求利用DSP Builder设计一个能输出调频信号的DDS发生器。

1、调制信号由外部输入。

2、最大频偏30KHZ。

3、载波频率为100KHZ。

二、设计分析(1)Matlab/DSP Builder设计流程图一:DSP Builder设计流程图(2)DDS原理及参数DDS即Direct Digital Synthesizer,直接数字合成器,是从相位的概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器由相位累加器、加法器、波形存储器ROM、D/A转换器和低通滤波器LPF构成。

原理图如下:图二:DDS 原理框图其K 为频率控制字,P 为相位控制字、fc 为参考时钟频率,N 为相位累加器的字长,D 为ROM 数据位及D/A 转换器的字长。

相位累加器在时钟fc 的控制下以步长K 作累加,输出的N 位二进制码与相位控制字P 相加后作为波形ROM 的地址,对波形ROM 进行寻址,波形ROM 输出D 位的幅度码S (n )进D/A 转换器变成阶梯波S (t ),再经过低通滤波器平滑后就可以得到合成的信号波形。

相位寄存器每经过2N/M 个s f 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波的频率计算: 0f =M 2s N f 先确定系统的分辨率f ∆,最高输出频率max f ,相位累加器位数N ,频率控制字M 。

(3)FM 调制原理设调制信号为t A t m m m ωcos )(=,载波信号为)cos()(t A t V c c ω=,则调频信号为]sin cos[)(t m t A t S m f c FM ωω+=。

三、电路设计四、Simulink仿真仿真结果如下:由上图可清楚得看到,输出信号的频率随着调制信号的变化而变化。

在调制信号的波峰处,输出信号频率达到最大值130KHZ;相应的,在调制信号的波谷处,输出信号频率为最小值70KHZ。