MULTLAB DSPbuilder硬件模块设计

- 格式:doc

- 大小:4.93 MB

- 文档页数:30

DSP Builder系统设计工具DSP Builder是Altera推出的一个数字信号处理(DSP)开发工具,它在Quartus Ⅱ FPGA设计环境中集成了MathWorks的Matlab和Simulink DSP开发软件。

Altera的DSP系统体系解决方案是一项具有开创性的解决方案,它将FPGA的应用领域从多通道高性能信号处理扩展到很广泛的基于主流DSP的应用,是Altera第一款基于C代码的可编程逻辑设计流程。

在Altera基于C代码的DSP设计流程中,设计者编写在Nios Ⅱ嵌入处理器上运行的C代码。

为了优化DSP算法的实现,设计者可以使用由Matlab和Simulink工具开发的专用DSP指令。

这些专用指令通过Altera的DSP Builder和SOPC Builder工具集成到可重配置的DSP设计中。

对DSP设计者而言,与以往FPGA厂商所需的传统的基于硬件描述语言(HDL)的设计相比,这种流程会更快、更容易。

除了全新的具有软件和硬件开发优势的设计流程之外,Altera DSP系统体系解决方案还引入了先进的S tratix和Stratix Ⅱ系列FPGA开发平台。

Stratix器件是Altera第一款提供嵌入式DSP块的FPGA,其中包括能够有效完成高性能DSP功能的乘法累加器(MAC)结构。

Stratix Ⅱ FPGA能够提供比Stratix器件高四倍的DSP带宽,更适合于超高性能DSP应用。

6.1 DSP Builder安装6.1.1 软件要求使用DSP Builder创建HDL设计需要有下面的软件支持:? Matlab 6.1或6.5版本;? Simulink4.1或5.0版本;? Quartus Ⅱ 2.0以上版本;? Synplify 7.2以上版本或LeonardoSpectrum 2002c以上版本(综合工具);? ModelSim5.5以上版本(仿真工具)。

6.1.2 DSP Builder软件的安装在安装DSP Builder之前,首先安装Matlab和Simulink软件以及Quartus Ⅱ软件。

电子131 XXX XXXXXX1、说明DSP Builder 的主要功能DSP Builder 是Altera 公司提供的一种DSP 系统设计工具,是Matlab/Simulink 设计工具和QuartusII 设计工具之间的一个桥梁,把Matlab/Simulink 中的DSP系统设计转化为HDL文件,在QuartusII 工具中实现到具体的器件中。

产生于Matlab\DSP Builder\Quartus II 流程的DSP 模块或其他功能模块可以成为单片FPGA 电路系统中的一个组成部分,担任某个局部电路的功能;通过Matlab\DSP Builder ,可以直接为Nios II 嵌入式处理器设计各类加速器,成为Nios II 系统的一个接口设备,与整个片内嵌入式系统融为一体。

DSP Builder 是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级和RTL 级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势。

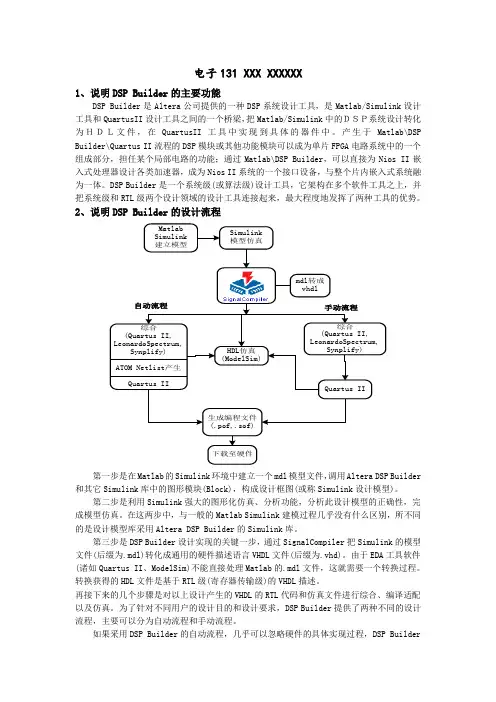

2、说明DSP Builder 的设计流程 Simulink 模型仿真综合(Quartus II,LeonardoSpectrum,Synplify)ATOM Netlist产生Quartus II HDL仿真(ModelSim)综合(Quartus II,LeonardoSpectrum,Synplify)Quartus II 生成编程文件(.pof,.sof)下载至硬件自动流程手动流程mdl转成vhdlMatlabSimulink建立模型第一步是在Matlab 的Simulink 环境中建立一个mdl 模型文件,调用Altera DSP Builder 和其它Simulink 库中的图形模块(Block),构成设计框图(或称Simulink 设计模型)。

第二步是利用Simulink 强大的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真。

基于Matlab/DSP Builder的正弦信号发生器设计引言近年来随着通信技术的不断发展,信号的正确传输显得日益重要,也就是说要有一个可靠的能产生稳定确信号的发生器,基于Matlab/DSP Builder的正弦信号发生器是利用Matlab/DSP Builder的模块进行的模快化设计,软件的设计采用模块化结构,使程序设计的逻辑关系更加简洁明了、易懂、易学。

使硬件在软件的控制下协调运作。

DSP Builder可以帮助设计者完成基于FPGA的DSP系统设计设计,除了图形化的系统建模外,还可以完成及大部分的设计过程和仿真,直至将设计文件下载到DSP 开发板上。

此次实验的目的就是将两者的优势有机的结合在一起,利用DSP的优势开发正弦信号发生器。

在设计中主要采用DSP Builder库中的模块进行系统的模型设计,然后再进行Simulink仿真。

1.设计思想1.1 DSP Builder特点DSP Builder系统级(或算法级设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模和RTL(硬件实现两个领域的设计工具连接起来,最大程度的发挥了两种工具的优势。

DSP Builder依赖于MathWorks公司的数学分析工具Matlab/Simulink,可以在Simulink中进行图形化设计和仿真,同时又通过Signal Compilder把Matlab/Simulink的设计文件(.mdl转换成相应的硬件描述语言VHDL 设计文件(.vhd,以及用于控制和编译的tcl脚本。

而对后者的处理可以用Quartus II 来实现。

1.2 QuartusII特点QuartusII提供了完整的多平台设计环境,能满足各种特定设计的需要,是单芯片可编程系统(SOPC设计的综合性环境和SOPC开发的基本设计工具,并且为Altera DSP开发包进行系统模型设计提供了集成综合环境。

QuartusII完全支持VHDL的设计流程,其内部嵌有VHDL逻辑综合器。

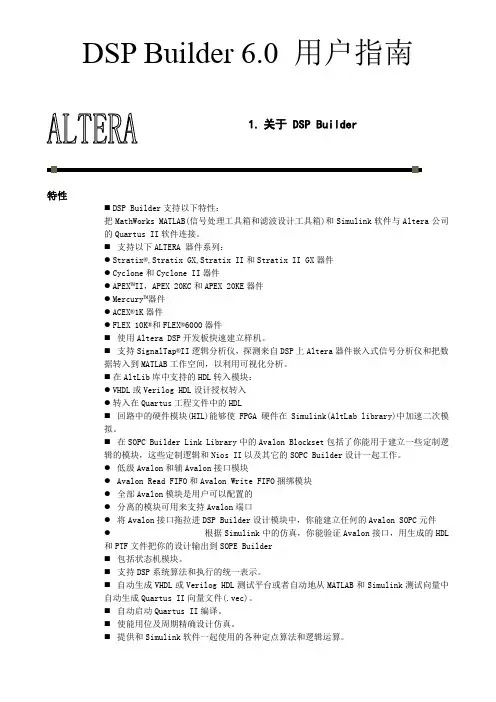

DSP Builder 6.0 用户指南1.关于 DSP Builder特性⏹DSP Builder支持以下特性:把MathWorks MATLAB(信号处理工具箱和滤波设计工具箱)和Simulink软件与Altera公司的Quartus II软件连接。

⏹支持以下ALTERA 器件系列:●Stratix®,Stratix GX,Stratix II和Stratix II GX器件●Cyclone和Cyclone II器件●APEX™II,APEX 20KC和APEX 20KE器件●Mercury™器件●ACEX®1K器件●FLEX 10K®和FLEX®6000器件⏹使用Altera DSP开发板快速建立样机。

⏹支持SignalTap®II逻辑分析仪,探测来自DSP上Altera器件嵌入式信号分析仪和把数据转入到MATLAB工作空间,以利用可视化分析。

⏹在AltLib库中支持的HDL转入模块:●VHDL或Verilog HDL设计授权转入●转入在Quartus工程文件中的HDL⏹回路中的硬件模块(HIL)能够使FPGA硬件在Simulink(AltLab library)中加速二次模拟。

⏹在SOPC Builder Link Library中的Avalon Blockset包括了你能用于建立一些定制逻辑的模块,这些定制逻辑和Nios II以及其它的SOPC Builder设计一起工作。

●低级Avalon和辅Avalon接口模块●Avalon Read FIFO和Avalon Write FIFO捆绑模块●全部Avalon模块是用户可以配置的●分离的模块可用来支持Avalon端口●将Avalon接口拖拉进DSP Builder设计模块中,你能建立任何的Avalon SOPC元件●根据Simulink中的仿真,你能验证Avalon接口,用生成的HDL和PTF文件把你的设计输出到SOPE Builder⏹包括状态机模块。

第9章DSP Builder设计初步利用EDA技术完成硬件设计的途径有多种,前面介绍的是利用QuartusII来完成的,最为典型的设计流程,包括设计项目编辑(如用VHDL)、综合、仿真、适配、编程。

但是对于一些特定的设计项目,这个流程就会显得很不方便,甚至无能为力。

例如涉及算法类(如DSP模块)及模拟信号处理与产生方面的系统设计。

Altera自2002年推出的DSP Builder则很好地解决了这些问题。

DSP Builder可以帮助设计者完成基于FPGA的不同类型的应用系统设计。

除了图形化的系统建模外,DSP Builder还可以自动完成大部分的设计过程和仿真,直至把设计文件下载至FPGA开发板上。

利用Matlab与DSP Builder进行模块设计也是SOPC技术的一个组成部分。

本章以两个简单的电路模型设计为示例,详细介绍Matlab、DSP Builder、QuartusII 三个工具软件联合开发的设计流程。

9.1 Matlab/DSP Builder及其设计流程DSP Builder是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模)和RTL级(硬件实现)两个设计领域的设计工具连接起来,都放在了Matlab/Simlink图形设计平台上,而将QuartusII作为底层设计工具置于后台,最大程度地发挥了对种工具的优势。

DSP Builder依赖于MathWorks公司的数学分析工具Matlab/Simlink,以Simulink的Blockset出现。

可以在Simulink中进行图形化设计和仿真,同时又通过SignalCompiler把Matlab/Simulink的模型设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的tcl脚本。

对于综合以及此后的处理都由QuartusII来完成。

由于在FPGA上设计一个算法模型的复杂性,设计的性能(包括面积、速度、可靠性、设计周期)对于不同的应用目标将有不同的要求,涉及的软件工具也不仅仅是Simulink和QuartusII,DSP Builder针对不同情况提供了两套设计流程,即自动流程和手动流程。

第六章Matlab/Dsp builder硬件模块设计Matlab是国内强大的数学分析工具,广泛用于科学计算和工程计算,还可以进行复杂的数字信号处理系统的建模、参数估计及性能分析。

Simulink是Matlab的一个组成部分,用于图形化建模仿真。

DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,它构架在多个软件工具之上,并把系统级(算法级建模)和RTL级(硬件实现)两个设计领域的设计工具连接起来放在Matlab/Simulink平台上,而将QuartrsⅡ作为底层设计工具置于后台,从而最大程度地发挥了这三种工具的优势。

DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,只要简单地进行DSP Builder工具箱中的模块调用即可。

Matlab/DSP Builder尤其适用于一些在Quartus Ⅱ上不方便完成或不能完成的设计项目(如涉及算法类及模拟信号处理与生产方面的系统处理)。

DSP Builder还可以自动完成大部分的设计过程和仿真,直到把设计文件下载到FPGA 中。

DSP Builder提供了Quartus® II软件和MATLAB/Simulink工具之间的接口。

其具有如下特性:1.用于连接Mathwork的MATLAB(信号处理工具箱和滤波器设计工具箱),Simulink环境和Altera® 的Quartus II设计软件环境。

2.支持Altera 的DSP核,这些核均可以从Altera的网站上下载(例如:FIR Compiler、Reed-Solomon Compiler等等)。

3.可以利用Altera的DSP开发板来快速的实现设计的原型。

4.支持SignalTap® II逻辑分析仪(一种嵌入式的信号分析仪,它可以探测到DSP开发板上Altera器件内部的信号,并把数据引入到MATLAB的工作区以便于进行可视化的分析)。

5.包括了用户可以创建的定制的逻辑,用于配合SOPC Builder和Nios® II嵌入式处理器设计。

6.包括了PLL块,用于多时钟设计。

7.包括了状态机块。

8.针对DSP系统的算法和实现,支持统一的表示方法。

9.根据MATLAB和Simulink的测试矢量,可以自动生成VHDL测试激励或Quartus II 矢量文件(.vec)。

10.自动调用VHDL综合器和Quartus II编译器。

11.仿真可以设定为比特或周期精度。

12.提供多种的定点运算和逻辑操作,用于配合使用Simulink 软件。

13.支持多种Altera 的器件: Stratix、Stratix II 和 Stratix GX 器件; Cyclone 和 Cyclone II 器件; APEXII、APEX 20KC 和 APEX 20KE 器件; Mercury器件; ACEX® 1K 器件; FLEX® 10K 和 FLEX 6000 器件。

利用Matlab和DSP Builder进行模块设计也是SOPC技术的一个组成部分。

这是由于利用Matlab/DSP Builder/QuartrsⅡ可完成纯硬件的DSP算法模型及实现,从而构成嵌入式系统外围接口的协处理模块,再进一步构成软件程序中的精简指令,DSP模块或其他功能模块可以成为单片FPGA电路系统中的一个组成部分,而且通过Matlab/DSP Builder,可以直接为Nios嵌入式处理器设计各类加速器,并以指令的形式加入到Nios的指令系统,从而成为Nios系统的一个接口设备,与整个片内嵌入式系统融为一体。

即利用DSP Builder和基本的Nios CPU,用户可以根据项目的要求,自己构建自己需要的DSP处理系统。

本章主要介绍利用Matlab/ DSP Builder/QuartrsⅡ三个工具软件联合开发的设计流程。

图6—1为Matlab/DSP Builder/QuartrsⅡ联合应用框图。

由图6—1可见,设计流程从利用建立DSP电路模型开始,电路模型的建立可以是图形化的,利用Simulink和DSP Builder中提供的丰富的功能模块和IP核进行设计。

DSP Builder 中包含了算术和存储功能等设计模块以及IP库中的许多复杂功能模块。

电路中的功能模块和IP的技术参数、数据格式、数据类型和总线宽度等都可以直接设置。

电路模型设计完成后,可以进行系统级的模型仿真,这与目标器件和硬件系统没有关系,是基于算法的仿真。

下个步骤是利用置于Simulink电路模型界面的DSP Builder的SignalCompiler,将电路模型文件,即Simulink电路模块文件(.mdl)转换成RTL级的VHDL代码表述和工具命令语言(Tcl)脚本。

一旦获得转换好的VHDL描述,在Simulink中即可调用VHDL综合器了,目前可选用的综合器有QuartrsⅡ、LeonardoSpectru、和Synplify。

由它们生成底层网表文件。

在QuartrsⅡ进行编译优化的过程中,会产生两种详细记录电路硬件特点和优化方式的底层电路描述的中间网表文件,即ATOM Netlist。

然后调用QuartrsⅡ中的编译器,根据网表文件及设置的优化约束条件进行布线布局和优化设计的适配操作,最后生成编程文件和仿真文件(.pdf和.sof),它们可用于对目标器件的编程配置和硬件实现;与此同时可生成分别用于QuartrsⅡ的门级仿真文件和ModelSim的VHDL时序仿真文件,以及相应的VHDL仿真激励文件,以用于实时测试DSP系统的工作性能。

图6-1 基于Matlab/Dsp builder/QuartrsⅡ等工具6.1 DSP Builder元件库简介打开Matlab环境。

可以看到Matlab的主窗口界面被分割成三个窗口:命令窗口(Command Window)、工作区(Workspace)、命令历史(Command History)。

使Matlab的Current Directory指向所安装的DSPBuilder的Altlib文件夹,点击旁边的simulink图标打开simulink库,如下图6-2所示。

图6-2 Matlab的Current Directory在Simulink Library Browser的左面展开Altera DSP Builder可以看见DSP Builder 的元件库如图6-3所示,元件库可以分为若干部分。

其中有主控元件库(AltLab)、算术元件库(Arithmetic)、开发板库(Boards)、复元件库(Complex Type)、组合元件库(Gate &Control)、总线元件库(IO&Bus)、时钟元件库(Rate Change)、SOPC元件库(SOPC Builder Links)、状态机功能元件库(State Machine Functions)、时序元件和存储器元件库(Storage)、IP核元件库(MegaCore Function)、视频和图象处理元件库(Video and Image Processing)图6-3 DSP Builder元件库1、主控元件库(AltLab),包含一些用于控制的模块。

主要有:数据观察窗(BP)、FPGA 编程器(Device programmer)、HDL引入模块(HDL Import)、HDL子系统元件模块(HDL SubSystem)、HIL硬件环境模块(HIL)、逻辑分析仪探头(Node)、硬件工程参数设置模块(QuartusⅡ Global Project Assignment)、FPGA引脚锁定模块(QuartusⅡ Poinout Assignment)、MatLab模型至VHDL转换器(SignalCompiler)、逻辑分析仪(SignalTapⅡAnalysis)。

2、算术元件库(Arithmetic),包含一些与运算相关联的器件。

主要有比较器(Comparator)、计数器(Counter)、差分器(Differentiator)、除法器(Divider)、增益乘法器(Gain)、地址发生器(Incerement Decrement)、积分器(Integrator)、乘法器(Multiplier)、乘法累加器(Multiply Accumulate)。

如图6-4所示。

图6-4 算术元件库3、SOPC元件库(SOPC Builder Links),在左侧展开加号分别是SOPC AVALON总线模块、SOPC AVALON总线端口模块和SOPC用户自定制指令端口。

如图6-5。

图6-5 SOPC元件库4、IP核元件库(MegaCore Function),包含Altera公司设计好的IP核。

可以使一般的设计者在不用全面了解所用IP核相关技术过多细节的情况下,在短期内设计符合要求的系统。

MegaCore是Altera的IP Core计划中的一个组成部分,IP核元件库所包含的IP核不附带在DSP Builder和QuartusⅡ中,需要单独购买。

如图6-6所示,IP核元件库主要有CIC IP核(cic)、FFT IP核(fft)、FIR IP核(fir)、NCO IP核(noc)、RS IP核、VITERBI IP核(viterbi)。

图6-6 MegaCore Function元件库6.2 FSK调制器设计二进制频率调制(2FSK),是利用二进制数字基带信号控制载波进行频谱变换的过程。

在发送端产生不同频率的载波震荡来传输数字信号“0”、“1”,在接收端,把不同频率的载波振荡还原成相应的数字基带信号。

FSK调制的方法有两种:1、直接调频法用数字基带矩形脉冲控制一个振荡器的某些参数,直接改变振荡频率,输出不同的频率信号。

2、频率键控法用数字矩形脉冲控制电子开关在两个振荡器之间进行转换,从而输出不同频率的信号。

6.2.1 建立设计模型1、们需要建立一个工作库,所以先新建一个文件夹FSK。

2、使Matlab的Current Directory指向所安装的DSPBuilder的Altlib文件夹点击上方的simulink图标打开simulink库,如下图6-7所示。

图6-7 Matlab的Current Directory3、在Simulink Library Browser 窗口中选择File菜单,在出现的菜单中选择New,在弹出的子菜单中选择新建模型model。

如图6-8图6-8 新建Model4、放置SignalCompilder。

点击simulink库管理器左侧的数形列表中的Altera DSP Builder条,使之展开DSPBuilder库,这时会出现一串树形列表,对DSPBuider的子模块(Block)进行分组,展开其中的Altlab,选择库管理器右侧的SignalCompilder,拖动到新的模型窗口。