电子秒表设计数字逻辑课程设计范本

- 格式:doc

- 大小:451.00 KB

- 文档页数:21

基于数字电路电子秒表课程设计摘要电子秒表是一种用数字电路技术实现时、分、秒计时的装置,无机械装置,具有较长的使用寿命,因此得到了广泛的使用。

它从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

本次实验所做电子式秒表由信号发生系统和计时系统构成,并具有清零,暂停功能。

由于需要比较稳定的信号,所以信号发生系统555定时器与电阻和电容组成的多谐振荡器构成,信号频率为100HZ。

计时系统由计数器、译码器、显示器组成。

计数器由74 LS160构成,由十进制计数器组成了一百进制和六十进制计数器,采用异步进位方式。

译码器由74LS48构成,显示器由数码管构成。

清零,暂停功能由RS触发器构成防抖动开关。

具体过程为:由晶体震荡器产生100HZ脉冲信号先进入计数器,然后传入译码器,将4位信号转化为数码管可显示的7位信号,结果以“分”、“秒”、“10毫秒”依次在数码管显示出来。

该秒表最大计时值为59分59.99秒,“10毫秒”为一百进制计数器组成,“分”和“秒”为六十进制计数器组成。

关键词:计时精度计数器显示器AbstractElectronic stopwatch is the realization of a digital circuit technology,.It can realize the hour, minute, second timer.It does not have mechanical means and has a longer life, so it has been widely used. The principle is a typical digital circuit, which includes a combination logic circuit and a timing circuit. The experiments can be done by electronic stopwatch constituted by the signal system and timing system, and has cleared pause function. Due to the need of a more stable signal, the signal generating system is constituted by the 555 Timer with the resistors and capacitors, and the signal frequency is 100Hz. Timing system contains the counter, decoder, display. Counter 74 LS160 constituted by the decimal counter the decimal and sexagesimal counter, which uses asynchronous binary. The decoder from 74LS48 constitute display digital tube constitute Cleared, the pause function by the RS flip-flop. Its specific process: the 100Hz pulse signal generated by the crystal oscillator and first into the counter, and then the incoming decoder, a 4-bit signal is converted to 7-bit signal of the digital control can be displayed, the result by "minute", "second", "10 milliseconds" turn on the digital display. The stopwatch timing is 59 minutes, 59.99 seconds, 10 milliseconds is the 150 binary counter, "minute" and "second" is the six decimal counter.Keyword:Timing accuracy counter display目录一、设计任务与要求 (2)二、方案设计与论证 (2)三、单元电路设计与参数计算 (4)1.信号发生器单元电路 (4)2.时钟分频计数单元电路 (6)3.显示及译码单元电路 (11)4.控制电路 (13)四、总原理图及元器件清单 (14)五、结论与心得 (17)六、参考文献 (18)一、设计任务与要求用74系列数字器件设计一个电子秒表,要求:1.以0.01秒为最小单位进行显示。

电子秒表设计课程设计一、课程目标知识目标:1. 学生能理解电子秒表的基本原理和功能,掌握计时器的工作流程。

2. 学生能够运用所学的电子元件和电路知识,设计并搭建一个简易的电子秒表。

3. 学生能够解释电子秒表中涉及的时间单位,如秒、分、时,并掌握它们之间的换算关系。

技能目标:1. 学生能够运用问题解决和团队合作的能力,完成电子秒表的电路设计和组装。

2. 学生通过实际操作,提升动手能力和实验技能,能够准确使用工具进行电子电路的搭建。

3. 学生能够通过编写简单程序或使用相关软件,实现对电子秒表的编程和功能调试。

情感态度价值观目标:1. 学生培养对电子技术和创新实践的热爱,增强对科学探究的兴趣。

2. 学生在学习过程中,发展耐心、细心和责任感,认识到精确计时在科学研究和技术发展中的重要性。

3. 学生通过小组合作,培养团队协作精神,尊重他人意见,学会共同解决问题。

课程性质:本课程是一门实践性与理论性相结合的综合性课程,旨在通过实际操作,使学生理解电子计时器的原理和应用。

学生特点:考虑到学生年级特点,他们已经具备一定的物理知识和动手能力,但需进一步培养创新思维和实际应用技巧。

教学要求:教学中应注重理论与实践的结合,鼓励学生主动探索,注重培养学生解决实际问题的能力和科学探究精神。

通过具体的学习成果,将课程目标转化为可观察、可评估的指标,为教学设计和评估提供依据。

二、教学内容本课程教学内容主要包括以下几部分:1. 电子秒表原理介绍:讲解计时器的基本工作原理,如振荡器、计数器、时钟脉冲等,关联课本第三章关于数字电路的内容。

2. 电子元件认知:学习常用电子元件如电阻、电容、二极管、三极管等,并了解它们在电子秒表中的作用,对应课本第二章电子元件的知识点。

3. 电路设计与搭建:根据电子秒表的功能需求,设计电路图,选用合适的电子元件进行电路搭建,结合课本第四章的电路设计原理。

4. 程序编写与调试:学习编写简单的程序或使用相关软件,实现对电子秒表的编程和功能调试,关联课本第五章关于微控制器的基础知识。

数电课程设计:电子秒表

电子秒表是一种常见的计时工具,它通过使用电子元件实现高精度的计时功能。

下面是一个基于数电的电子秒表的设计方案:

1. 运算部分设计:

- 使用一个1Hz的时钟源,可以通过计数器或者振荡器实现。

- 使用一个可重置的二进制计数器,位数根据需要的计时范

围确定。

例如,如果计时范围为1小时,可使用一个4位二进制计数器。

- 计时开始/停止控制逻辑:这可以通过一个开关电路实现,可以使用一个门电路或者触发器电路。

- 计数器重置逻辑:可以使用一个按钮或者开关来重置计数

器的值。

2. 显示部分设计:

- 使用数码管或者液晶显示器来显示计时结果。

数码管可以

使用共阳或者共阴的7段数码管。

- 使用译码器将计数器的二进制输出转换为译码信号,用于

控制数码管显示的数字。

3. 其他功能:

- 可以添加一个暂停功能,通过一个按钮或者开关来实现。

当计时中按下暂停按钮时,计时器会停止计数,再次按下暂停

按钮时,计时器继续计数。

- 可以添加一个拆表功能,通过一个按钮或者开关来实现。

按下拆表按钮时,计时器会记录当前的计时值,然后重置为0,再次按下拆表按钮时,计时器恢复原来的计时状态。

该设计方案中的电子秒表可根据实际需求进行调整和扩展,例如增加更多的功能按钮、调整计时范围和精度等。

同时,需要注意电路的稳定性和可靠性,以及对供电电源和信号的处理。

数字电子技术课程设计电子秒表数字电子技术课程设计报告题目:电子秒表的设计专业:班级:姓名:指导教师:课程设计任务书学生班级:学生姓名:学号:设计名称:电子秒表的设计起止日期:指导教师:周珍艮设计要求:1、明确设计题目,确定方案。

对于考虑的方案,经过比较后,确定选择哪个方案。

2、单元电路的设计和元器件的选择。

要列出元器件清单3、画出完整的电路原理图和必要的波形图,并说明主要工作原理。

4、计算出各元器件的主要参数,并标在电路图中恰当的位置。

5、画出电路图。

6、对电路性能进行测试,并分析是否满足要求。

7、按要求撰写课程设计报告。

报告内容包括目录、正文(概述,硬件原理图介绍,需要的元器件清单)、结论(设计的电路性能测试及总结,设计过程中遇到的问题及解决方法,心得等)、参考文献、附录(可有可无)等。

目录绪论- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 4第一章、设计要求1.1设计任务及目的- - - - - - - - - - - - - - - - - - - - - - -- - - - - - - - -51.2 系统总体框图- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 51.3、设计方案分析- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -6第二章、电路工作原理及相关调试2.1 电路工作原理- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 72.1相关调试- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -- 11第三章、实验总结附录A 电子秒表原理图附录B 相关波形元件清单参考文献绪论随着电子技术的发展,电子技术在各个领域的运用也越来越广泛,渗透到人们日常生活的方方面面,掌握必要的电工电子知识已经成为当代大学生特别是理工类大学生必备的素质之一。

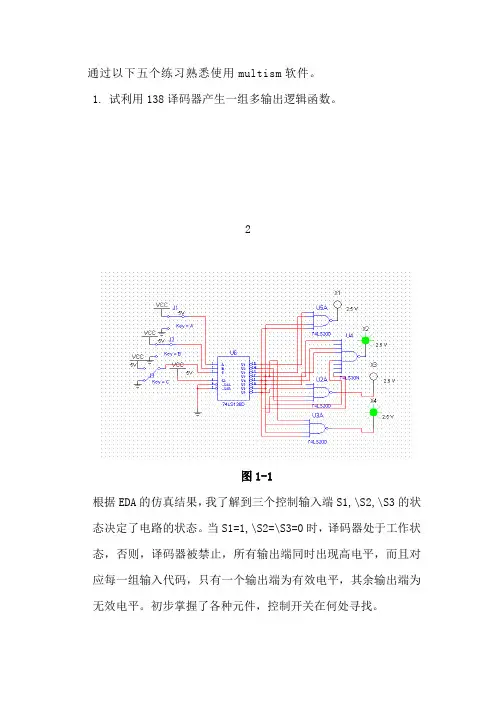

通过以下五个练习熟悉使用multism软件。

1.试利用138译码器产生一组多输出逻辑函数。

2图1-1根据EDA的仿真结果,我了解到三个控制输入端S1,\S2,\S3的状态决定了电路的状态。

当S1=1,\S2=\S3=0时,译码器处于工作状态,否则,译码器被禁止,所有输出端同时出现高电平,而且对应每一组输入代码,只有一个输出端为有效电平,其余输出端为无效电平。

初步掌握了各种元件,控制开关在何处寻找。

2.利用JK触发器构成同步计数器,初态Q3Q2Q1=000.3图1-2通过连接电路及仿真运行,我了解了利用JK触发器构成计数器的原理,同时也了解到触发器的次态仅取决于此时刻输入信号的状态,而其他时刻输入信号的状态对触发器的状态没有影响。

3.555定时器构成的多谐振荡器。

4图1-3通过连接电路及运行仿真,了解到了555定时器构成多谐振荡器产生方波的原理,在实验中我们组成员经过耐心查找,终于在同一示波器中显示输入输出波形。

4.基本放大电路——分压式射极偏置电路5图1-45.实用精密检波放大电路。

图1-5三.通过使用multism软件设计一个能显示1s为最小单位的电子秒表。

1.设计目的:(1)了解计时器主体电路的组成及工作原理;(2)熟悉集成电路及有关电子元器件的使用;(3)学习数字电路中基本555定时器、时钟发生器及计数、译码显示等单元电路的综合应用。

2.设计任务及说明:电子秒表电路是一块独立构成的记时集成电路。

它集成了计数器、、振荡器、译码器和驱动等电路,能够对秒以下时间单位进行精确记时,具有清零、启动计时、暂停计时及继续计时等控制功能。

3.功能要求(1)设计一个具有时、分、秒的数字显示计时器(2)具有校时、校分的功能(3)通过开关功能实现清零、暂停等功能的有效转换设计一个可以满足以下要求的简易秒表(1)秒表由5位七段LED显示器显示,其中一位显示“min”,四位显示“s”,其中显示分辩率为0.01 s。

目录1.引言1.1设计目的-------------------------------------------------------2 1.2设计内容-------------------------------------------------------2 1.3设计要求-------------------------------------------------------2 2.数字电子秒表设计2.1仪器设备-------------------------------------------------------3 2.2设计原理-------------------------------------------------------32.3电路设计及仿真-------------------------------------------------33.电路的硬件验证--------------------------------------------------104.心得体会---------------------------------------------------------125.参考文献---------------------------------------------------------121.引言1.1设计目的:(1)掌握同步计时器74160、74161的使用方法,并理解其工作原理。

(2)掌握74160、74161进行计数器、分频器的设计方法。

(3)掌握用三态缓冲器74244和74160,74138,7448进行动态显示扫描电路设计的方法。

(4)掌握电子秒表的设计方法。

(5)掌握在EDA系统软件MAX+plusII环境下用FPGA/CPLD进行数字系统设计的方法,掌握该环境下功能仿真、时序仿真、管脚锁定的芯片下载的方法。

(6)掌握用EDA硬件开发系统进行硬件验证的方法。

数字逻辑课程设计_秒表一、教学目标本课程旨在让学生掌握秒表的基本原理和使用方法,培养学生的数字逻辑思维和实际操作能力。

具体目标如下:1.知识目标:学生能够理解秒表的工作原理,包括时间计算、计数器等基本概念。

2.技能目标:学生能够熟练使用秒表进行时间测量和计数,并能进行简单的故障排查和维修。

3.情感态度价值观目标:通过学习秒表,培养学生对科学技术的兴趣和好奇心,提高学生的问题解决能力和团队合作意识。

二、教学内容本课程的教学内容主要包括以下几个部分:1.秒表的基本原理:介绍秒表的工作原理,包括时间计算、计数器等基本概念。

2.秒表的使用方法:教授学生如何正确使用秒表进行时间测量和计数,包括操作步骤和注意事项。

3.秒表的故障排查和维修:培养学生对秒表故障的识别和解决能力,包括常见故障的原因和维修方法。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用多种教学方法:1.讲授法:教师通过讲解秒表的基本原理和使用方法,让学生掌握相关知识。

2.讨论法:学生分组讨论秒表的使用心得和故障解决经验,促进学生之间的交流和合作。

3.案例分析法:教师提供一些实际的案例,让学生分析并解决秒表的使用问题,培养学生的实际操作能力。

4.实验法:学生在实验室进行秒表的操作和实践,加深对秒表的理解和掌握。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将准备以下教学资源:1.教材:选择合适的秒表教材,为学生提供系统的学习资料。

2.参考书:提供一些相关的参考书籍,供学生进一步深入学习。

3.多媒体资料:制作一些教学视频和演示文稿,帮助学生更好地理解秒表的工作原理和使用方法。

4.实验设备:准备一些秒表和相关实验设备,让学生进行实际操作和实验。

五、教学评估为了全面、客观、公正地评估学生的学习成果,本课程将采用以下评估方式:1.平时表现:通过观察学生在课堂上的参与程度、提问回答、小组讨论等表现,评估其学习态度和理解能力。

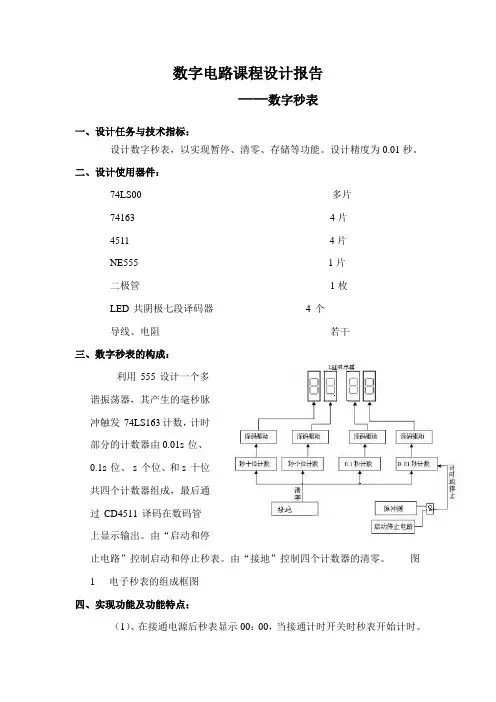

数字电路课程设计报告——数字秒表一、设计任务与技术指标:设计数字秒表,以实现暂停、清零、存储等功能。

设计精度为0.01秒。

二、设计使用器件:74LS00 多片74163 4片4511 4片NE555 1片二极管1枚LED 共阴极七段译码器 4 个导线、电阻若干三、数字秒表的构成:利用555 设计一个多谐振荡器,其产生的毫秒脉冲触发74LS163计数,计时部分的计数器由0.01s 位、0.1s 位、s 个位、和s 十位共四个计数器组成,最后通过CD4511 译码在数码管上显示输出。

由“启动和停止电路”控制启动和停止秒表。

由“接地”控制四个计数器的清零。

图1 电子秒表的组成框图四、实现功能及功能特点:(1)、在接通电源后秒表显示00:00,当接通计时开关时秒表开始计时。

(2)、清零可在计时条件下也可在暂停条件下进行。

(3)、解决了在使用163清零端和保持端时由于163默认的清零端优先级高于保持端造成的0.01秒位上无法保持到0.09的技术问题。

(4)、增加了数据溢出功能,由于是4位秒表,最多计到一分钟,当秒表到达一分钟时,秒表自动暂停显示在60:00秒处,此时二极管发亮,起警示灯作用。

清零后则可继续计时。

(5)、由于条件有限,我们自己用导线制作了电源、清零、暂停等开关以减少导线的拔插造成的面板的不美观。

下图为完整课程设计的实物图:五、课程设计原理:本课程设计由模6000计数器和其控制电路组成,模6000计数器功能由同步加法计数器74163和与非门74LS00组成。

74163的功能及用法:74163同步加法计数器具有以下功能:(1)、同步清零功能。

当清零端输入低电平,还必须有时钟脉冲CP的上升沿作用才能使各触发器清零,此过程为同步清零。

(2)、同步并行置数功能。

(3)、同步二进制加计数功能。

(4)、保持功能。

综上所述,74163是具有同步清零、同步置数功能的4位二进制同步计数器。

74163的应用:(1)、构成任意模的计数器将74163与少量门电路结合可构成任意模计数器。

第一章实验概述1.1实验设计任务1.1.1 设计任务1. 设计一个电子秒表,可显示4位数,计时范围0——10分钟2. 显示精确到0.1秒,对0.01秒进行四舍五入3. 有暂停、启动、恢复和连续功能,显示板由发光二极管构成2.1 实验目的与设计要求2.1.1 实验目的1. 学习数字电路基本RS触发器、单稳态触发器、时钟发生器、计数器以及译码显示器等单元电路的综合应用;2. 了解电子秒表的组成与工作原理;3. 熟悉中规模集成电路的应用;4. 掌握电子秒表的设计、调试以及故障排除方法;5. 培养书写综合实验报告的能力。

2.1.2 设计要求1. 根据设计任务要求,综合运用数字电子技术课程中所学到的理论知识与实践技能独立完成设计课题。

2. 根据课题查阅书籍,独立思考,深入研究课程设计中遇到的问题,培养自己分析、解决问题的能力。

3. 根据设计要求,从选择设计方案开始,首先按单元电路进行设计,选择合适的元器件,最后画出总的电路图。

4. 学会电子电路的连线安装和调试技能,最终实现任务要求的全部功能;电路布局合理,走线清楚,工作可靠。

5. 写出完整的实验报告,调试中出现的异常现象的分析与讨论。

第二章 电子秒表的设计过程2.1 电路的设计与元件的选择2.1.1 总体方案的设计图 2.1电子秒表一般由振荡器、分频器、计数器、译码器、显示器等几部分组成。

其中振荡器和分频器组成标准秒信号发生器,由不同进制的计数器、译码器和显示器组成计时系统。

信号送入计数器,累计结果以分、秒、分秒的数字显示出来,分、分秒由十进制计数器构成,秒由六十进制计数器构成。

其原理框图(如图2.1)脉冲发生电路振荡器 分频器计数器显示译码 显示显示显示译码 译码 译码分计数 秒十计数 秒个计数 分秒计数四舍五入控制电路2.1.2 所需元件的选择1. 二输入与门、二输入与非门、二输入或门、反相器2. 多谐振荡器:f=100Hz(集成555定时器的应用)(如图2.2)振荡周期T=0.7(R1+2R2)C,调节滑动变阻R2可输出不同的频率的脉冲信号;此振荡器在电路中是为分频器和四舍五入电路提供脉冲信号。

数字电子课程设计报告题目名称:电子秒表电路姓名:李美柳学号:1003741104班级:电子101班指导老师:刘纯天2012年6月(1)计时范围:0~59秒(2)显示分辨率为1s。

(3)用按钮开关控制工作状态,即:暂停、清零。

(4)本身带有,工作时指示灯亮。

二、元件清单:三、详细设计:(1)秒脉冲的产生CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC 或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

D 2Q5CLK3Q6S4R1U2:A74HC74CLK 1E 2MR 7Q03Q14Q25Q36U3:A4518CLK 9E 10MR 15Q011Q112Q213Q314U3:B4518图2-1脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器产生标准频率信号经过整形、分频获得1Hz的秒脉冲。

石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。

如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图2-1所示。

(2)秒计数器的设计十进制同步加法计数器CD4518CD4518/CC4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。

每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。

由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CLK信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。

RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。

秒表数电实验课程设计一、教学目标本课程旨在通过秒表数电实验,使学生掌握数字电路的基本知识和实验技能,培养学生的动手能力和实验素养。

具体目标如下:1.了解数字电路的基本概念和原理。

2.掌握基本逻辑门电路的组成和功能。

3.熟悉常用数字电路芯片及其应用。

4.了解秒表电路的工作原理。

5.能够运用Multisim等软件进行数字电路仿真实验。

6.能够独立完成数字电路实验,并进行故障排查。

7.能够根据实验结果,分析并优化电路性能。

情感态度价值观目标:1.培养学生对科学实验的兴趣和热情。

2.培养学生团队合作精神,提高沟通与协作能力。

3.培养学生诚实守信、勇于创新的科学精神。

二、教学内容本课程的教学内容主要包括以下几个部分:1.数字电路基本概念和原理。

2.基本逻辑门电路的组成和功能。

3.常用数字电路芯片及其应用。

4.秒表电路的工作原理及设计。

5.数字电路实验操作及故障排查。

三、教学方法为了提高教学效果,本课程将采用多种教学方法相结合的方式进行教学:1.讲授法:用于讲解数字电路的基本概念、原理和常用芯片。

2.实验法:通过动手实验,使学生掌握数字电路的组成和功能。

3.讨论法:分组讨论实验结果,培养学生的团队协作能力。

4.案例分析法:分析实际案例,提高学生解决实际问题的能力。

四、教学资源为了保证教学质量,我们将准备以下教学资源:1.教材:《数字电路实验教程》。

2.参考书:《数字电路原理与应用》。

3.多媒体资料:实验操作视频、PPT课件等。

4.实验设备:数字电路实验箱、秒表、逻辑门电路芯片等。

以上教学资源将为实现本课程的教学目标提供有力支持。

五、教学评估为了全面、客观地评估学生的学习成果,本课程将采用以下评估方式:1.平时表现:通过课堂参与、提问、讨论等环节,评估学生的学习态度和积极性。

2.作业:布置适量作业,评估学生对课堂所学知识的掌握程度。

3.实验报告:评估学生在实验过程中的操作技能和问题解决能力。

4.期末考试:全面测试学生对本课程知识的掌握情况。

秒表计时器数字逻辑课程设计

一、设计目的

通过设计并制作一个秒表计时器,使学生掌握数字逻辑电路的基本原理,熟悉常见数字逻辑门电路的特性和应用,培养实际动手能力和解决问题的能力。

二、设计任务

设计一个具有启动、停止和重置功能的秒表计时器;

使用数字逻辑门电路实现计时器的控制逻辑;

设计一个显示电路,用于显示计时器的计数值;

编写控制程序,实现计时器的自动计时、停止和重置功能。

三、设计步骤

确定计时器的功能需求,设计控制逻辑电路;

选择合适的数字逻辑门电路,如与门、或门、非门等;

设计显示电路,选择合适的显示器,如LED数码管;

编写控制程序,实现计时器的自动计时、停止和重置功能;

搭建实验电路,测试计时器的功能是否符合设计要求;

优化和完善设计,确保计时器稳定可靠地工作。

四、设计要求

设计过程中要充分考虑实际应用的需求,注重实用性和可靠性;

设计过程中要注重电路的优化和简化,降低成本和功耗;

编写程序时要注重代码的可读性和可维护性,遵循良好的编程规范。

五、总结

通过本次课程设计,学生可以深入了解数字逻辑电路的基本原理和应用,掌握常见数字逻辑门电路的特性和应用,提高实际动手能力和解决问题的能力。

同时,学生还可以学习到如何根据实际需求进行电路设计和程序编写,为后续的学习和工作打下坚实的基础。

数电电子秒表课程设计一、课程目标知识目标:1. 让学生理解数字电子秒表的基本原理和组成,掌握其工作流程。

2. 使学生掌握数字电子秒表的计数、计时和清零功能,并能运用相关电子元件实现这些功能。

3. 让学生掌握数字电子秒表中各个电子元件的作用,如晶振、计数器、时钟发生器等。

技能目标:1. 培养学生运用所学知识,设计并搭建一个简单的数字电子秒表电路。

2. 培养学生通过编程,实现对数字电子秒表的计数、计时和清零功能的控制。

3. 培养学生运用调试工具,对数字电子秒表电路进行调试和优化。

情感态度价值观目标:1. 培养学生对电子技术的兴趣,激发其探索精神和创新意识。

2. 培养学生团队合作精神,学会在团队中共同解决问题,共同进步。

3. 培养学生严谨的科学态度,养成良好的实验操作习惯。

本课程针对高中年级学生,结合电子技术课程内容,注重实践操作和理论知识相结合。

课程性质为实践性较强的设计课程,要求学生在掌握基本原理的基础上,能够运用所学知识,动手设计和搭建数字电子秒表电路。

通过本课程的学习,学生将能够达到上述课程目标,为后续深入学习电子技术打下坚实基础。

二、教学内容本章节教学内容紧密围绕课程目标,结合电子技术课程相关章节,组织以下内容:1. 数字电子秒表原理:讲解数字电子秒表的组成、工作原理,涉及晶振、时钟发生器、计数器等关键元件的作用。

2. 电路设计与搭建:学习如何设计数字电子秒表的电路,选择合适的电子元件,并按照电路图进行搭建。

3. 编程与控制:学习编写程序,实现对数字电子秒表的计数、计时和清零功能。

4. 调试与优化:教授学生如何使用调试工具,对搭建的数字电子秒表电路进行调试,找出并解决问题。

具体教学安排如下:1. 第一周:介绍数字电子秒表的原理,讲解相关电子元件的作用,让学生初步了解课程内容。

2. 第二周:详细讲解电路设计与搭建,指导学生动手实践,完成电路搭建。

3. 第三周:教授编程与控制方法,引导学生学习编写程序,实现数字电子秒表的基本功能。

数字电子技术课程设计报告题目:电子秒表的设计专业:班级:姓名:指导教师:课程设计任务书学生班级:学生姓名:学号:设计名称:电子秒表的设计起止日期:指导教师:周珍艮目录绪论- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 4 第一章、设计要求1.1设计任务及目的- - - - - - - - - - - - - - - - - - - - - - -- - - - - - - - -51.2 系统总体框图- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 51.3、设计方案分析- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -6第二章、电路工作原理及相关调试2.1 电路工作原理- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 72.1相关调试- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -- 11第三章、实验总结附录A 电子秒表原理图附录B 相关波形元件清单参考文献绪论随着电子技术的发展,电子技术在各个领域的运用也越来越广泛,渗透到人们日常生活的方方面面,掌握必要的电工电子知识已经成为当代大学生特别是理工类大学生必备的素质之一。

电子秒表是日常生活中比较常见的电子产品,秒表的逻辑结构主要由时基电路、分频器、二一五一十进制异步加法记数器、数据选择器和显示译码器等组成。

整个秒表需有一个清零/ 启动信号和一个停止/保持信号装置,以便秒表能随意停止及启动,计数器的输出全都为BCD码输出,方便显示译码器连接。

数电电子秒表课程设计一、课程目标知识目标:1. 理解数字电路基本原理,掌握电子秒表的基本组成及工作原理;2. 掌握计数器、定时器等数字电路的应用,能正确运用相关元器件搭建电子秒表;3. 学会分析电子秒表的电路图,并能进行简单的故障排查。

技能目标:1. 培养学生动手操作能力,能够独立完成电子秒表的搭建和调试;2. 培养学生运用所学知识解决实际问题的能力,提高创新意识和团队合作精神;3. 提高学生运用相关软件(如Multisim、Protel等)进行电路设计和仿真测试的能力。

情感态度价值观目标:1. 培养学生对电子技术的兴趣和热情,激发学生学习主动性和积极性;2. 培养学生严谨的科学态度,注重实验数据,遵循实验操作规程;3. 培养学生团结协作、互相帮助的精神,增强集体荣誉感和责任感。

课程性质分析:本课程为电子信息类学科,旨在让学生通过实际操作,掌握数字电路基础知识,培养实际动手能力。

学生特点分析:学生年级为高中二年级,具备一定的物理和数学基础,具有较强的逻辑思维能力和动手操作欲望。

教学要求:结合课程内容和学生的特点,注重理论与实践相结合,充分调动学生的主观能动性,培养实际操作能力和团队协作精神。

通过本课程的学习,使学生在知识、技能和情感态度价值观方面取得具体的学习成果,为后续相关课程的学习打下坚实基础。

二、教学内容1. 数字电路基础知识回顾:逻辑门电路、触发器、计数器原理;2. 电子秒表的原理与设计:秒表的计时原理、秒表电路的组成、各部分功能;3. 常用元器件介绍:集成电路、晶体振荡器、显示屏等;4. 电路图分析:学会分析电子秒表的电路图,理解各部分之间的连接关系;5. 搭建与调试:根据电路图,使用面包板或实验箱搭建电子秒表,并进行调试;6. 故障排查:学会分析搭建过程中可能出现的问题,进行故障排查;7. 仿真测试:运用Multisim、Protel等软件进行电路设计和仿真测试;8. 教学案例分享:分析优秀电子秒表设计方案,学习借鉴经验。

电子技术课程设计报告--电子秒表的设计一、设计目的本次课程设计的目的是设计一款电子秒表,实现具备暂停和复位功能的计时功能。

通过设计本次课程,我将学习到如何运用单片机实现计时功能,同时也将提高自己的电子设计能力。

二、设计原理本次设计采用AT89S52单片机作为控制芯片,通过单片机控制数码管的显示,完成对时间的计时和显示功能。

下面详细介绍如何实现设计的计时功能。

1、初始化:将计时器寄存器清零,并设置定时器为8位计时模式,同时设置时钟源为频率为12MHz的晶振。

2、启动计时:将定时器计数器初始值设置为0,同时启动计时器。

3、计时:定时器开始工作后,每过1ms,计时器的值就会加1,当计时器的值达到255时,定时器会自动清零,并触发定时溢出中断。

4、显示:将计时器的值传入程序中,经过处理后,将时间转化为时、分、秒、毫秒等信息,并通过数码管的显示完成时间的显示。

5、暂停功能:通过按下暂停键,可以停止计时器的工作,并记录下当前的计时时间。

6、复位功能:通过按下复位键,可以将计时器的值清零,并停止计时器的工作。

三、硬件设计1、主控芯片AT89S52单片机:采用AT89S52单片机作为控制核心,具有一定的处理能力和存储容量,能在实现计时功的同时,还实现一些其他的控制功能。

2、显示模块数码管:本设计采用了4位共阴数码管,能够完成对时间的显示。

3、按键模块本设计采用了两个按键,一个用于暂停功能,一个用于复位功能。

4、电源模块本设计采用了12V电源转接头,将12V电源转化为单片机和数码管所需要的5V电压。

5、其他零件晶振:采用12MHz的晶振作为单片机的时钟源。

电容:采用22pF电容和晶振配对使用,稳定时钟信号。

四、软件设计本设计采用Keil C51软件进行开发。

软件编写的主要思路如下:1、GPIO配置:定义IO口及初始化相关设置,如数码管的引脚及输出方向。

2、时钟初始化:配置外部晶振的时钟源,并初始化相应的寄存器。

3、定时器初始化:设定中断周期,选择定时器的计数模式,启动定时器,并设置中断优先级。

电子秒表1.设计课题任务及指标1.通过本设计的选题、方案论证、设计计算、安装调试、资料整理、撰写“设计报告”等环节, 初步掌握电子工程设计方法和组织实施的基本技能, 深化、扩展并综合运用课堂上所学的电子电路分析设计方法以及集成电路知识完成小系统的电路设计。

2.利用基本脉冲发生器及计数、译码、显示等单元电路设计数字秒表。

3.在实验装置上或者利用仿真软件完成数字秒表的线路连接和调试。

功能要求:基本要求: 计时从1s至99s;有置数、复位功能;能用开关灵活启动和停止秒表。

扩展功能: 有倒计时功能;能计时从0.1s至9.9s。

2.系统设计方案论证所作为数字式秒表, 所以必须有数字显示。

按设计要求, 须用数码管来做显示器。

题目要求最大记数值为99秒, 那则需要两个数码管。

要求计数分辨率为1秒, 那么则需要相应频率的信号发生器。

选择信号发生器时, 有两种方案:一种是用晶体震荡器, 另一种方案是采用集成电路555定时器与电阻和电容组成的多谐振荡器。

由于熟悉程度, 本组采用集成电路555定时器与电阻和电容组成的多谐振荡器。

秒表功能中要求有复位功能、能用开关灵活启动和停止秒表, 则控制电路的方案也有两种:方案一, 用74ls08和74ls32及一个3控拨码开关;方案二, 用2个单刀双掷开关及多个单刀开关。

为了能够灵活的控制秒表, 我们选用方案一。

计数部分使用两个74LS192十进制计数器, 这种计数器能够简捷的进行顺逆计时, 为了方便简单译码显示电路采用了74ls48与共阴极七段数码管。

系统框图:图1 流程图4.单元电路设计4.1电源与总控开关图2 电源与总控开关电源由干电池提供;R1为保护电阻;S1为电路总控开关。

4.2脉冲发生器(由555构成的多些振荡器)图3 脉冲发生电路图图4 NE555管脚图由于频率f=1.43/(R1+2R2)C=1Hz, (1)产生1Hz频率,所以, 电容C1=0.33u, 电阻R2=100KΩ, R3=2.2MΩ。

电子秒表设计数字逻辑课程设计

第一章实验概述

a)实验设计任务

1.1.1 设计任务

1. 设计一个电子秒表,可显示4位数,计时范围0——10分钟

2. 显示精确到0.1秒,对0.01秒进行四舍五入

3. 有暂停、启动、恢复和连续功能,显示板由发光二极管构成2.1 实验目的与设计要求

2.1.1 实验目的

1. 学习数字电路基本RS触发器、单稳态触发器、时钟发生器、计数

器以及译码显示器等单元电路的综合应用;

2. 了解电子秒表的组成与工作原理;

3. 熟悉中规模集成电路的应用;

4. 掌握电子秒表的设计、调试以及故障排除方法;

5. 培养书写综合实验报告的能力。

2.1.2 设计要求

1. 根据设计任务要求,综合运用数字电子技术课程中所学到的理论

知识与实践技能独立完成设计课题。

2. 根据课题查阅书籍,独立思考,深入研究课程设计中遇到的问

题,培养自己分析、解决问题的能力。

3. 根据设计要求,从选择设计方案开始,首先按单元电路进行

设计,选择合适的元器件,最后画出总的电路图。

4. 学会电子电路的连线安装和调试技能,最终实现任务要求的全部功能;电路布局合理,走线清楚,工作可靠。

5. 写出完整的实验报告,调试中出现的异常现象的分析与讨论。

第二章电子秒表的设计过程

2.1 电路的设计与元件的选择

2.1.1 总体方案的设计

图 2.1

电子秒表一般由振荡器、分频器、计数器、译码器、显示器等几部分组成。

其中振荡器和分频器组成标准秒信号发生器,由不同进制的计数器、译码器和显示器组成计时系统。

信号送入计数器,累计结果以分、秒、分秒的数字显示出来,分、分秒由十进制计数器构成,秒由六十进制计数器构成。

其原理框图(如图2.1)

2.1.2 所需元件的选择

1. 二输入与门、二输入与非门、二输入或门、反相器

2. 多谐振荡器:f=100Hz(集成555定时器的应用)(如图 2.2)

振荡周期T=0.7(R1+2R2)C,调节滑动变阻R2可输出不同的频率的脉冲信号;此振荡器在电路中是为分频器和四舍五入电路提供脉冲信号。

图2.2

3. 8421编码十进制加法计数器74160 (如图2.3)

图2.3

四个十进制加法计数器74160构成电子秒表的计数单元,分别显示分个位、秒十位、秒个位与0.1秒;经过不同的连接方式,74160能够实现四种不同的逻辑功能如下:

1)清零。

CLR’端为清零端,只要CLR’=0,触发器。