32位单精度浮点乘法器的FPGA实现

- 格式:doc

- 大小:126.50 KB

- 文档页数:4

文献检索课程作业3 撰写文献综述

(本作业通不过者取消考试资格!)

【实验内容与设计思想】

以下是每个同学必须完成的文献综述题目,必须按张老师要求在本课程进行的第四周星期一之前,将完成稿通过你的博客发布到因特网上,并同时发一封邮件到张老师邮箱,报告你的博客网址和文献综述完成情况。

张老师会立刻回电批示通过或不予通过。

凡不予通过者请立即自行修改,如第二稿仍不能通过,则取消该生本课程期末考试资格,本课程成绩以零分记。

质量上乘的文献综述将在张老师的网站上分批展示,并在该生的期末考试成绩上适当加分,予以表彰。

信管041班文献综述题目

计科051班文献综述题目

计科052班文献综述题目

电科052班文献综述题目

信管052班文献综述题目。

vivado ip核之复数浮点数乘法floating-point

在数字信号处理和科学计算中,复数浮点数乘法是一个非常重要的运算。

Vivado IP核提供了这个功能,使得用户可以在FPGA上实现高效的复数浮点数乘法。

复数浮点数乘法的原理比较简单,主要是将两个复数相乘,得到的结果也是复数。

这个过程需要分别对实部和虚部进行乘法运算,然后将结果合并。

在Vivado IP核中,这个过程被高效地实现了。

使用Vivado IP核进行复数浮点数乘法时,用户需要提供一些参数,例如输入复数的实部和虚部,以及输出结果的精度等。

这些参数对于实现高效的乘法运算非常重要。

此外,Vivado IP核还提供了许多其他有用的特性,例如可配置的流水线深度和多路复用器等。

这些特性可以帮助用户在FPGA上实现更加高效和灵活的复数浮点数乘法运算。

总之,Vivado IP核中的复数浮点数乘法是一个非常有用的功能,可以帮助用户在FPGA上实现高效和灵活的复数浮点数乘法运算。

通过合理地使用这个功能,用户可以大大提高数字信号处理和科学计算的性能。

1。

20×18位符号定点乘法器的FPGA实现王景存;黄勇【摘要】在数字信号处理中经常需要进行乘法运算,乘法器的设计对整个器件的性能有很大的影响,在此介绍20×18比特定点阵列乘法器的设计.采用基4-Booth算法和4-2压缩的方案,并采用先进的集成电路工艺,使用SMIC 0.18μm标准单元库,提高了乘法器的速度,节省了器件.利用Xilinx FPGA(xc2vp70-6ff1517)对乘法器进行了综合仿真,完成一次乘法运算的时间为15.922 ns,在减少乘法器器件的同时,提高了乘法器的速度,降低了器件的功耗.【期刊名称】《现代电子技术》【年(卷),期】2009(032)008【总页数】4页(P5-7,10)【关键词】定点乘法器;VerilogHDL;Booth算法;4-2压缩;波形仿真【作者】王景存;黄勇【作者单位】武汉科技大学,湖北,武汉,430081;武汉科技大学,湖北,武汉,430081【正文语种】中文【中图分类】TP332.2随着计算机和信息技术的快速发展,人们对器件处理速度和性能的要求越来越高,在高速数字信号处理器(DSP)、微处理器和RSIC等各类芯片中,乘法器是必不可少的算术逻辑单元,且往往处于关键延时路径中,乘法运算需要在一个时钟周期内完成,它完成一次乘法操作的周期基本上决定了微处理器的主频,因此高性能的乘法器是现代微处理器及高速数字信号处理中的重要部件[1]。

目前国内乘法器设计思想有4种,分别为:并行乘法器、移位相加乘法器、查找表乘法器、加法树乘法器。

其中,并行乘法器易于实现,运算速度快,但耗用资源多,尤其是当乘法运算位数较宽时,耗用资源会很庞大;移位相加乘法器设计思路是通过逐项移位相加实现,其耗用器件少,但耗时钟,速度慢;查找表乘法器将乘积直接放在存储器中,将操作数作为地址访问存储器,得到的输出数据就是乘法结果,该方法的速度只局限于存储器的存储速度,但随乘数的位数增加,存储器的空间会急剧增加,该方法不适合位数高的乘法操作;加法树乘法器采用流水线结构,能在一个时钟完成两数相乘,但当乘数的位数增加,流水线的级数增多,导致会使用很多寄存器,增加器件的耗用[2],而采用Booth算法的乘法器,会在速度、器件、精度、功耗方面有很大优势。

基于FPGA的流水线单精度浮点数乘法器设计彭章国;张征宇;王学渊;赖瀚轩;茆骥【摘要】针对现有的采用Booth算法与华莱士(Wallace)树结构设计的浮点乘法器运算速度慢、布局布线复杂等问题,设计了基于FPGA的流水线精度浮点数乘法器.该乘法器采用规则的Vedic算法结构,解决了布局布线复杂的问题;使用超前进位加法器(Carry Look-ahead Adder,CLA)将部分积并行相加,以减少路径延迟;并通过优化的4级流水线结构处理,在Xilinx(R)ISE 14.7软件开发平台上通过了编译、综合及仿真验证.结果证明,在相同的硬件条件下,本文所设计的浮点乘法器与基4-Booth算法浮点乘法器消耗时钟数的比值约为两者消耗硬件资源比值的1.56倍.【期刊名称】《微型机与应用》【年(卷),期】2017(036)004【总页数】5页(P74-77,83)【关键词】浮点乘法器;超前进位加法器;华莱士树;流水线结构;Vedic算法;Booth 算法【作者】彭章国;张征宇;王学渊;赖瀚轩;茆骥【作者单位】西南科技大学信息工程学院,四川绵阳621010;西南科技大学信息工程学院,四川绵阳621010;中国空气动力研究与发展中心,四川绵阳621000;西南科技大学信息工程学院,四川绵阳621010;西南科技大学信息工程学院,四川绵阳621010;西南科技大学信息工程学院,四川绵阳621010【正文语种】中文【中图分类】TP331.2浮点乘法器(eFloating Point Multiplier,FPM)是数字信号处理(eDigital Signal Processing,DSP)、视频图像处理以及信号识别等应用邻域重要的运算单元。

尤其是在视频图像处理领域,随着对高速海量图像数据处理的实时性要求逐渐提高,设计一种具有更高速率、低功耗、布局规律、占用面积小和集成度高的浮点乘法器极其重要。

阵列乘法器是采用移位与求和的算法而设计的一种乘法器[1]。

fpga课程设计乘法器一、课程目标知识目标:1. 让学生掌握FPGA的基本原理和结构,理解乘法器的设计方法。

2. 使学生了解数字信号处理中乘法运算的重要性,掌握乘法器的功能和应用。

3. 帮助学生掌握Verilog HDL语言编程,并能运用该语言设计简单的乘法器电路。

技能目标:1. 培养学生运用FPGA进行数字电路设计的能力,提高实际问题解决能力。

2. 培养学生运用Verilog HDL语言进行编程,实现特定功能的乘法器电路。

3. 培养学生进行团队协作,完成课程设计任务,提高沟通与协作能力。

情感态度价值观目标:1. 培养学生对FPGA技术及其应用的兴趣,激发学生的创新意识。

2. 培养学生严谨、务实的科学态度,养成勤奋、刻苦的学习习惯。

3. 增强学生的国家使命感和社会责任感,认识到我国在FPGA领域的发展潜力。

课程性质:本课程为电子工程与技术专业课程,以实践为主,理论联系实际。

学生特点:学生具备一定的电子电路基础和编程能力,对FPGA技术有一定了解。

教学要求:结合课程特点和学生特点,注重实践操作,提高学生的动手能力和创新能力。

在教学过程中,注重引导学生自主学习,培养团队协作精神。

通过课程学习,使学生能够独立完成乘法器的设计与实现,为后续相关课程打下坚实基础。

二、教学内容1. FPGA基本原理和结构复习:回顾FPGA的内部结构、工作原理以及配置技术,重点理解查找表(LUT)的原理和应用。

相关教材章节:第一章 FPGA概述。

2. 数字乘法器原理:介绍乘法器在数字信号处理中的应用,分析不同类型的乘法器设计方法,如并行乘法器、串行乘法器等。

相关教材章节:第三章 数字乘法器设计。

3. Verilog HDL语言编程基础:复习Verilog HDL的基本语法,重点掌握模块定义、数据类型、运算符和赋值语句等。

相关教材章节:第二章 Verilog HDL基础。

4. 乘法器设计实践:结合实际案例,引导学生利用Verilog HDL语言设计一个简单的乘法器电路,包括设计、仿真和综合。

基于改进型选择进位加法器的32位浮点乘法器设计作者:刘容赵洪深李晓今来源:《现代电子技术》2013年第16期摘要:在修正型Booth算法和Wallace树结构以及选择进位加法器的基础上,提出了一种新型32位单精度浮点乘法器结构。

该新型结构通过截断选择进位加法器进位链,缩短了关键路径延时。

传统选择进位加法器每一级加法器的进位选择来自上级的进位输出。

提出的结构可以提前计算出尾数第16位的结果,它与Wallace树输出的相关位比较就可得出来自前一位的进位情况进而快速得到进位选择。

在Altera的EP2C70F896C6器件上,基于该结构实现了一个支持IEEE754 浮点标准的4级流水线浮点乘法器,时序仿真表明,该方法将传统浮点乘法器结构关键路径延时由6.4 ns减小到5.9 ns。

关键词:修正Booth算法; Wallace树结构;选择进位加法器;浮点乘法器中图分类号: TN702⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)16⁃0133⁃04浮点乘法器是数字处理器的重要组成单元,它的性能直接关系到整个数字系统的性能。

所以浮点乘法器一直以来是人们研究的热点。

而乘法器的设计主要是对速度、面积、功耗等因素的优化与折中。

Booth 算法大大缩小了部分积数量;Wallace tree、dadda tree等压缩树结构实现部分积的并行求和提高了乘法器的速度,进位保留加法器(Carry Save Adder,CSA)则实现最终两个部分积的快速求和。

文献[1]基于乘法器各级核心器件是加法器的思想,通过优化加法器减小了乘法器的延时。

文献[2]设计了一种改进的基4 Booth编码和华莱士树的24位符号定点乘法器,在功耗和面积降低的同时,延时也得到了减小,做到了芯片性能和设计复杂度之间的良好折中。

文献[3]提出了一种适用于FPGA结构的改进型Wallace tree架构乘法器,实现了资源和性能的合理平衡。

fpga里小数乘法怎么搞?转载▼/s/blog_be7040250101kcgn.html经常有人问, fpga里小数乘法怎么搞?如果你乐意, 按照IEEE754标准做"浮点"型运算的ip当然最好(虽然面积上不太好).不过,很多情况下,没有这个必要.一般我们就用"定点"了.你得自己"定个点", 比如用16位, 分成8位整数8位小数(后面记为"(8.8)"), 即"定点"在第8位.那么:1 -> 16'h0100;1.5 -> 16'h0180;-1.5 -> -1.5*256 + 65536(补码) -> 16'hFE80(其实就是-16'sh0180, 让综合器给我们算补码去~~);...1.164 -> 1.164*256 = 298 = 16'h012A;所以signed input [15:0] a (也是"8整.8小")和 1.164相乘给signed output [15:0] mul (也是"8整.8小"), 直接写:assignmul = (a * 16'sh012A) >>>8;就行了, 当然, 你的fpga里有dsp block最好, 不然也要几百个LE的.因为(8.8) 乘 (8.8) 得到 (16.16), 为了恢复成(8.8), 所以帯符号右移8位即可.把低8位小数舍掉, 高8位整数也丢了, 所以你得保证你的16位(8.8)的"定点小数"乘积不能超过范围, 多数数字信号处理系数都是区间[-1.0, 1.0]的,多半不存在问题, 积分什么的, 还有其它可能有问题的自己想清楚就行, 当然你要保留16位整.16位小也可以~~~总结:modulefixpmul#(parameter IW = 8,parameter FW = 8)(input signed [IW+FW-1 : 0] a,input signed [IW+FW-1 : 0] b,output signed [IW+FW-1 : 0] o);(* multstyle = "dsp" *) wire signed [IW*2+FW*2-1 : 0] long;assign long = a * b;assign o = long >>> FW;endmodulePS: 作为一个完美主义者的想法: 以8位整型为例, 其实8位有符号乘8位有符号得到的16位有符号, 中的第14位(权2^14的位, 符号位右边的位), 很讨厌, 它只有在-128 * -128时才等于1, 其它65535种情况, 全是0, 很浪费.所以我们一般在数字信号处理系统中, 永远把[-1,1]映射到[-127,127], 这样那个讨厌的第14位永远用不到, 然后就可以: wire signed [15:0] mul = a * b; wire signed [14:0] out = {wire[15], wire[13:0]}, 8位有符号乘8位有符号得到15位有符号, 节约一位.。

基于FPGA的32位循环型除法器设计作者:李文彬陈金鹰王惟洁任小强来源:《物联网技术》2014年第11期摘要:借助于硬件描述语言Verilog HDL语言和FPGA,提出了一种32位循环型除法器的实现方法。

该除法器通过改善程序结构,优化了时序,提高了除法运算速度,克服了传统除法器“吃时钟”的弊端。

且该除法器的移位、相减和比较操作都在一个程序下完成,无需模块划分,节约逻辑资源。

该设计并顺利通过Quartus II编译、综合和仿真工具Modelsim的仿真,达到了预期的结果。

关键词:Verilog HDL;FPGA;循环;除法器中图分类号:TP393 文献标志码:A 文章编号:2095-1302(2014)11-00-020 引言在数据处理过程中,除法是经常用但也是最复杂的四则运算。

特别是针对含有除法器的FPGA设计中,除法器的运算速度,运算精度和占用逻辑资源大小对系统的整体性能具有很大影响[1]。

现有的EDA软件提供的除法模块时钟消耗多,占有逻辑资源量大,且除数受限,只能是2的次幂。

因此,设计一种由Verilog HDL[2]编写的可综合的,可以是任意除数的,运算速度快,逻辑资源占用量小[3,4]的除法器在FPGA数据处理中就显得尤为必要。

1 循环型除法器原理与设计循环性除法器也叫位操作除法器,主要通过移位、相减和比较三种操作实现求商和得余[5]。

无论是乘法器还是除法器都有操作空间,典型的循环型除法器又可分为操作空间可恢复性和不可恢复性,这里采用易于控制,逻辑清晰的操作空间不可恢复型算法。

在上述所采用算法中,首先保证被除数为正值,若为负值,则对被除数正值化,然后进行相应的移位、减法和比较操作,最后再对结果进行调整。

具体实现过程如下:假设除数和被除数都是N位,那么操作空间P的位宽就是2*N,其中P[N-1:0]用来填充被除数,P[2*N-1:N-1]是用来与除数进行递减操作。

此外,为了保证运算结果正确性,还要考虑同步操作,P[2*N-1:N-1]和除数的递减操作应该发生在别的空间,此处命名为D空间,D空间具有和P 空间同样的位宽。

FPGA浮点数定点数的处理/justlxy/p/5100053166⼤佬博客,讲的⾮常有条理的1,基础知识(1)定点数的基础认知:⾸先例如⼀个16位的数表⽰的定点数的范围是:(MAX:16‘d32767 MIN: -32767#2^15-1#’)最⾼位符号位,三位整数位,其余的12位是⼩数位的话,那么它的精度有⼩数部分决定:1/4096=0.024*******可表⽰数的范围为:(0.024********4095)=0.999755859375,然后加上整数的最⼤表⽰值7,即极限最⼤值为7.999755859375。

(2)浮点数的认知浮点数就是指整数和⼩数位数不确定的数字的表达,实际上采⽤的就是咱们常⽤的科学计数法。

如1.23*10^2采⽤的是基数(10),指数(2),尾数(1.23)以及⼀个符号位来表⽰。

这⾥实际上是采⽤指数⽅法实现了⼩数点的浮动。

在 IEEE 标准中,浮点数是将特定长度的连续字节的所有⼆进制位分割为特定宽度的符号域,指数域和尾数域三个域,其中保存的值分别⽤于表⽰给定⼆进制浮点数中的符号,指数和尾数。

这样,通过尾数和可以调节的指数(所以称为"浮点")就可以表达给定的数值了。

具体的格式参见下⾯的图例:上图中可以看出S表⽰符号位,EXponent表⽰指数位,也就是“浮动”的指数位,指数的范围在32位的系统中(0-2^8 -1)/2 也就是0-127,在double型位2^11位浮动指数。

2.FPGA浮点数的定点化⾸先明确输⼊的浮点数是什么格式的:其次明⽩要输出的定点数⼜是怎样的,最后两者之间的转换也就明了了:输⼊的浮点数是::f[31:0]表⽰⼀个单精度32位浮点数,f[31]是符号位,其为‘0’表⽰正数、为‘1’表⽰负数;f[30:23]这8位为指数位,为了能表⽰负指数,将在实际指数的基础上加上127得到的结果存⼊f[30:23];f[22:0]表⽰⼩数位(尾数),类似科学计数法,不过采⽤了省略整数位(2进制的科学计数法整数位必定是1)1。

32位单精度浮点乘法器的FPGA实现

作者:胡侨娟仲顺安陈越洋党华 | 来源:现代电子技术 | 日期:

2007-11-28 | 被阅读:7 次【小中大】

摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综...

摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综合。

关键词: 浮点乘法器; Boo th 算法; W allace 树; 波形仿真

随着计算机和信息技术的快速发展, 人们对微处理器的性能要求越来越高。

乘法器完成一次乘法操作的周期基本上决定了微处理器的主频, 因此高性能的乘法器是现代微处理器中的重要部件。

本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

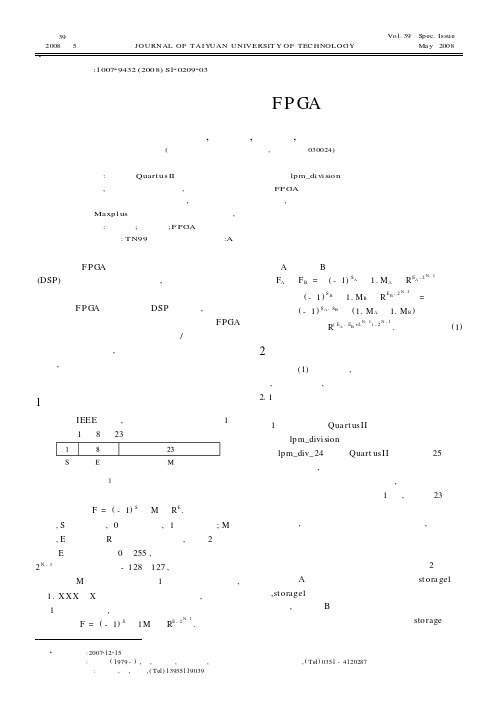

1 乘法计算公式

32 位乘法器的逻辑设计可分为: Booth编码与部分积的产生, 保留进位加法器的逻辑, 乘法阵列的结构。

1.1 Booth编码与部分积的逻辑设计

尾数的乘法部分,本文采用的是基4 Booth编码方式, 如表1。

首先规定A

m 和B

m

表示数据A和B的实际尾数,P 表示尾数的乘积, PP

n

表示尾数的部分积。

浮点

32 位数, 尾数是带隐含位1 的规格化数, 即: A

m =1×a

22

a

21…

.a

和B

m

= 1

×b

22b

21

.…b

, 由于尾数全由原码表示,相当于无符号数相乘, 24 × 24 位尾数

乘积P 的公式为:

1.2 乘法器的阵列结构

本文采用的是3 -2 加法器, 输入3 个1 位数据: a, b,ci; 输出2 个1 位数据: s, Co。

运算式如下:

其逻辑表达式如下:

产生之后, 将他们相加便得到每个乘法操作的结果。

相加的步当每个部分积PP

n

骤有很多, 可采用的结构和加法器的种类也很多。

比如串行累加:

而Wallace 树的乘法阵列如下:

加法器之间的连接关系如图1, 图2 所示, 或者从公式(7) 与(8) 中可以看出, 图1中串行累加的方法延迟为11个3-2 加法器的延迟, 而图2中, Wallace树延迟为5个3 -2加法器的延迟。

图1的延迟比图2的延迟大。

图1 串行累

加图2 Wallace 树

2 32 位浮点乘法器的设计

本文是针对IEEE754 单精度浮点数据格式进行的浮点乘法器设计。

IEEE754 单精度浮点格为32位, 如图3 所示。

设A ,B均为单精度IEEE754格式, 他们的符号位, 有效数的偏移码和尾数部分分别用S , E 和M来表示。

双精度和单精度采用的运算规则是一致的, 只是双精度的位长增加了一倍, 双精度是64位, 其中尾数52位, 指数11位, 1位符号位。

所以提高了精度范围。

图3 32 位浮点数据格式

32 位浮点数据格式: A = (- 1) S×M ×2E-127。

其中乘法器运算操作分4步进行。

(1) 确定结果的符号, 对A 和B 的符号位做异或操作。

(2) 计算阶码, 两数相乘, 结果的阶码是两数的阶码相加, 由于A 和B 都是偏移码, 因此需要从中减去偏移码值127,得到A 和B 的实际阶码, 然后相加, 得到的是结果的阶码, 再把他加上127, 变成偏移码。

(3) 尾数相乘,A 和B 的实际尾数分别为24位数, 即1×M

a 和1×M

b

, 最高位1

是隐藏位, 浮点数据格式只显示后23位, 所以尾数相乘结果应为一个48位的数据。

(4) 尾数规格化, 需要把尾数相乘的48位结果数据变成24 位的数据, 分3步进行:

① 如果乘积的整数位为01, 则尾数已经是规格化了;如果乘积的整数位为10, 11, 则需要把尾数右移1位, 同时把结果阶码加1。

② 对尾数进行舍入操作, 使尾数为24位, 包括整数的隐藏位。

③ 把结果数据处理为32位符合IEEE浮点数标准的结果。

包括1位符号位, 8位结果阶码位, 结果23尾数位。

3 32 位浮点乘法器的实现与仿真

图4 列出本设计的FPGA 仿真结果。

图中data1是被乘数, data2是乘数, reset 是清零信号, 高有效。

start 是开始信号, 也是高有效。

dataout10是两个浮点32 位数相乘, 进行规格化以后的结果, 是一个32 位数。

Product 是24位尾数相乘的结果, 是一个48位数。

图4 32 位浮点乘法器的仿真结果

整个设计采用了VHDL和Verilog HDL语言进行结构描述, 如果采用的是上华0.5 的标准单元库, 并用Synopsys DC 进行逻辑综合, 其结果是完成一次32位浮点乘法的时间为30ns, 如果采用全定制进行后端版图布局布线, 乘法器性能将更加优越。

4 结语

本文给出了32 位浮点乘法器的设计, 浮点算法具有高精度性以及较宽的运算

范围, 使得乘法的设计更能够满足工程和科学计算的要求, 电路的设计、模拟和实现均采用Altera Quartus II 4.1开发工具。

采用的器件EPF10K100EQ 240-1, 逻辑单元是1914个, PIN的数量是147,本设计采用了一系列的算法和结构, 如采用Booth编码的方法和Wallace树的结构, 使得系统具有高速度特点, 并且易于ASIC的后端版图实现。