有限状态机FSM

- 格式:ppt

- 大小:1.02 MB

- 文档页数:62

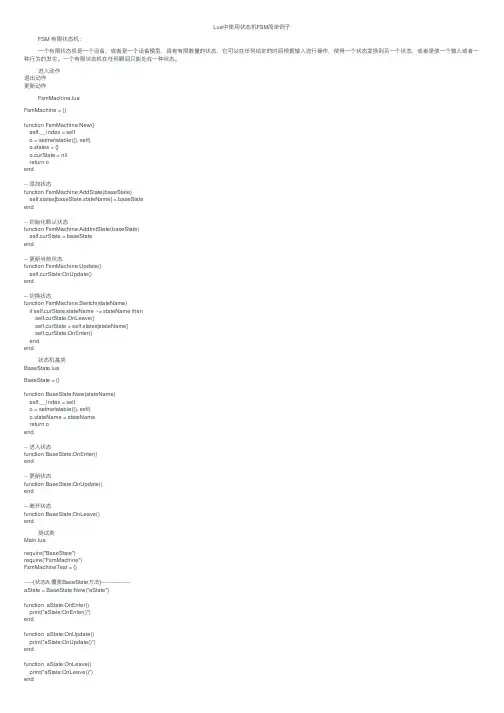

Lua中使⽤状态机FSM简单例⼦FSM 有限状态机:⼀个有限状态机是⼀个设备,或者是⼀个设备模型,具有有限数量的状态,它可以在任何给定的时间根据输⼊进⾏操作,使得⼀个状态变换到另⼀个状态,或者是使⼀个输⼊或者⼀种⾏为的发⽣。

⼀个有限状态机在任何瞬间只能处在⼀种状态。

进⼊动作退出动作更新动作FsmMachine.luaFsmMachine = {}function FsmMachine:New()self.__index = selfo = setmetatable({}, self)o.states = {}o.curState = nilreturn oend-- 添加状态function FsmMachine:AddState(baseState)self.states[baseState.stateName] = baseStateend-- 初始化默认状态function FsmMachine:AddInitState(baseState)self.curState = baseStateend-- 更新当前状态function FsmMachine:Update()self.curState:OnUpdate()end-- 切换状态function FsmMachine:Switch(stateName)if self.curState.stateName ~= stateName thenself.curState:OnLeave()self.curState = self.states[stateName]self.curState:OnEnter()endend状态机基类BaseState.luaBaseState = {}function BaseState:New(stateName)self.__index = selfo = setmetatable({}, self)o.stateName = stateNamereturn oend-- 进⼊状态function BaseState:OnEnter()end-- 更新状态function BaseState:OnUpdate()end-- 离开状态function BaseState:OnLeave()end测试类Main.luarequire("BaseState")require("FsmMachine")FsmMachineTest = {}-----[状态A,覆盖BaseState⽅法]----------------aState = BaseState:New("aState")function aState:OnEnter()print("aState:OnEnter()")endfunction aState:OnUpdate()print("aState:OnUpdate()")endfunction aState:OnLeave()print("aState:OnLeave()")end-----[状态B,覆盖BaseState⽅法]----------------bState = BaseState:New("bState") function bState:OnEnter()print("bState:OnEnter()")endfunction bState:OnUpdate()print("bState:OnUpdate()")endfunction bState:OnLeave()print("bState:OnLeave()")end-----[测试状态机]-----------------------------fsm = FsmMachine:New()fsm:AddState(aState)fsm:AddState(bState)fsm:AddInitState(aState)for i = 1, 10 doif i == 5 thenfsm:Switch("bState")endfsm.curState:OnUpdate()end输出aState:OnUpdate()aState:OnUpdate()aState:OnUpdate()aState:OnUpdate()aState:OnUpdate()aState:OnLeave()bState:OnEnter()bState:OnUpdate()bState:OnUpdate()bState:OnUpdate()bState:OnUpdate()bState:OnUpdate()。

编译原理有限状态机及化简编译原理是计算机科学中的一门重要课程,它研究的是如何将高级语言程序转化为可执行的低级机器语言。

在编译原理中,有限状态机是一种重要的工具,它能够帮助我们理解和设计编程语言的词法结构。

而化简则是在设计有限状态机时的一项重要技巧,能够简化状态机的复杂度,提高编译器的效率。

有限状态机(Finite State Machine,FSM)是一种用于描述系统行为的数学模型。

在编译原理中,有限状态机被广泛应用于词法分析阶段,用于识别和解析程序中的各类词法单元。

有限状态机由一组状态和一组转移函数组成。

状态表示系统所处的某个特定状态,转移函数表示状态之间的转移条件和动作。

通过不断地进行状态转移,有限状态机可以识别和解析输入的程序。

在编译过程中,我们需要将源代码中的字符序列转化为一系列词法单元,如关键字、标识符、运算符等。

有限状态机可以帮助我们识别这些词法单元。

例如,我们可以设计一个有限状态机来识别整数常量。

该状态机的状态可以分为初始状态、扫描状态和接受状态。

初始状态表示状态机的起始状态,扫描状态表示状态机正在扫描数字字符,接受状态表示状态机已经扫描完整个整数常量。

通过定义合适的转移函数,我们可以使状态机按照预定的规则进行状态转移,最终得到正确的整数常量词法单元。

在设计有限状态机时,我们常常需要考虑状态的合并和化简。

化简是指将状态机中的一些状态合并为一个等价的状态,从而减少状态的数量。

通过化简可以使状态机更加简洁,提高编译器的效率。

化简的过程中,我们需要考虑状态之间的等价性。

两个状态是等价的,当且仅当它们在任何输入条件下都具有相同的转移行为。

通过判断状态的等价性,我们可以将等价的状态合并为一个新的状态,从而化简状态机。

化简状态机的过程可以使用等价类划分算法来实现。

该算法首先将状态划分为两个互不相交的等价类:接受状态和非接受状态。

然后,对每个等价类进行划分,直到无法再进行划分为止。

最终,我们可以得到一个化简后的状态机,其状态数量更少,但仍能正确识别和解析程序中的词法单元。

有限状态机(FSM)设计利用VHDL设计的许多实用逻辑系统中,有许多是可以利用有限状态机的设计方案来描述和实现的。

无论与基于VHDL的其它设计方案相比,还是与可完成相似功能的CPU相比,状态机都有其难以逾越的优越性。

它主要表现在以下几方面:由于状态机的结构模式相对简单,设计方案相对固定,特别是可以定义符号化枚举类型的状态,这一切都为VHDL综合器尽可能发挥其强大的优化功能提供了有利条件。

而且性能良好的综合器都具备许多可控或不可控的专门用于优化状态机的功能。

状态机容易构成性能良好的同步时序逻辑模块,这对于对付大规模逻辑电路设计中令人深感棘手的竞争冒险现象无疑是一个上佳的选择,加之综合器对状态机的特有的优化能,使得状态机解决方案的优越性更为突出。

状态机的VHDL设计程序层次分明,结构清晰,易读易懂,在排错、修改和模块移植方面,初学者特别容易掌握。

在高速运算和控制方面,状态机更有其巨大的优势。

由于在VHDL中,一个状态机可以由多个进程构成,一个结构体中可以包含多个状态机,而一个单独的状态机(或多个并行运行的状态机)以顺序方式的所能完成的运算和控制方面的工作与一个CPU类似。

由此不难理解,一个设计实体的功能便类似于一个含有并行运行的多CPU的高性能微处理器的功能。

事实上这种多CPU的微处理器早已在通信、工控和军事等领域有了十分广泛的应用。

就运行速度而言,尽管CPU和状态机都是按照时钟节拍以顺序时序方式工作的,但CPU 是按照指令周期以逐条执行指令的方式运行的;每执行一条指令通常只能完成一项操作,而一个指令周期须由多个CPU机器周期构成,一个机器周期又由多个时钟周期构成,一个含有运算和控制的完整设计程序往往需要成百上千条指令。

相比之下,状态机状态变换周期只有一个时钟周期,而且由于在每一状态中状态机可以完成许多并行的运算和控制操作,所以一个完整的控制程序,即使由多个并行的状态机构成,其状态数也是十分有限的。

有限状态机在单片机编程中的应用

有限状态机在单片机编程中的应用:

一、什么是有限状态机

有限状态机(Finite State Machine,FSM),也叫确定有限状态自动机,是一

种常用的数学计算模型,用来描述系统状态以及状态间转移的触发条件变化和行为转移,经常被用来模拟、确定和设计计算机程序和其它由许多步骤构成的工作流程。

二、单片机与有限状态机的应用

1、有限状态机可以有效的帮助开发者实现复杂的自动化控制系统。

通过有限

状态机,可以定义不同的流程,分析控制逻辑,以及控制程序的全部运行规律。

2、当需要实现复杂功能,控制流程时,通常使用有限状态机。

由于单片机可

以很好的模拟有限状态机,并且具有很好的计算能力,处理各种控制逻辑,所以单片机是一种优秀的解决方案。

三、单片机编程中,有限状态机应用的优势

1、有限状态机具有可视化、高效性和可维护性,这些特性使得它在单片机编

程中非常有用,能够使开发人员方便地理解流程、管理控制逻辑,提高编程的开发效率和稳定性。

2、有限状态机可以把程序划分为一些外部可见的变量和控制代码,简化程序

的设计和调试,大大减少开发难度和工作量,同时也提高了程序运行的可靠性。

3、有限状态机能够很好的处理复杂的状态转移问题,如果将有限状态机运用

到单片机的开发中,可以使程序的处理有更清晰的划分,让代码更易维护,更方便调试。

四、总结

从上面的分析可以清楚的看出,使用有限状态机的开发方式,可以有效地提高程序的可读性,可靠性,可维护性等等,因此,在单片机编程中运用有限状态机无疑是一个很好的选择。

模糊状态机(FuSM)FSM (有限状态机):涉及到不同状态之间的转换,且系统一次只处于一个当前状态。

FuSM(模糊状态机):有限状态机的一个变种,建立在模糊逻辑的概念之上,一般定义为“被扩展来处理部分真相概念的传统逻辑(bool 逻辑)的超集”。

应该注意,虽然FuSM建立在模糊逻辑概念之上,但不代表是实实在在的模糊系统。

部分真值是一个非常强大的概念。

与常规的FSM不同,FuSM在范围上不具有一般性。

与FSM一样,FuSM跟踪一系列可能的游戏状态。

但不同的是,FSM具有一个单一的当前状态,然后通过转换到一个不同的状态来响应输入事件,而FuSM 可能同时具有多个状态,因此不存在转换。

模糊系统中的每个状态都计算一个"激活水平",该激活水平决定了系统处于任意给定状态的程度,因此,系统的整体行为由当前被激活状态的贡献组合来决定。

FuSM仅仅对那些能够同时处于多个状态并且具有超越简单数字值(如开或关,关闭或打开,生存或死亡)的系统有用,模糊数值用于描述部分开,几乎关闭和未完全死亡等。

另一种对此类数值类型进行量化的方法是使用一个归一系数(0.0 与 1.0之间的数)来表示条件对各个端状态的隶属度(例如:0.0表示完全关闭,1.0表示完全开启),尽管对于FuSM来说归一化并不是必须的。

这是不必记住集合隶属度的所有权限制的一种简单方式,同时也确保了集合隶属度值之间比较的简单性。

关于什么是真正的FuSM,在游戏AI领域还存在一些混淆的看法,因为在同一类别中存在好几个FSM 变种被当作是FuSM。

这些变种包括:1::具有转换优先级的FSM. 在该模型中,必须对每个可用状态的激活水平进行计算(该模型仍然是一个FSM,因此每个状态都有一系列可能的转换);然后那个具有最高激活水平的状态获胜,成为新的当前状态。

这是许多程序员使用模糊度概念来增加其决策状态机的方式,但该系统仍然是一个FSM,并且类似系统输出行的可预测性仅仅比常规FSM稍微小一点。

如何利用有限状态机实现多任务有限状态机(Finite State Machine,FSM)是一种数学模型,可以用于描述和分析系统的行为。

在计算机科学领域,有限状态机常用于描述和实现程序的控制流程。

利用有限状态机实现多任务是一种常见的设计方法,可以将程序的控制流程分解为多个有限状态机,并在不同的状态机之间进行切换,从而实现多个任务的并发执行。

以下是一种基本的利用有限状态机实现多任务的方法:1.确定任务数量和任务优先级:首先,需要确定系统中存在的任务数量和任务的优先级。

任务的数量和优先级决定了需要设计的状态机的数量和结构。

2.设计状态机的状态集合:为每个任务设计一个状态机,并确定状态机的状态集合。

状态集合应该包括任务的所有可能状态,例如等待状态、运行状态、完成状态等。

可以使用状态迁移图或状态转换表来描述状态机的结构。

3.确定状态转换条件:确定每个状态之间的转换条件。

转换条件可以是特定的事件触发,例如定时器中断、外部输入事件等。

转换条件也可以是条件判断,例如变量的取值或一些条件的成立与否。

4.实现状态转换逻辑:根据状态转换条件,设计并实现状态机的转换逻辑。

转换逻辑可以使用条件语句、循环语句等编程语言提供的控制结构实现。

在状态转换过程中,可能需要保存和更新任务相关的数据或状态信息。

5.实现任务调度器:设计并实现任务调度器,负责控制不同任务状态机之间的切换。

任务调度器可以使用循环结构实现,按照任务的优先级顺序轮询各个任务的状态机,并根据状态机的当前状态和转换条件决定是否进行状态切换。

6.可以加入优先级调度:根据任务的优先级,可以考虑实现优先级调度算法,确保高优先级任务能够优先执行。

例如,可以使用优先级队列或时间片轮转算法来实现优先级调度。

7.运行时环境:根据具体的系统平台和编程语言,提供相应的运行时环境。

例如,可以在操作系统中实现多线程或多进程来同时执行任务状态机。

通过以上方法,利用有限状态机可以实现多任务的并发执行。

有限状态机主讲人:姜小波本章目录有限状态机(FSM)概述•有限状态机(Finite State Machine,FSM)的定义一个时序逻辑单元●有限状态机个时序逻辑单元✓取一个输入和一个现态✓生成输出和一个新的状态它被称为有限状态机,因为它至少有有限数量个状态。

它由组合逻辑单元和触发器组成,以使其能保持状态信息态信息。

可用状态转移表来表示现态、输入、输出和下一个状态。

●有限状态机的表达方式可用状态转移表来表示现态、输入、输出和下个状态。

InputCurrenInput 0 Input 1 …. Input nt State State 0State Next State / Output …. Next State / Output …. …. …. 1….State n …. …. …. …. …. ….状态转移表●有限状态机的表达方式也可以用状态转移图来表示与状态转移表一样的信息。

Input / OutputState0State1Input / Output状态转移图•状态机的本质对具有逻辑顺序和时序规律事件的对具有“”和“”事件的一种描述方法。

•应用思路从状态变量入手,分析每个状态的输入,状态转移和输出,从而完成电路的功能。

转移输出从完成电路的功能首先明确电路的输出关系,这些输出相当于状态的输出,回溯规划每个状态和状态转移条件与状态输入。

•有限状态机的组成合逻辑组合逻辑组合逻辑又可分为次态逻辑和输出逻辑两个部分。

其中次态逻辑的功能是用来确定有限状态机的下个中:次态逻辑的功能是用来确定有限状态机的下一个状态;输出逻辑是用来确定有限状态机的输出。

寄存器逻辑寄存器逻辑的功能:用来存储有限状态机的内部状态。

•状态机的基本要素状态:也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

输出输出指在某个状态时特定发的事件 :输出指在某一个状态时特定发生的事件。

输入:指状态机中进入每个状态的条件,有的状态机没有输入条件,其中的状态转移较为简状态机没有输入条件其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态。

有限状态机(FSM)设计——Fizzim2使用帮助更新记录•2016.04.26•1) 修改outputs/signals 类型为dff-onstate, dff-ontransit, dff-onboth, comb-ontransit, hold-onstate, hold-ontransit 和hold-onboth 共7种;•2) 修正一些 bugs•2016.03.22•第一版简介Fizzim2是一个FSM (Finite State Machine) 工具,可以自动生成 Verilog HDL 代码。

这个工具源于Fizzim,一个非常好的设计。

给作者提了几点改进建议,没有被采纳!也许是理念不同,也许是语言不通(一个中国人和一个德国人之间使用英语交流)。

好在原设计是开源的(点赞),于是就自己动手操刀了。

Fizzim2对其做了下面增强和改进:•all java, NOT need perl•add HDL-View, what you see is what you get•focus on design entry, ignore some features e.g. 'statebit' which can be accomplished by synthesizer•more explicitly in use, change type from 'statebit, regdp, comb, flag' to 'onstate, ontransit, ontransit-dd, hold'•add 'signals' & 'page_mode' feature, support complicated FSM design model•modify priority feature, use 'UserAttrs' of transition aspriority•'reset_state' can be set by right-click on state•fix some bugs总的说来,Fizzim2增加了“所见即所得”的特性,和改进了几处设计输入方式,使用起来更加方便了。