有限状态机(moore mealy)

- 格式:doc

- 大小:29.50 KB

- 文档页数:4

mealy型时序逻辑电路与moore型时序逻辑电路的区别。

Mealy型时序逻辑电路与Moore型时序逻辑电路有如下区别:

1. 输出信号的不同:Mealy型时序逻辑电路的输出信号是组合逻辑

门的输出和状态机的当前状态的函数,而Moore型时序逻辑电路的输出信

号仅仅是状态机的当前状态的函数。

2. 状态转移的时刻不同:Mealy型时序逻辑电路在输入信号边沿到

来时,根据组合逻辑门的输出和当前状态进行状态转移;而Moore型时序

逻辑电路在输入信号边沿到来时根据当前状态进行状态转移。

3. 状态机模型的不同:Mealy型时序逻辑电路的状态机模型与输出

信号有关,而Moore型时序逻辑电路的状态机模型与输出信号无关。

4. 模块的适用范围:Mealy型时序逻辑电路适用于需要输出与状态

有关的电路,而Moore型时序逻辑电路适用于需要输出与状态无关的电路。

总之,Mealy型时序逻辑电路多了一个输出与状态机有关的组合逻辑,因此电路中的状态转移和输出信号的计算是同时进行的。

Moore型时序逻

辑电路则只有一个状态机,因此状态转移和输出信号的计算是分别进行的。

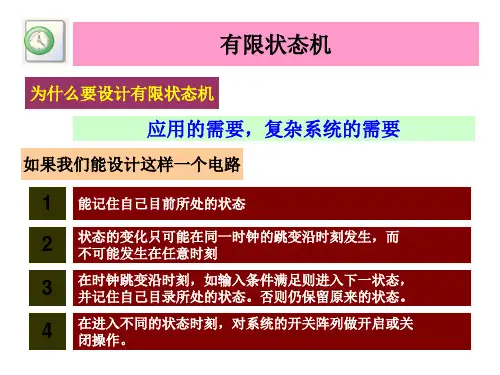

1.什么是有限状态机,Moore机和Mealy机的各自特点和他们之间的区别是什么?答:有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

Mealy机属于同步输出状态机,他的输出是当前状态和所有输入信号的的函数,其输出会在输出仅为当前状态的函数,与当前输入信号无关。

当然,当前状态是和上一时刻时输入信号相关的,当前输入的变化必须等待下一时钟到来使状态发生变化时才能导致输出的变化。

因此,Moore机比Mealy机多等待一个时钟周期才会引起输出的变化,由于Mealy机的输出不与时钟同步,当状态译码比较复杂时,易在输出端产生不可避免的毛刺。

********************************************************************* 2.一个复杂的电路可以划分为几个不同的抽象级别:系统级,算法级,寄存器传输级,逻辑门级,晶体管开关级。

********************************************************************* 3.reg和wire的区别Reg型变量需要被明确赋值,并且在重新赋值前,一直保持原值,wire对应于连续赋值,如assign,reg对应于过程赋值,如always,initial。

********************************************************************* 4.阻塞和非阻塞的区别非阻塞赋值在整个过程块结束后才能完成赋值操作,阻塞赋值在该语句结束时就立即完成赋值操作,阻塞语句是顺序执行的,而非阻塞语句是同时执行的。

********************************************************************* 5.举例说明触发器在什么情况下会在综合过程中生成锁存器在写组合逻辑电路的always块中,, always块中要使用的输入信号在always 后面的敏感信号表中有遗漏,组合逻辑电路设计时不能有反馈。

集成电路实验状态机设计实验报告专业:电子信息工程姓名:江燕婷学号:2011301200025状态机设计(实验五)实验报告一.实验目的1. 掌握状态机设计的基本方法2.学习利用状态机的方法实现控制电路二.实验原理有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。

有限状态机非常适合用FPGA器件实现,用Verilog HDL的case语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。

有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。

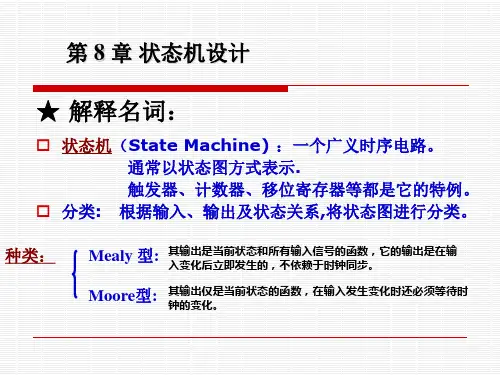

根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。

摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。

米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。

图1-1 摩尔型状态机图1-2 米里型状态机状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。

状态机的状态实现上,可采用符号编码或显式数字编码。

编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。

顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。

三. 实验设备与软件平台微型计算机,GW48-CK,QuartusII v5.0。

verilog 状态机写法在Verilog中,有几种常用的状态机写法,包括Mealy状态机、Moore状态机和通用状态机。

下面简要介绍每种写法的特点:Mealy状态机:输出依赖于当前状态和输入信号。

输出的变化可以与状态的变化同步。

Verilog代码示例:module MealyFSM (input logic clk,input logic reset,input logic input_signal,output logic output_signal);enum logic [2:0] states;logic [2:0] current_state, next_state;always_ff @(posedge clk or posedge reset) beginif (reset)current_state <= states[0];elsecurrent_state <= next_state;endalways_comb begincase (current_state)states[0]: begin // State 0if (input_signal)next_state = states[1];elsenext_state = states[0];output_signal = input_signal & next_state[0]; // Output depends on current state and input signalendstates[1]: begin // State 1if (input_signal)next_state = states[0];elsenext_state = states[1];output_signal = input_signal | next_state[0]; // Output depends on current state and input signalend// Add more states and conditions as neededendcaseendEndmoduleMoore状态机:输出只依赖于当前状态。

Moore状态机和Mealy状态机的区别

Mealy和moore型状态机的主要区别

Mooer状态机的输出只与当前的状态有关,也就是数当前的状态决定输出,⽽与此时的输⼊⽆关,输⼊只决定状态机的状态改变,不影响电路最终的输出(注意:这⾥所说的输出不是状态机的状态机状态的输出,⽽是当前状态的所代表的含义,⽐如:检测110 序列的状态机,当状态机跳转到STA_GOT110时,电路会有⼀个输出信号,假如说是find,此时find就会为⾼电平,其他(状态时)时find就会为低电平。

find 是我们最后电路的输出,find的值置于我们的转台机当前所处的状态有关,⽽与输出⽆关)。

⽤⼀本书上的话说就是:Moore状态机的每⼀状态指定它的输出独⽴于电路的输⼊。

Mealy状态机的输出不仅与当前的状态有关,还与当前的输出有关(同样,不要误认为状态机的输出只能是状态机的状态),即当前的输⼊和当前的状态共同决定当前的输⼊。

Mooer 状态机和 Mealy 状态机的状态的是相同的,当前的状态和输⼊共同决定下⼀个状态是什么。

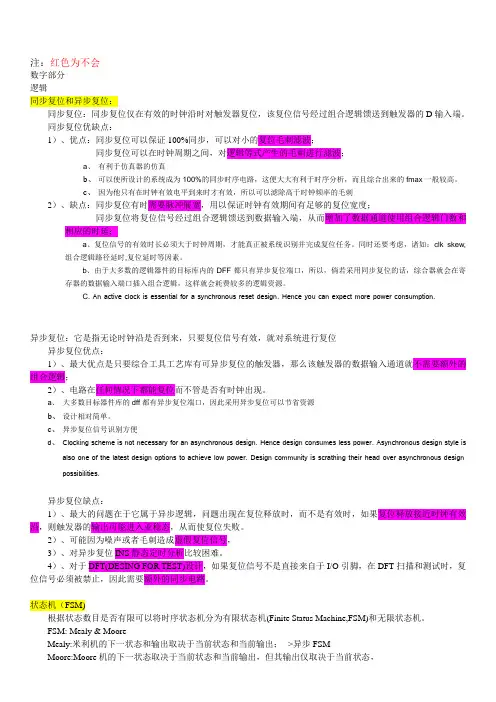

注:红色为不会数字部分逻辑同步复位和异步复位:同步复位:同步复位仅在有效的时钟沿时对触发器复位,该复位信号经过组合逻辑馈送到触发器的D输入端。

同步复位优缺点:1)、优点:同步复位可以保证100%同步,可以对小的复位毛刺滤波;同步复位可以在时钟周期之间,对逻辑等式产生的毛刺进行滤波;a、有利于仿真器的仿真b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺2)、缺点:同步复位有时需要脉冲展宽,用以保证时钟有效期间有足够的复位宽度;同步复位将复位信号经过组合逻辑馈送到数据输入端,从而增加了数据通道使用组合逻辑门数和相应的时延;a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。

同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

C. An active clock is essential for a synchronous reset design. Hence you can expect more power consumption.异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位异步复位优点:1)、最大优点是只要综合工具工艺库有可异步复位的触发器,那么该触发器的数据输入通道就不需要额外的组合逻辑;2)、电路在任何情况下都能复位而不管是否有时钟出现。

a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源b、设计相对简单。

c、异步复位信号识别方便d、Clocking scheme is not necessary for an asynchronous design. Hence design consumes less power. Asynchronous design style isalso one of the latest design options to achieve low power. Design community is scrathing their head over asynchronous design possibilities.异步复位缺点:1)、最大的问题在于它属于异步逻辑,问题出现在复位释放时,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态,从而使复位失败。

FPGA名词概念1、ASIC:application-specific integrated circuits专用集成电路是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC分为全定制和半定制。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

2、ALU:arithmetic an logic unit算术逻辑单元是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由“And Gate”(与门)和“Or Gate”(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。

基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。

3、BCD:binary-coded decimal BCD码或二-十进制代码,亦称二进码十进数是一种二进制的数字编码形式,用二进制编码的十进制代码。

这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。

4、CLBs:configurable logic blocks可配置逻辑模块。

包含一个可配置开关矩阵,此矩阵有选型电路(多路复用器),触发器和4或6个输入组成。

在Xilinx公司的FPGA器件中,CLB由多个(一般为4个或2个)相同的slice和附加逻辑构成。

Moore型状态机和Mealy型状态机 ⼀、状态机的定义 状态机就是能够根据控制信号按照预先设定的状态进⾏状态转移,是协调相关信号动作、完成特定动作的控制中⼼。

状态机简写为FSM (Finite State Machine),分为两类: 1:输出只和当前状态有关⽽与输⼊⽆关,则称为摩尔(Moore)状态机; 2:输出不仅和当前状态有关⽽且和输⼊有关,则称为⽶利(Mealy)状态机; ⼆、两种状态机的区别 1:在波形上区别:以⼀个序列检测器为例,检测到输⼊信号11时输出z为1,其他时候为0。

⽤摩尔型FSM实现需要⽤到三个状态(A,B,C)。

⽽⽤⽶利型FSM实现则需要两个状态(A,B)。

摩尔型FSM输出函数的输⼊只由状态变量决定,要想输出z=1,必须C状态形成,即寄存器中的两个1都打进去后才可以。

输出z=1会在下⼀个有效沿到来的时候被赋值。

⽽⽶利型FSM输出函数是由输⼊和状态变量共同决定的。

状态在B的时候如果输⼊为1,则直接以组合电路输出z=1,不需要等到下个有效沿到来。

从⽽也就不需要第三个状态C。

2:摩尔状态机更安全:输出在时钟边沿变化(总是在⼀个周期后)。

在Mealy机器中,输⼊更改可能会在逻辑完成后⽴即导致输出更改, 当两台机器互连时出现⼤问题,如果不⼩⼼,可能会发⽣异步反馈。

3:Mealy状态机对输⼊的反应更快:在相同的周期内反应 - 不需要等待时钟。

在Moore机器中,可能需要更多逻辑来将状态解码为输出 - 在时钟边沿之后更多的门延迟。

并⾮所有时序电路都可以使⽤Mealy模型实现。

⼀些时序电路只能作为摩尔机器实现。

三、经典三段式状态机模板1reg [:] current_state ;2reg [:] next_state ;34wire [:0] IDLE ;5wire [:0] S0 ;6wire [:0] S1 ;7wire [:0] S2 ;89//=============================================================================\10//**************************** State Machine *******************************11//=============================================================================\1213always @(posedge sclk or negedge s_rst_n) begin14if(!s_rst_n)15 current_state <= IDLE;16else17 current_state <= next_state;18end1920always @(*) begin21 next_state = IDLE;22case(current_state)23 IDLE:begin24if(idle2s0 == 1'b1)25 next_state = S0;26else27 next_state = current_state;28end2930 S0:begin31if(s02s1 == 1'b1)32 next_state = S1;33else34 next_state =current_state;35end3637 S1:begin38if(s12s2 == 1'b1)39 next_state = S2;40else41 next_state = current_state;42end4344 S2:begin45if(s22idle == 1'b1)46 next_state = IDLE;47else48 next_state = current_state;49end5051default:begin52 next_state = IDLE;53end54endcase55end5657assign idle2s0 = current_state == IDLE &&58assign s02s1 = current_state == S0 &&59assign s12s2 = current_state == S1 &&60assign s22idle = current_state == S2 &&6162always @(posedge sclk or negedge s_rst_n) begin63if(!s_rst_n) begin6465end66else begin67case(next_state)6869end70endView Code 四、摩尔型状态机 1、举例说明摩尔型状态机,⾮重叠检测 1101 1101 (1)状态转移图 (2)Moore代码1// ********************************************************************************* 2// Project Name : state_test3// Email :4// Create Time : 2020/06/25 20:205// Module Name : state_test6// editor : qing7// Version : Rev1.0.08// Description : ⾮重叠检测的Mooer状态机 11019// ********************************************************************************* 1011module state_test(12input sclk ,13input s_rst_n ,1415input din ,16output reg dout17 );1819//========================================================================\20// =========== Define Parameter and Internal signals ===========21//========================================================================/2223reg [4:0] current_state ;24reg [4:0] next_state ;2526parameter S0 = 5'b00001 ;27parameter S1 = 5'b00010 ;28parameter S2 = 5'b00100 ;29parameter S3 = 5'b01000 ;30parameter S4 = 5'b10000 ;3132//============================================================================= 33//**************************** Main Code *******************************34//============================================================================= 3536always @(posedge sclk or negedge s_rst_n) begin37if(!s_rst_n)38 current_state <= S0;39else40 current_state <= next_state;41end4243always @(*) begin44 next_state = S0;45case(current_state)46 S0:begin47if(din == 1'b1) // 148 next_state = S1;49else50 next_state = current_state; // 051end5253 S1:begin54if(din == 1'b1)55 next_state = S2; // 1156else57 next_state = S0; // 1058end5960 S2:begin61if(din == 1'b0) // 11062 next_state = S3;63else64 next_state = current_state; // 11165end6667 S3:begin68if(din == 1'b1)69 next_state = S4; // 110170else71 next_state = S0; // 110072end7374 S4:begin75if(din == 1'b1) // 1101 176 next_state = S1;77else78 next_state = S0; // 1101 079end8081default:begin82 next_state = S0;83end84endcase85end8687always @(posedge sclk or negedge s_rst_n) begin88if(!s_rst_n) begin89 dout <= 0;90end91else if(current_state == S4)92 dout <= 1;93else94 dout <= 0;95end96endmoduleView Code testbench1// ********************************************************************************* 2// Project Name : state_test3// Email :4// Create Time : 2020/06/25 06:255// Module Name : state_test_tb6// editor : qing7// Version : Rev1.0.08// ********************************************************************************* 910 `timescale 1ns/1ps11module state_test_tb;12reg sclk ;13reg s_rst_n ;14reg din ;15wire dout ;1617 state_test state_test_inst(18 .sclk (sclk ) ,19 .s_rst_n (s_rst_n ) ,20 .din (din ) ,21 .dout (dout )22 );2324initial25 sclk = 1'b0;26always #10 sclk = ~sclk;2728initial29begin30 #1;31 din = 0;32 s_rst_n = 1'b0;33 #21;34 s_rst_n = 1'b1;3536 #51;3738 din = 1;39 #20;40 din = 0;41 #20;42 din = 1;43 #20;44 din = 1;45 #20;46 din = 0;47 #20;48 din = 1;49 #20;50 din = 0;51 #30;5253 din = 1;54 #20;55 din = 0;56 #20;57 din = 1;58 #20;59 din = 1;60 #20;61 din = 0;62 #20;63 din = 1;64 #20;65 din = 0;66 #30;67end6869endmodule70View Code 2、举例说明摩尔型状态机,重叠检测 1101001 (1)状态转移图 (2)Moore代码1// ********************************************************************************* 2// Project Name : state_test3// Email :4// Create Time : 2020/06/25 20:205// Module Name : state_test6// editor : qing7// Version : Rev1.0.08// Description : 重叠检测的Mooer状态机 11019// ********************************************************************************* 1011module state_test(12input sclk ,13input s_rst_n ,1415input din ,16output reg dout17 );1819//========================================================================\20// =========== Define Parameter and Internal signals ===========21//========================================================================/2223reg [4:0] current_state ;24reg [4:0] next_state ;2526parameter S0 = 5'b00001 ;27parameter S1 = 5'b00010 ;28parameter S2 = 5'b00100 ;29parameter S3 = 5'b01000 ;30parameter S4 = 5'b10000 ;3132//============================================================================= 33//**************************** Main Code *******************************34//============================================================================= 3536always @(posedge sclk or negedge s_rst_n) begin37if(!s_rst_n)38 current_state <= S0;39else40 current_state <= next_state;41end4243always @(*) begin44 next_state = S0;45case(current_state)46 S0:begin47if(din == 1'b1) // 148 next_state = S1;49else50 next_state = current_state; // 051end5253 S1:begin54if(din == 1'b1)55 next_state = S2; // 1156else57 next_state = S0; // 1058end5960 S2:begin61if(din == 1'b0) // 11062 next_state = S3;63else64 next_state = current_state; // 11165end6667 S3:begin68if(din == 1'b1)69 next_state = S4; // 110170else71 next_state = S0; // 110072end7374 S4:begin75if(din == 1'b1) // 1101 176 next_state = S2;77else78 next_state = S0; // 1101 079end8081default:begin82 next_state = S0;83end84endcase85end8687always @(posedge sclk or negedge s_rst_n) begin88if(!s_rst_n) begin89 dout <= 0;90end91else if(current_state == S4)92 dout <= 1;93else94 dout <= 0;95end96endmoduleView Code testbench1// ********************************************************************************* 2// Project Name : state_test3// Email :4// Create Time : 2020/06/25 06:255// Module Name : state_test_tb6// editor : qing7// Version : Rev1.0.08// ********************************************************************************* 910 `timescale 1ns/1ps11module state_test_tb;12reg sclk ;13reg s_rst_n ;14reg din ;15wire dout ;1617 state_test state_test_inst(18 .sclk (sclk ) ,19 .s_rst_n (s_rst_n ) ,20 .din (din ) ,21 .dout (dout )22 );2324initial25 sclk = 1'b0;26always #10 sclk = ~sclk;2728initial29begin30 #1;31 din = 0;32 s_rst_n = 1'b0;33 #21;34 s_rst_n = 1'b1;3536 #51;3738 din = 1;39 #20;40 din = 0;41 #20;42 din = 1;43 #20;44 din = 1;45 #20;46 din = 0;47 #20;48 din = 1;49 #20;50 din = 0;51 #30;5253 din = 1;54 #20;55 din = 0;56 #20;57 din = 1;58 #20;59 din = 1;60 #20;61 din = 0;62 #20;63 din = 1;64 #20;65 din = 0;66 #30;67end6869endmoduleView Code 五、⽶利型状态机 1101序列检测 1、状态转移图 2、Mealy 代码1// *********************************************************************************2// Project Name : mealy_state3// Email :4// Create Time : 2020/06/29 22:285// Module Name :6// editor : Qing7// Version : Rev1.0.08// Description : ⽶利型状态机 1101序列检测9// *********************************************************************************1011module mealy_state(12input sclk ,13input s_rst_n ,1415input din ,16output reg dout17 );1819//========================================================================\ 20// =========== Define Parameter and Internal signals ===========21//========================================================================/24reg [3:0] current_state ;25reg [3:0] next_state ;2627parameter IDLE = 4'b0001 ;28parameter S0 = 4'b0010 ;29parameter S1 = 4'b0100 ;30parameter S2 = 4'b1000 ;3132//=============================================================================\ 33//**************************** State Machine *******************************34//=============================================================================\ 3536always @(posedge sclk or negedge s_rst_n) begin37if(!s_rst_n)38 current_state <= IDLE;39else40 current_state <= next_state;41end4243always @(*) begin44 next_state = IDLE;45case(current_state)46 IDLE:begin47if(din == 1'b1)48 next_state = S0;49else50 next_state = current_state;51end5253 S0:begin54if(din == 1'b1)55 next_state = S1;56else57 next_state = IDLE;58end5960 S1:begin61if(din == 1'b0)62 next_state = S2;63else64 next_state = current_state;65end6667 S2:begin68if(din == 1'b1)69 next_state = IDLE;70else71 next_state = IDLE;72end7374default:begin75 next_state = IDLE;76end77endcase78end7980always @(posedge sclk or negedge s_rst_n) begin81if(!s_rst_n)82 dout <= 1'b0;83else if(current_state == S2 && din == 1'b1)84 dout <= 1'b1;85else86 dout <= 1'b0;89endmoduleView Code testbench:1// ********************************************************************************* 2// Project Name : mealy_state3// Email :4// Create Time : 2020/06/29 23:065// Module Name : mealy_state_tb6// editor : Qing7// Version : Rev1.0.08// ********************************************************************************* 910module mealy_state_tb;11reg sclk ;12reg s_rst_n ;13reg din ;14wire dout ;1516 mealy_state mealy_state_inst(17 .sclk (sclk ),18 .s_rst_n (s_rst_n ),19 .din (din ),20 .dout (dout )21 );2223initial24 sclk = 1'b0;25always #10 sclk = ~sclk;2627initial28begin29 #1;30 din =1'b0;31 s_rst_n = 1'b0;32 #21;33 s_rst_n = 1'b1;34 #20;3536 xulie;37 #100;38 xulie;39 #100;40 xulie;41end4243task xulie;44repeat(2)45begin46 din = 1'b1;47 #40;48 din = 1'b0;49 #20;50 din = 1'b1;51 #80;52 din = 1'b1;53 #30;54 din = 1'b0;55 #30;56 din = 1'b1;57 #100;58end5960 endtask6162endmoduleView Code 六、总结 1、Moore状态机的输出是与时钟同步,Mealy状态机的输出是异步的,当输⼊发⽣变化时,输出就发⽣变化。

有限状态机主讲人:姜小波本章目录有限状态机(FSM)概述•有限状态机(Finite State Machine,FSM)的定义一个时序逻辑单元●有限状态机个时序逻辑单元✓取一个输入和一个现态✓生成输出和一个新的状态它被称为有限状态机,因为它至少有有限数量个状态。

它由组合逻辑单元和触发器组成,以使其能保持状态信息态信息。

可用状态转移表来表示现态、输入、输出和下一个状态。

●有限状态机的表达方式可用状态转移表来表示现态、输入、输出和下个状态。

InputCurrenInput 0 Input 1 …. Input nt State State 0State Next State / Output …. Next State / Output …. …. …. 1….State n …. …. …. …. …. ….状态转移表●有限状态机的表达方式也可以用状态转移图来表示与状态转移表一样的信息。

Input / OutputState0State1Input / Output状态转移图•状态机的本质对具有逻辑顺序和时序规律事件的对具有“”和“”事件的一种描述方法。

•应用思路从状态变量入手,分析每个状态的输入,状态转移和输出,从而完成电路的功能。

转移输出从完成电路的功能首先明确电路的输出关系,这些输出相当于状态的输出,回溯规划每个状态和状态转移条件与状态输入。

•有限状态机的组成合逻辑组合逻辑组合逻辑又可分为次态逻辑和输出逻辑两个部分。

其中次态逻辑的功能是用来确定有限状态机的下个中:次态逻辑的功能是用来确定有限状态机的下一个状态;输出逻辑是用来确定有限状态机的输出。

寄存器逻辑寄存器逻辑的功能:用来存储有限状态机的内部状态。

•状态机的基本要素状态:也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

输出输出指在某个状态时特定发的事件 :输出指在某一个状态时特定发生的事件。

输入:指状态机中进入每个状态的条件,有的状态机没有输入条件,其中的状态转移较为简状态机没有输入条件其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态。

1. Mealy型时序逻辑电路的原理介绍Mealy型时序逻辑电路是一种常见的数字逻辑电路,它具有特定的输入和输出状态,在输入变化时会产生相应的输出。

与另一种常见的时序逻辑电路Moore型不同,Mealy型时序逻辑电路的输出不仅与当前状态有关,还与输入信号有关。

Mealy型时序逻辑电路在一些应用中具有一定的优势。

2. Mealy型时序逻辑电路的结构Mealy型时序逻辑电路由状态机和组合逻辑电路组成。

状态机用来存储当前的状态,而组合逻辑电路则根据当前状态和输入信号产生相应的输出。

这种结构使得Mealy型时序逻辑电路能够根据输入和当前状态快速响应,并产生相应的输出。

3. Mealy型时序逻辑电路的工作原理Mealy型时序逻辑电路的工作原理是在时钟的驱动下,根据输入信号和当前状态,组合逻辑电路产生输出。

与Moore型不同,Mealy型的输出与输入信号直接相关,因此能够更快地响应输入变化,并产生相应的输出。

4. Mealy型时序逻辑电路的应用Mealy型时序逻辑电路广泛应用于数字系统中,例如通信设备、计算机系统、控制系统等。

由于其快速响应输入的特点,Mealy型时序逻辑电路在需要实时处理输入信号并产生相应输出的应用中具有一定的优势。

5. Mealy型时序逻辑电路的优缺点与Moore型时序逻辑电路相比,Mealy型时序逻辑电路的优点在于能够更快地响应输入变化,并产生相应的输出;缺点在于输出和状态的关系更为复杂,设计和调试相对困难。

6. Mealy型时序逻辑电路的设计与实现Mealy型时序逻辑电路的设计与实现涉及状态转移图、状态表、状态方程、输出方程等内容,需要根据具体的应用需求进行设计和优化。

在实际应用中,可以通过FPGA、ASIC等器件来实现Mealy型时序逻辑电路。

7. 结论Mealy型时序逻辑电路作为一种常见的数字逻辑电路,在数字系统中具有重要的应用价值。

它能够根据输入和当前状态快速产生相应的输出,适用于需要实时响应输入信号的应用场景。

简述有限状态机的分类和区别

有限状态机是一种用于描述系统行为的数学模型,可以分为两种类型:确定性有限状态机和非确定性有限状态机。

确定性有限状态机是指在给定的输入条件下,每个状态只能有一种确定的下一步状态,因此它的转移函数是确定的。

而非确定性有限状态机则允许在给定输入条件下,一个状态可以有多种可能的下一步状态,因此它的转移函数是非确定的。

此外,有限状态机还可以分为Moore型和Mealy型。

Moore型的输出只依赖于当前状态,而不依赖于输入;而Mealy型的输出则同时依赖于当前状态和输入。

总之,有限状态机的分类和区别主要体现在其转移函数和输出函数的确定性和依赖关系上。

在实际应用中,选择适合的类型可以更好地描述和控制系统行为。

- 1 -。

有限状态机(Finite State Machine )1、有限状态机的基本概念有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

在数字电路系统中,有限状态机时一种十分重要的时序逻辑电路模块,它对数字系统的设计具有十分重要的作用。

有限状态机一般用来描述数字数字系统的控制单元,是许多数字系统的核心部件。

有限状态机由组合逻辑和寄存器逻辑组成。

其中,寄存器逻辑的功能是存储有限状态机的内部状态;而组合逻辑有可以分为次态逻辑和输出逻辑两部分,次态逻辑的功能是确定有限状态机的下一个状态,输出逻辑的功能是确定有限状态机的输出。

在实际的应用中,根据有限状态机是否使用输入信号,设计人员经常将其分为Moore型有限状态机和Mealy型有限状态机两种类型。

⑴Moore型有限状态机其输出信号仅与当前状态有关,即可以把Moore型有限状态的输出看成是当前状态的函数。

其结构框图如图1.图1 Moore型有限状态机的结构⑵Mealy型有限状态机其输出信号不仅与当前状态有关,而且还与所有的输入信号有关,即可以把Mealy型有限状态机的输出看成是当前状态和所有输入信号的函数。

其结构框图如图2.图2 Mealy型有限状态机的结构这两种有限状态机的主要区别在于:Moore型有限状态机仅与当前状态有关,而与输入信号无关。

Mealy型有限状态机不但与当前状态有关,还与输入信号有关。

2、为什么要使用有限状态机♦ 有限状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点。

♦ 状态机的结构模式相对简单。

♦ 状态机容易构成性能良好的同步时序逻辑模块。

♦ 状态机的VHDL表述丰富多样。

♦ 在高速运算和控制方面,状态机更有其巨大的优势。

♦ 就可靠性而言,状态机的优势也是十分明显的。

3、描述有限状态机应该包含的内容⑴至少包含一个状态信号,用来指定状态机的状态。

⑵时钟信号,为有限状态机的状态转换提供时钟信号。

⑶状态转移指定,用于指定有限状态机的状态之间转换的逻辑关系。

⑷输出指定,用来指明有限状态机两状态之间转换的结果。

⑸复位信号,用于有限状态机从任意状态到复位状态的转换。

4、有限状态机的描述方法一般描述有限状态机应遵循一定的语法规则:状态机的状态:用枚举类型数据进行定义。

状态机的次态逻辑、输出逻辑和状态寄存器等一般用并行信号赋值语句、IF语句或CASE 语句等语句进行描述。

有限状态机的各种描述风格描述风格功能划分进程数A 1、次态逻辑、状态寄存器、输出逻辑1B 1、次态逻辑、状态寄存器2、输出逻辑2C 1、次态逻辑2、状态寄存器、输出逻辑2D 1、次态逻辑、输出逻辑2、状态寄存器2E 1、状态逻辑2、状态寄存器3、输出逻辑3有限状态机各种描述风格对逻辑综合的结果影响很大,一般地,时序逻辑电路与组合逻辑电路分别用不同的进程进行描述,综合后不会生成多余的寄存器,占用硬件资源输省;若把时序逻辑电路与组合逻辑电路混合在同一个进程描述,逻辑综合时,可能生成数目较多的多余寄存器,占用硬件资源会大大增加。

5、用VHDL设计状态机的具体步骤⑴根据具体的状态机设计要求,确定选择Moore型状态机还是选择Mealy型状态机。

⑵根据系统要求确定状态数量、状态转移的条件和各状态输出信号的赋值,并画出状态转移图或状态转换表;⑶根据状态转移图或状态转换表编写状态机的VHDL程序;⑷利用EDA工具对状态机的功能进行仿真验证。

6、一般状态机的VHDL设计用VHDL设计有限状态机方法有多种,但最一般和最常用的状态机设计通常包括说明部分,主控时序部分,主控组合部分和辅助进程部分。

1) 说明部分说明部分中使用TYPE语句定义新的数据类型,此数据类型为枚举型,其元素通常都用状态机的状态名来定义。

状态变量定义为信号,便于信息传递,并将状态变量的数据类型定义为含有既定状态元素的新定义的数据类型。

说明部分一般放在结构体的ARCHITECTURE和BEGIN之间。

2) 主控时序进程主控时序进程是指负责状态机运转和在时钟驱动正负现状态机转换的进程。

状态机随外部时钟信号以同步方式工作,当时钟的有效跳变到来时,时序进程将代表次态的信号next_state 中的内容送入现态信号current_state中,而next_state中的内容完全由其他进程根据实际情况而定,此进程中往往也包括一些清零或置位的控制信号。

3) 主控组合进程根据外部输入的控制信号(包括来自外部的和状态机内容的非主控进程的信号)或(和)当前状态值确定下一状态next_state的取值内容,以及对外或对内部其他进程输出控制信号的内容。

4) 辅助进程用于配合状态机工作的组合、时序进程或配合状态机工作的其他时序进程。

在一般状态机的设计过程中,为了能获得可综合的,高效的VHDL状态机描述,建议使用枚举类数据类型来定义状态机的状态,并使用多进程方式来描述状态机的内部逻辑。

例如可使用两个进程来描述,—个进程描述时序逻辑,包括状态寄存器的工作和寄存器状态的输出,另一个进程描述组合逻辑,包括进程间状态值的传递逻辑以及状态转换值的输出。

必要时还可以引入第三个进程完成其它的逻辑功能。

下例描述的状态机由两个主控进程构成,其中进程REG为主控时序进程,COM为主控组合进程。

[例]LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY s_machine ISPORT (clk, reset: IN STD_LOGIC;State_inputs: IN STD_LOGIC_VECTOR(0 TO 1);comb_outputs: OUT STD_LOGIC_VECTOR(0 TO 1));END ENTITY s_machine;ARCHITECTURE behv OF s_machine ISTYPE states IS (st0,st1,st2,st3);--定义states为枚举型数据类型SIGNAL current_state, next_state : states;BEGINREG: PROCESS (reset, clk) --时序逻辑进程BEGINIF reset='1' THEN--异步复位Current_state<=st0;ELSIF clk='1' AND clk'EVENT THENcurrent_state<=next_state; --当检测到时钟上升沿时转换至下一状态END IF;END PROCESS; --由信号current_state将当前状态值带出此进程,进入进程COM COM: PROCESS(current_state, state_Inputs) --组合逻辑进程BEGINCASE current_state IS -- 确定当前状态的状态值WHEN st0 =>comb_outputs <= "00"; --初始状态译码输出"00"IF state_inputs="00" THEN --根据外部的状态控制输入"00"next_state<=st0; --在下一时钟后,进程REG的状态将维持为st0ELSEnext_state<=st1; --否则,在下一时钟后,进程REG的状态将为st1END IF;WHEN st1=> comb_outputs<="01"; --对应状态st1的译码输出"01"IF state_inputs="00" THEN --根据外部的状态控制输人"00"next_state<=st1; --在下一时钟后,进程REG的状态将维持为st1ELSEnext_state<=st2; -- 否则,在下一时钟后,进程REG的状态将为st2END IF;WHEN st2=> comb_outputs<="10"; --以下依次类推IF state_inputs="11" THENnext_state<=st2;ELSEnext_state<=st3;END IF;WHEN st3=>comb_outputs<="11";IF state_inputs="11" THENnext_state<=st3;ELSEnext_state<=st0;END IF;END CASE;END PROCESS;END ARCHITECTURE behv;图3为上述状态机的工作时序图。

reset为异步复位信号,低电平有效,而clk为上升沿有效。

如在第3个脉冲上升沿到来时current_state=“st0”,state_inputs=“01”,输出comb_outputs=“01”。

第4个脉冲上升沿到来时current_state=“st1”,state_inputs=“00”,输出comb_outputs=“01”。

综合后的RTL图如图4所示。

图3 上例中状态机的工作时序图图4上例中状态机的RTL图一般来说,程序的不同进程间是并行运行的,但由于敏感信号设置的不同和电路的延迟,在时序上进程间的动作是有先后的。

如对上例中的状态转换行为来说,有进程REG和COM,它们的敏感信号表分别为(reset,clk)和(current_state,state_inputs),在clk上升沿到来时,进程REG将首先运行,完成状态转换的赋值操作。

如果外部控制信号state_inputs不变,只有当来自进程REG的信号current_state改变时,进程COM才开始动作,并将根据current_state 和state_inputs的值来决定下一有效时钟沿到来后,进程REG的状态转换方向。

这个状态机的两位组合逻辑输出comb_outputs是对当前状态的译码。

我们可以通过这个输出值来了解状态机内部的运行情况,同时还可以利用外部控制信号state_inputs任意改变状态机的状态变化模式。

注意:在上例中,有两个信号起到了互反馈的作用,完成了两个进程间的信息传递的功能,这两个信号分别是current_state〔进程REG->进程COM)和next_state(进程COM->进程REG)。

在VHDL中可以有两种方式来创建反馈机制:即使用信号的方式和使用变量的方式。

通常倾向于使用信号的方式(如例7.1)。

一般而言,在进程中使用变量传递数据,然后使用信号将数据带出进程。