有限状态机

- 格式:ppt

- 大小:605.00 KB

- 文档页数:51

1.1概述有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

有限状态机又可以认为是组合逻辑和寄存器逻辑的一种组合。

状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情,其实这就是状态机的本质。

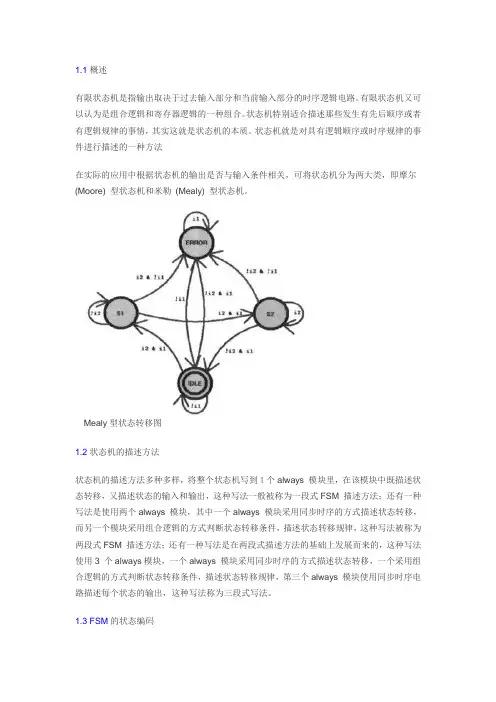

状态机就是对具有逻辑顺序或时序规律的事件进行描述的一种方法在实际的应用中根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔(Moore) 型状态机和米勒(Mealy) 型状态机。

Mealy型状态转移图1.2状态机的描述方法状态机的描述方法多种多样,将整个状态机写到1个always 模块里,在该模块中既描述状态转移,又描述状态的输入和输出,这种写法一般被称为一段式FSM 描述方法;还有一种写法是使用两个always 模块,其中一个always 模块采用同步时序的方式描述状态转移,而另一个模块采用组合逻辑的方式判断状态转移条件,描述状态转移规律,这种写法被称为两段式FSM 描述方法;还有一种写法是在两段式描述方法的基础上发展而来的,这种写法使用3 个always模块,一个always 模块采用同步时序的方式描述状态转移,一个采用组合逻辑的方式判断状态转移条件,描述状态转移规律,第三个always 模块使用同步时序电路描述每个状态的输出,这种写法称为三段式写法。

1.3 FSM的状态编码二进制码(Binary)和格雷码(Gray)属于压缩状态编码,这种编码的优点是使用的状态向量最少,但是需要较多的逻辑资源用来状态译码。

二进制码从一个状态转换到相邻状态时,可能有多个比特位发生变化,易产生中间状态转移问题,状态机的速度也要比采用其它编码方式慢。

格雷码两个相邻的码值仅有一位就可区分,这将会减少电路中相邻物理信号线同时变化的情况,因而可以减少电路中的电噪声。

Johnson码也有同样的特点,但是要用较多的位数。

独热码(One-hot)指对任意给定的状态,状态寄存器中只有l位为1,其余位都为0。

有限状态机(Finite State Machine )1、有限状态机的基本概念有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。

在数字电路系统中,有限状态机时一种十分重要的时序逻辑电路模块,它对数字系统的设计具有十分重要的作用。

有限状态机一般用来描述数字数字系统的控制单元,是许多数字系统的核心部件。

有限状态机由组合逻辑和寄存器逻辑组成。

其中,寄存器逻辑的功能是存储有限状态机的内部状态;而组合逻辑有可以分为次态逻辑和输出逻辑两部分,次态逻辑的功能是确定有限状态机的下一个状态,输出逻辑的功能是确定有限状态机的输出。

在实际的应用中,根据有限状态机是否使用输入信号,设计人员经常将其分为Moore型有限状态机和Mealy型有限状态机两种类型。

⑴Moore型有限状态机其输出信号仅与当前状态有关,即可以把Moore型有限状态的输出看成是当前状态的函数。

其结构框图如图1.图1 Moore型有限状态机的结构⑵Mealy型有限状态机其输出信号不仅与当前状态有关,而且还与所有的输入信号有关,即可以把Mealy型有限状态机的输出看成是当前状态和所有输入信号的函数。

其结构框图如图2.图2 Mealy型有限状态机的结构这两种有限状态机的主要区别在于:Moore型有限状态机仅与当前状态有关,而与输入信号无关。

Mealy型有限状态机不但与当前状态有关,还与输入信号有关。

2、为什么要使用有限状态机♦ 有限状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点。

♦ 状态机的结构模式相对简单。

♦ 状态机容易构成性能良好的同步时序逻辑模块。

♦ 状态机的VHDL表述丰富多样。

♦ 在高速运算和控制方面,状态机更有其巨大的优势。

♦ 就可靠性而言,状态机的优势也是十分明显的。

3、描述有限状态机应该包含的内容⑴至少包含一个状态信号,用来指定状态机的状态。

⑵时钟信号,为有限状态机的状态转换提供时钟信号。

⑶状态转移指定,用于指定有限状态机的状态之间转换的逻辑关系。

一般有限状态机的组成

一般有限状态机由以下几个组成部分组成:

1. 状态(State):有限状态机包含一个状态集合,每个状态代表

系统的一个特定状态或条件。

2. 输入(Input):有限状态机接受一系列输入信号,这些输入信

号触发状态转换。

3. 输出(Output):有限状态机根据当前状态和输入,可能会产

生输出信号。

4. 状态转换规则(Transition rule):有限状态机定义了状态之间

的转换规则,这些规则指定了在给定输入条件下如何从一个状态转换到另一个状态。

5. 初始状态(Initial state):有限状态机在开始时处于初始状态。

6. 终止状态(Terminal state):有限状态机可能有一个或多个终

止状态,在达到终止状态时,有限状态机停止运行。

7. 常见的有限状态机还可以包含以下特殊类型的状态:超限状态、没有默认转换状态、自环状态等。

这些组成部分共同定义了有限状态机的行为,它们用于描述系统的状态变化及相应的动作。

有限状态机原理

有限状态机(Finite State Machine, FSM)是一种计算模型,用于描述系统或算法的行为。

它由一组有限个状态、一组可能的输入信号和一组定义状态转换规则的状态转换函数组成。

在任意时刻,FSM都处于一个特定的状态,等待输入信号触发状态转换。

有限状态机具有以下基本特点:

1. 状态:有限状态机有一组预定义的状态,每个状态表示系统或算法的一种行为或状态。

2. 输入信号:系统或算法接收一组可能的输入信号,每个输入信号可能触发状态的转换或执行某种操作。

3. 状态转换:有限状态机通过状态转换函数定义可能的状态转换规则,以及在特定输入信号下从一个状态转换到另一个状态的动作或操作。

4. 动作:状态转换可以伴随着执行特定的动作或操作,用于改变系统的状态或执行一些其他的操作。

有限状态机应用广泛,可以用于描述各种系统的行为,如计算机中的指令执行、网络通信协议、自动控制系统等。

它可以帮助开发者理清系统的行为逻辑,简化复杂系统的设计和实现。

有限状态机还可以通过组合、嵌套等方式进行组合和扩展,以应对更加复杂的问题。

有限状态机的理解c++有限状态机(Finite State Machine,FSM)是一种数学模型,用于描述一个系统在不同状态下的行为。

它是由一组状态、一组输入信号和一组输出信号组成,通过根据当前状态和输入信号来确定下一状态,并根据当前状态和输出信号来产生相应的输出。

有限状态机主要包含以下几个概念:1. 状态(State):系统在不同时间点可能处于的各种状态,比如初始状态、中间状态、结束状态等。

状态可以用一个变量来表示,在C++中可以使用枚举类型来定义每个状态。

示例代码:```cppenum class State {INIT,PROCESSING,FINISHED};```2. 输入信号(Input):触发状态机状态转换的外部事件或条件。

当输入信号发生时,状态机会根据当前状态和输入信号进行状态转换。

示例代码:```cppenum class Input {START,PAUSE,RESUME,STOP};```3. 输出信号(Output):在特定状态下,状态机可以执行一些操作或者产生某些输出结果。

输出信号可以用来通知外部系统状态机的行为。

示例代码:```cppenum class Output {NEXT_STEP,PROCESSING_COMPLETE,ERROR};```4. 状态转换表(Transition Table):用来描述不同状态下,根据输入信号产生的状态转换。

状态转换表可以使用二维数组或者哈希表的方式来表示。

示例代码:```cppstd::unordered_map<State, std::unordered_map<Input, State>> transitionTable = {{State::INIT, {{Input::START, State::PROCESSING}}},{State::PROCESSING, {{Input::PAUSE,State::PROCESSING}, {Input::STOP, State::FINISHED}}},{State::FINISHED, {}}};```有了上述概念的基础,我们可以编写一个简单的有限状态机的实现。

有限状态机算法引言有限状态机(Finite State Machine,简称FSM)是一种计算模型,它能够根据输入的符号序列在一系列预定义的状态之间进行转换。

有限状态机算法是一种基于有限状态机模型的算法,用于解决各种问题,如语法分析、编译器设计、自动控制等。

本文将对有限状态机算法进行全面、详细、完整且深入的探讨。

有限状态机的基本概念有限状态机由一组状态和状态之间的转移函数组成。

状态表示系统所处的某个特定状态,转移函数定义了状态之间的转换规则。

有限状态机根据输入符号序列和当前状态,通过执行转移函数来改变状态,并产生相应的输出。

有限状态机的分类有限状态机可以分为确定性有限状态机(Deterministic Finite State Machine,简称DFSM)和非确定性有限状态机(Nondeterministic Finite State Machine,简称NFSM)。

DFSM在任何给定时间只能处于一个状态,并且每个输入符号都有唯一的下一个状态。

NFSM在任何给定时间可以处于多个状态,并且每个输入符号可以有多个可能的下一个状态。

有限状态机的表示方法有限状态机可以通过状态转移图或状态转移表来表示。

状态转移图使用节点表示状态,使用边表示状态之间的转移。

状态转移表是一个二维表格,行表示当前状态,列表示输入符号,表格中的元素表示下一个状态。

以下是一个简单的状态转移图示例:+---a---+| |V |(A)---b-->(B)| ^c || |+-------+有限状态机的应用有限状态机算法在许多领域都有广泛的应用。

下面列举了一些常见的应用场景:1. 语法分析在编译器设计中,有限状态机算法用于解析和分析源代码的语法结构。

通过定义一系列的状态和转移规则,可以将输入的源代码转换为语法树或执行代码。

2. 自动控制有限状态机算法在自动控制系统中起着重要的作用。

例如,交通信号灯控制系统可以使用有限状态机来确定不同状态下的信号灯颜色和转换规则。

状态机数据结构状态机是一种用于描述系统状态和状态之间转换关系的数学模型。

它在计算机科学和工程领域有着广泛的应用。

本文将介绍状态机的基本概念、应用场景以及一些常用的状态机数据结构。

一、基本概念状态机是由一组状态和一组状态转换规则组成的。

状态表示系统的某种特定情况或条件,而状态转换规则描述了系统在不同状态下的行为。

状态机可以分为有限状态机(FSM)和无限状态机(ISM)两种类型。

1. 有限状态机(FSM)有限状态机是指状态的数量是有限的。

它包含一个初始状态和一组终止状态,以及一组状态转换规则。

当系统执行某个操作或接收到某个输入时,根据当前状态和输入,状态机会根据事先定义好的转换规则进行状态的转换。

2. 无限状态机(ISM)无限状态机是指状态的数量是无限的。

它通常用于描述具有连续状态的系统,如物理系统或网络协议等。

无限状态机通常通过微分方程或差分方程来描述状态之间的转换关系。

二、应用场景状态机在计算机科学和工程领域有着广泛的应用。

下面是一些常见的应用场景:1. 系统建模和设计:状态机可以帮助开发人员对系统行为和状态进行建模和设计。

它可以帮助开发人员更好地理解和分析系统的行为,并提供指导性的设计原则。

2. 编译器和解释器:状态机可以用于编译器和解释器中的词法分析和语法分析阶段。

通过定义适当的状态和状态转换规则,可以有效地分析和识别输入的代码片段。

3. 协议分析和验证:状态机可以用于描述和验证网络协议的行为。

通过定义协议的状态和状态转换规则,可以分析和验证协议的正确性和安全性。

4. 控制系统和自动化:状态机可以用于描述和控制各种自动化系统,如工业控制系统、机器人控制系统等。

通过定义系统的状态和状态转换规则,可以实现对系统行为的控制和调度。

三、常用的状态机数据结构在实际应用中,为了方便描述和实现状态机,常常使用一些特定的数据结构来表示状态和状态转换规则。

下面是一些常用的状态机数据结构:1. 状态表:状态表是一个二维表格,其中每一行表示一个状态,每一列表示一个输入。

简要说明状态机的分类,以及状态机的表达方式状态机是一种抽象的数学模型,用于描述在不同状态下的行为和

转换,常用于计算机科学中控制流程和状态转换的场景。

状态机的分类:

1、有限状态机(Finite State Machine,FSM):是指状态的数

量是有限的,并且每个状态都有明确的转移条件和转移方向的状态机。

FSM通常用状态图或状态表来表示,常用于字符串匹配、语法分析等领域。

2、无限状态机(Infinite State Machine,ISM):是指状态的

数量是无限的,没有明确的转移条件和转移方向的状态机。

ISM通常用状态空间图或状态空间表达式来表示,常用于电路设计、控制系统等领域。

状态机的表达方式:

1、状态图(State Diagram):是一种用于描述状态和状态之间

转移的图形表示方法,通常由状态节点和转移边组成。

状态图可以用于描述有限状态机的行为。

2、状态表(State Table):是一种用于描述状态和转移条件的

表格表示方法,通常由状态、输入、输出和转移条件组成。

状态表可以用于描述有限状态机的行为。

3、状态空间图(State-Space Diagram):是一种用于描述状态空间中状态和状态之间转移的图形表示方法,通常由状态节点和转移边组成。

状态空间图可以用于描述无限状态机的行为。

4、状态空间表达式(State-Space Expression):是一种用于描述状态空间中状态和转移条件的数学表达式,通常由状态变量、输入变量、输出变量和转移方程组成。

状态空间表达式可以用于描述无限状态机的行为。