锁相环式数字频率合成器(上)

- 格式:doc

- 大小:13.18 MB

- 文档页数:17

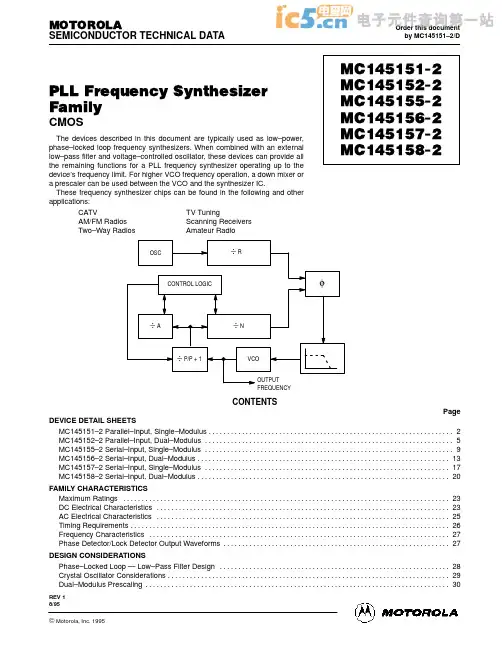

PLL Frequency Synthesizer FamilyCMOSThe devices described in this document are typically used as low–power,phase–locked loop frequency synthesizers. When combined with an external low–pass filter and voltage–controlled oscillator, these devices can provide all the remaining functions for a PLL frequency synthesizer operating up to the device’s frequency limit. For higher VCO frequency operation, a down mixer or a prescaler can be used between the VCO and the synthesizer IC.These frequency synthesizer chips can be found in the following and other applications:CATV TV Tuning AM/FM Radios Scanning Receivers Two–Way Radios Amateur RadioCONTENTSPageDEVICE DETAIL SHEETSMC145151–2 Parallel–Input, Single–Modulus 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . MC145152–2 Parallel–Input, Dual–Modulus 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . MC145155–2 Serial–Input, Single–Modulus 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . MC145156–2 Serial–Input, Dual–Modulus 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . MC145157–2 Serial–Input, Single–Modulus 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . MC145158–2 Serial–Input, Dual–Modulus 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . FAMILY CHARACTERISTICSMaximum Ratings 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DC Electrical Characteristics 23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AC Electrical Characteristics 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Timing Requirements 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Frequency Characteristics 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Phase Detector/Lock Detector Output Waveforms 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DESIGN CONSIDERATIONSPhase–Locked Loop — Low–Pass Filter Design 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Crystal Oscillator Considerations 29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Dual–Modulus Prescaling 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Order this document by MC145151–2/DMOTOROLASEMICONDUCTOR TECHNICAL DATAMC145151-2MC145152-2MC145155-2MC145156-2MC145157-2MC145158-2Parallel-Input PLL Frequency SynthesizerInterfaces with Single–Modulus PrescalersThe MC145151–2 is programmed by 14 parallel–input data lines for the N counter and three input lines for the R counter. The device features consist of a reference oscillator, selectable–reference divider, digital–phase detector, and 14–bit programmable divide–by–N counter.The MC145151–2 is an improved–performance drop–in replacement for the MC145151–1. The power consumption has decreased and ESD and latch–up performance have improved.•Operating T emperature Range: – 40 to 85°C•Low Power Consumption Through Use of CMOS T echnology • 3.0 to 9.0 V Supply Range•On– or Off–Chip Reference Oscillator Operation •Lock Detect Signal•÷ N Counter Output Available•Single Modulus/Parallel Programming•8 User–Selectable ÷ R Values: 8, 128, 256, 512, 1024, 2048, 2410, 8192•÷ N Range = 3 to 16383•“Linearized” Digital Phase Detector Enhances Transfer Function Linearity •Two Error Signal Options: Single–Ended (Three–State) or Double–Ended •Chip Complexity: 8000 FET s or 2000 Equivalent GatesMOTOROLASEMICONDUCTOR TECHNICAL DATAMC145151-2Parallel-Input PLL Frequency SynthesizerInterfaces with Dual–Modulus PrescalersThe MC145152–2 is programmed by sixteen parallel inputs for the N and A counters and three input lines for the R counter. The device features consist of a reference oscillator, selectable–reference divider, two–output phase detector,10–bit programmable divide–by–N counter, and 6–bit programmable ÷ A counter.The MC145152–2 is an improved–performance drop–in replacement for the MC145152–1. Power consumption has decreased and ESD and latch–up performance have improved.•Operating T emperature Range: – 40 to 85°C•Low Power Consumption Through Use of CMOS T echnology • 3.0 to 9.0 V Supply Range•On– or Off–Chip Reference Oscillator Operation •Lock Detect Signal•Dual Modulus/Parallel Programming•8 User–Selectable ÷ R Values: 8, 64, 128, 256, 512, 1024, 1160, 2048•÷ N Range = 3 to 1023, ÷ A Range = 0 to 63•Chip Complexity: 8000 FET s or 2000 Equivalent Gates •See Application Note AN980MOTOROLASEMICONDUCTOR TECHNICAL DATAMC145152-2Serial-Input PLL Frequency SynthesizerInterfaces with Single–Modulus PrescalersThe MC145155–2 is programmed by a clocked, serial input, 16–bit data stream. The device features consist of a reference oscillator, selectable–refer-ence divider, digital–phase detector, 14–bit programmable divide–by–N counter, and the necessary shift register and latch circuitry for accepting serial input data.The MC145155–2 is an improved–performance drop–in replacement for the MC145155–1. Power consumption has decreased and ESD and latch–up performance have improved.•Operating T emperature Range: – 40 to 85°C•Low Power Consumption Through Use of CMOS T echnology • 3.0 to 9.0 V Supply Range•On– or Off–Chip Reference Oscillator Operation with Buffered Output •Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs •Lock Detect Signal•Two Open–Drain Switch Outputs•8 User–Selectable ÷ R Values: 16, 512, 1024, 2048, 3668, 4096, 6144,8192•Single Modulus/Serial Programming •÷ N Range = 3 to 16383•“Linearized” Digital Phase Detector Enhances Transfer Function Linearity •Two Error Signal Options: Single–Ended (Three–State) or Double–Ended •Chip Complexity: 6504 FET s or 1626 Equivalent GatesMOTOROLASEMICONDUCTOR TECHNICAL DATAMC145155-2MC145151–2 through MC145158–213Serial-Input PLL Frequency SynthesizerInterfaces with Dual–Modulus PrescalersThe MC145156–2 is programmed by a clocked, serial input, 19–bit data stream. The device features consist of a reference oscillator, selectable–refer-ence divider, digital–phase detector, 10–bit programmable divide–by–N counter, 7–bit programmable divide–by–A counter, and the necessary shift register and latch circuitry for accepting serial input data.The MC145156–2 is an improved–performance drop–in replacement for the MC145156–1. Power consumption has decreased and ESD and latch–up performance have improved.•Operating T emperature Range: – 40 to 85°C•Low Power Consumption Through Use of CMOS T echnology • 3.0 to 9.0 V Supply Range•On– or Off–Chip Reference Oscillator Operation with Buffered Output •Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs •Lock Detect Signal•Two Open–Drain Switch Outputs •Dual Modulus/Serial Programming•8 User–Selectable ÷ R Values: 8, 64, 128, 256, 640, 1000, 1024, 2048•÷ N Range = 3 to 1023, ÷ A Range = 0 to 127•“Linearized” Digital Phase Detector Enhances Transfer Function Linearity •Two Error Signal Options: Single–Ended (Three–State) or Double–Ended •Chip Complexity: 6504 FET s or 1626 Equivalent GatesMOTOROLASEMICONDUCTOR TECHNICAL DATAMC145156-2MC145151–2 through MC145158–2MOTOROLA15OUTPUT PINSPD outPhase Detector A Output (Pin 6)Three–state output of phase detector for use as loop–error signal. Double–ended outputs are also available for this pur-pose (see φV and φR ).Frequency f V > f R or f V Leading: Negative Pulses Frequency f V < f R or f V Lagging: Positive PulsesFrequency f V = f R and Phase Coincidence: High–Imped-ance State φR , φVPhase Detector B Outputs (Pins 4, 3)These phase detector outputs can be combined externally for a loop–error signal. A single–ended output is also avail-able for this purpose (see PD out ).If frequency f V is greater than f R or if the phase of f V is leading, then error information is provided by φV pulsing low.φR remains essentially high.If the frequency f V is less than f R or if the phase of f V is lagging, then error information is provided by φR pulsing low.φV remains essentially high.If the frequency of f V = f R and both are in phase, then both φV and φR remain high except for a small minimum time period when both pulse low in phase.MCDual–Modulus Prescale Control Output (Pin 8)Signal generated by the on–chip control logic circuitry for controlling an external dual–modulus prescaler. The MC level will be low at the beginning of a count cycle and will remain low until the ÷ A counter has counted down from its programmed value. At this time, MC goes high and remains high until the ÷ N counter has counted the rest of the way down from its programmed value (N – A additional counts since both ÷ N and ÷ A are counting down during the first por-tion of the cycle). MC is then set back low, the counterspreset to their respective programmed values, and the above sequence repeated. This provides for a total programmable divide value (N T ) = N P + A where P and P + 1 represent the dual–modulus prescaler divide values respectively for high and low MC levels, N the number programmed into the ÷ N counter, and A the number programmed into the ÷ A counter.LDLock Detector Output (Pin 9)Essentially a high level when loop is locked (f R , f V of same phase and frequency). LD pulses low when loop is out of lock.SW1, SW2Band Switch Outputs (Pins 14, 15)SW1 and SW2 provide latched open–drain outputs corre-sponding to data bits numbers one and two. These outputs can be tied through external resistors to voltages as high as 15 V, independent of the V DD supply voltage. These are typically used for band switch functions. A logic 1 causes the output to assume a high–impedance state, while a logic 0causes the output to be low.REF outBuffered Reference Oscillator Output (Pin 17)Buffered output of on–chip reference oscillator or exter-nally provided reference–input signal.POWER SUPPLYV DDPositive Power Supply (Pin 5)The positive power supply potential. This pin may range from + 3 to + 9 V with respect to V SS .V SSNegative Power Supply (Pin 7)The most negative supply potential. This pin is usually ground.MC145151–2 through MC145158–217Serial-Input PLL Frequency SynthesizerInterfaces with Single–Modulus PrescalersThe MC145157–2 has a fully programmable 14–bit reference counter, as well as a fully programmable ÷ N counter. The counters are programmed serially through a common data input and latched into the appropriate counter latch,according to the last data bit (control bit) entered.The MC145157–2 is an improved–performance drop–in replacement for the MC145157–1. Power consumption has decreased and ESD and latch–up performance have improved.•Operating T emperature Range: – 40 to 85°C•Low Power Consumption Through Use of CMOS T echnology • 3.0 to 9.0 V Supply Range•Fully Programmable Reference and ÷ N Counters •÷ R Range = 3 to 16383•÷ N Range = 3 to 16383•f V and f R Outputs •Lock Detect Signal•Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs •“Linearized” Digital Phase Detector•Single–Ended (Three–State) or Double–Ended Phase Detector Outputs •Chip Complexity: 6504 FET s or 1626 Equivalent GatesMOTOROLASEMICONDUCTOR TECHNICAL DATAMC145157-2MOTOROLASerial-Input PLL Frequency SynthesizerInterfaces with Dual–Modulus PrescalersThe MC145158–2 has a fully programmable 14–bit reference counter, as well as fully programmable ÷ N and ÷ A counters. The counters are programmed serially through a common data input and latched into the appropriate counter latch, according to the last data bit (control bit) entered.The MC145158–2 is an improved–performance drop–in replacement for the MC145158–1. Power consumption has decreased and ESD and latch–up performance have improved.•Operating T emperature Range: – 40 to 85°C•Low Power Consumption Through Use of CMOS T echnology • 3.0 to 9.0 V Supply Range•Fully Programmable Reference and ÷ N Counters •÷ R Range = 3 to 16383•÷ N Range = 3 to 1023•Dual Modulus Capability; ÷ A Range = 0 to 127•f V and f R Outputs •Lock Detect Signal•Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs •“Linearized” Digital Phase Detector•Single–Ended (Three–State) or Double–Ended Phase Detector Outputs •Chip Complexity: 6504 FET s or 1626 Equivalent GatesMOTOROLASEMICONDUCTOR TECHNICAL DATAMC145158-2OUTPUT PINSPD outPhase Detector A Output (Pin 5)This single–ended (three–state) phase detector output produces a loop–error signal that is used with a loop filter to control a VCO.Frequency f V > f R or f V Leading: Negative Pulses Frequency f V < f R or f V Lagging: Positive Pulses Frequency f V = f R and Phase Coincidence: High–Imped-ance StateφR, φVPhase Detector B Outputs (Pins 16, 15)Double–ended phase detector outputs. These outputs can be combined externally for a loop–error signal. A single–ended output is also available for this purpose (see PD out). If frequency f V is greater than f R or if the phase of f V is leading, then error information is provided by φV pulsing low.φR remains essentially high.If the frequency f V is less than f R or if the phase of f V is lagging, then error information is provided by φR pulsing low.φV remains essentially high.If the frequency of f V = f R and both are in phase, then both φV and φR remain high except for a small minimum time period when both pulse low in phase.MCDual–Modulus Prescale Control Output (Pin 12)This output generates a signal by the on–chip control logic circuitry for controlling an external dual–modulus prescaler. The MC level is low at the beginning of a count cycle and remains low until the ÷ A counter has counted down from its programmed value. At this time, MC goes high and remains high until the ÷ N counter has counted the rest of the way down from its programmed value (N – A additional counts since both ÷ N and ÷ A are counting down during the first por-tion of the cycle). MC is then set back low, the counters pre-set to their respective programmed values, and the above sequence repeated. This provides for a total programmable divide value (N T) = N P + A where P and P + 1 represent the dual–modulus prescaler divide values respectively for high and low modulus control levels, N the number programmed into the ÷ N counter, and A the number programmed into the ÷ A counter. Note that when a prescaler is needed, the dual–modulus version offers a distinct advantage. The dual–modulus prescaler allows a higher reference frequency at the phase detector input, increasing system performance ca-pability, and simplifying the loop filter design.f R, f VR Counter Output, N Counter Output (Pins 13, 3) Buffered, divided reference and f in frequency outputs. The f R and f V outputs are connected internally to the ÷ R and ÷ N counter outputs respectively, allowing the counters to be used independently, as well as monitoring the phase detector inputs.LDLock Detector Output (Pin 7)This output is essentially at a high level when the loop is locked (f R, f V of same phase and frequency), and pulses low when loop is out of lock.REF outBuffered Reference Oscillator Output (Pin 14)This output can be used as a second local oscillator, refer-ence oscillator to another frequency synthesizer, or as the system clock to a microprocessor controller.POWER SUPPLYV DDPositive Power Supply (Pin 4)The positive power supply potential. This pin may range from + 3 to + 9 V with respect to V SS.V SSNegative Power Supply (Pin 6)The most negative supply potential. This pin is usually ground.MC145151–2 through MC145158–2MOTOROLA36Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit,and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters can and do vary in different applications. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.◊。

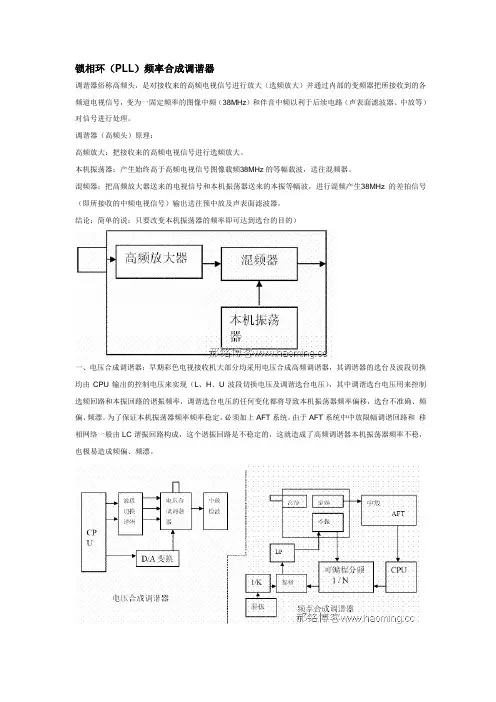

锁相环(PLL)频率合成调谐器调谐器俗称高频头,是对接收来的高频电视信号进行放大(选频放大)并通过内部的变频器把所接收到的各频道电视信号,变为一固定频率的图像中频(38MHz)和伴音中频以利于后续电路(声表面滤波器、中放等)对信号进行处理。

调谐器(高频头)原理:高频放大:把接收来的高频电视信号进行选频放大。

本机振荡器:产生始终高于高频电视信号图像载频38MHz的等幅载波,送往混频器。

混频器:把高频放大器送来的电视信号和本机振荡器送来的本振等幅波,进行混频产生38MHz的差拍信号(即所接收的中频电视信号)输出送往预中放及声表面滤波器。

结论:简单的说:只要改变本机振荡器的频率即可达到选台的目的)一、电压合成调谐器:早期彩色电视接收机大部分均采用电压合成高频调谐器,其调谐器的选台及波段切换均由CPU输出的控制电压来实现(L、H、U波段切换电压及调谐选台电压),其中调谐选台电压用来控制选频回路和本振回路的谐振频率,调谐选台电压的任何变化都将导致本机振荡器频率偏移,选台不准确、频偏、频漂。

为了保证本机振荡器频率频率稳定,必须加上AFT系统。

由于AFT系统中中放限幅调谐回路和移相网络一般由LC谐振回路构成,这个谐振回路是不稳定的,这就造成了高频调谐器本机振荡器频率不稳,也极易造成频偏、频漂。

二、频率合成调谐器1、频率合成的基本含义:是指用若干个单一频率的正弦波合成多个新的频率分量的方法(频率合成调谐器的本振频率是由晶振分频合成的)。

频率合成的方法有很多种。

下图为混频式频率合成器方框图以上图中除了三个基频外还有其“和频”及“差频”输出(还有各个频率的高次谐波输出)。

输出信号的频率稳定性由基准信号频率稳定性决定,而且输出信号频率误差等于各基准信号误差之和,因此要想减少误差除了要提高基准信号稳定度之外还应减少基准信号的个数。

2、锁相环频率合成器:其方框图类似于彩色电视接收机中的副载波恢复电路,只是在输入回路插入了一个基准信号分频器(代替色同步信号输入)而在反馈支路插入一个可编程分频器(代替900移相)。

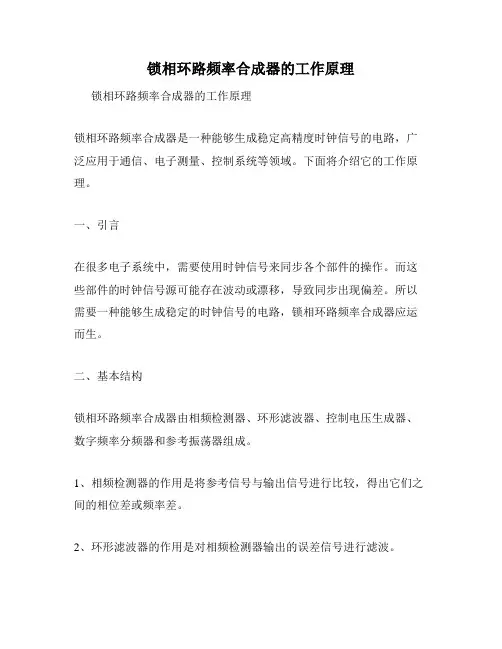

锁相环路频率合成器的工作原理锁相环路频率合成器的工作原理锁相环路频率合成器是一种能够生成稳定高精度时钟信号的电路,广泛应用于通信、电子测量、控制系统等领域。

下面将介绍它的工作原理。

一、引言在很多电子系统中,需要使用时钟信号来同步各个部件的操作。

而这些部件的时钟信号源可能存在波动或漂移,导致同步出现偏差。

所以需要一种能够生成稳定的时钟信号的电路,锁相环路频率合成器应运而生。

二、基本结构锁相环路频率合成器由相频检测器、环形滤波器、控制电压生成器、数字频率分频器和参考振荡器组成。

1、相频检测器的作用是将参考信号与输出信号进行比较,得出它们之间的相位差或频率差。

2、环形滤波器的作用是对相频检测器输出的误差信号进行滤波。

3、控制电压生成器的作用是将滤波器的输出误差信号转化为控制电压,来调整和控制输出信号的频率或相位差。

4、数字频率分频器的作用是将输出信号分频,即降低频率。

5、参考振荡器的作用是提供一个稳定的参考信号。

三、工作原理锁相环路频率合成器的工作原理分为两个阶段:捕获和锁定。

在捕获阶段,锁相环路频率合成器控制电压的输出不断改变以使输出频率趋近于参考信号频率,同时,环形滤波器将误差信号滤波,保证输出稳定,从而实现捕获参考信号的频率。

在锁定阶段,锁相环路频率合成器控制电压的输出基本不变,但仍会根据环形滤波器的输出误差信号进行微调,使得参考信号与输出信号的相位差和频率差最小,实现锁相。

四、应用实例锁相环路频率合成器广泛应用于各种电子系统中,如:1、数字通信中的时钟恢复电路。

2、多频段合成天线接收器中的频率转换器。

3、控制系统中的精密时序控制器。

4、频率合成器中的同步产生电路。

五、总结锁相环路频率合成器是一种能够生成稳定高精度时钟信号的电路,由相频检测器、环形滤波器、控制电压生成器、数字频率分频器和参考振荡器组成。

它的工作原理分为捕获阶段和锁定阶段,并广泛应用于通信、电子测量、控制系统等领域。

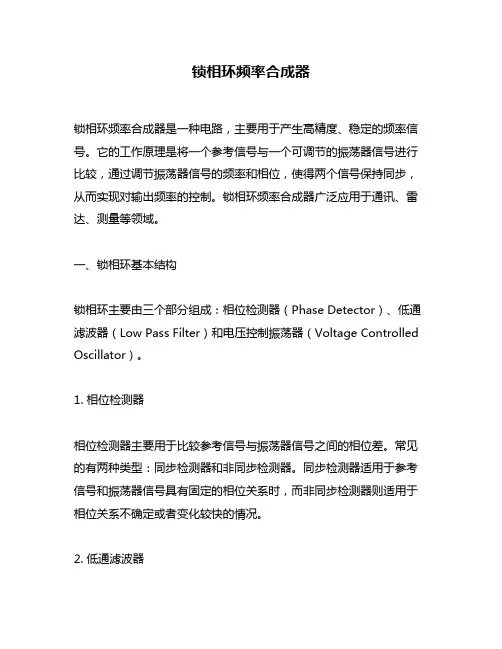

锁相环频率合成器锁相环频率合成器是一种电路,主要用于产生高精度、稳定的频率信号。

它的工作原理是将一个参考信号与一个可调节的振荡器信号进行比较,通过调节振荡器信号的频率和相位,使得两个信号保持同步,从而实现对输出频率的控制。

锁相环频率合成器广泛应用于通讯、雷达、测量等领域。

一、锁相环基本结构锁相环主要由三个部分组成:相位检测器(Phase Detector)、低通滤波器(Low Pass Filter)和电压控制振荡器(Voltage Controlled Oscillator)。

1. 相位检测器相位检测器主要用于比较参考信号与振荡器信号之间的相位差。

常见的有两种类型:同步检测器和非同步检测器。

同步检测器适用于参考信号和振荡器信号具有固定的相位关系时,而非同步检测器则适用于相位关系不确定或者变化较快的情况。

2. 低通滤波器低通滤波器主要用于平滑输出电压,并消除高频噪声干扰。

它的作用是将相位检测器输出的误差信号进行滤波,得到一个直流电压信号,这个信号被用来控制振荡器的频率和相位。

3. 电压控制振荡器电压控制振荡器(VCO)是锁相环频率合成器中最重要的部分之一。

它可以产生可调节的频率信号,并且可以通过调节输入电压来改变输出频率。

VCO通常由一个反馈环路组成,其中参考信号和VCO输出信号经过比较后产生误差信号,通过低通滤波器后输入到VCO中,从而实现对输出频率的控制。

二、锁相环工作原理锁相环工作原理可以用以下几个步骤来描述:1. 参考信号与振荡器信号进行比较,产生误差信号;2. 误差信号经过低通滤波器平滑处理后输入到VCO中;3. VCO产生新的振荡器信号,并与参考信号进行比较;4. 如果两个信号之间存在相位差,则继续调整VCO输出频率和相位,直到两个信号同步为止;5. 输出的同步信号可以用于驱动其他系统或设备。

三、锁相环应用锁相环频率合成器在通讯、雷达、测量等领域有着广泛的应用。

以下是一些常见的应用场景:1. 时钟恢复在数字通信系统中,接收端需要恢复发送端的时钟信号。

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着通信技术的飞速发展,频率合成器作为电子系统中的关键部件,其性能和稳定性直接影响到整个系统的性能。

本文将详细介绍一种基于FPGA(现场可编程门阵列)的PLL(锁相环)+DDS(直接数字合成器)的频率合成器,并对其设计原理、实现方法及性能优势进行深入探讨。

二、PLL+DDS频率合成器的工作原理PLL+DDS频率合成器通过将PLL与DDS结合,利用两者的优势来达到高精度、高稳定性的频率输出。

PLL模块主要负责跟踪和生成参考频率,而DDS模块则能够快速生成多种频率的波形。

FPGA作为核心控制器,负责协调PLL和DDS模块的工作,实现频率的合成和输出。

三、设计实现1. 硬件设计在硬件设计方面,PLL+DDS频率合成器主要包含FPGA、PLL模块、DDS模块以及输出电路等部分。

其中,FPGA作为核心控制器,负责协调整个系统的运行。

PLL模块采用高精度的锁相环电路,以实现稳定的参考频率输出。

DDS模块则采用数字方式生成多种频率的波形。

2. 软件设计在软件设计方面,需要编写FPGA的程序代码来实现对PLL 和DDS模块的控制。

通过配置FPGA的IO口,实现对PLL和DDS模块的驱动和控制。

同时,还需要编写相应的算法程序,以实现频率的合成和输出。

四、性能优势基于FPGA的PLL+DDS频率合成器具有以下优势:1. 高精度:PLL和DDS的结合使得频率合成器具有高精度的频率输出。

2. 高稳定性:通过PLL模块的锁相环电路,可以实现稳定的参考频率输出,从而提高整个系统的稳定性。

3. 快速响应:DDS模块采用数字方式生成波形,具有快速响应的特点,可以快速调整输出频率。

4. 灵活性:FPGA的可编程性使得频率合成器具有很高的灵活性,可以方便地实现多种功能的扩展和升级。

五、应用领域基于FPGA的PLL+DDS频率合成器在通信、雷达、电子测量等领域具有广泛的应用。

例如,在通信系统中,它可以为基站提供稳定的射频信号;在雷达系统中,它可以为雷达提供精确的扫描频率;在电子测量领域,它可以用于信号源的生成和测试等。

*******************实践教学*******************兰州理工大学计算机与通信学院2012年春季学期《通信系统基础实验》设计项目实验报告设计题目:锁相式数字频率合成器实验报告专业班级:设计小组名单:指导教师:陈昊目录一、设计实验目的 (3)二、频率合成基本原理 (4)2.1频率合成的概念 (4)2.2频率合成器的主要技术指标 (4)2.3锁相频率合成器 (5)三、锁相环技术 (6)3.1 锁相环工作原理 (6)3.2 锁相环CD4046芯片介绍 (6)四、基于锁相环技术的倍频器 (10)4.1 HS191芯片介绍 (10)4.2 基于锁相环技术的倍频器的设计 (12)4.2.1 工作原理 (12)3.2.2 Proteus软件仿真 (13)4.2.3 硬件实现 (14)4.2.4 锁相环参数设计 (15)五、总结与心得 (17)六、参考文献 (18)七、元器件清单 (19)一、设计实验目的1. 掌握VCO压控振荡器的基本工作原理。

2. 加深对基本锁相环工作原理的理解。

3. 熟悉锁相式数字频率合成器的电路组成与工作原理.。

二、频率合成基本原理2.1频率合成的概念频率合成是指由一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线性运算,产生具有同样稳定度和精确度的大量离散频率的过程。

实现频率合成的电路叫频率合成器,频率合成器是现代电子系统的重要组成部分。

在通信、雷达和导航等设备中,频率合成器既是发射机频率的激励信号源,又是接收机的本地振荡器;在电子对抗设备中,它可以作为干扰信号放生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

早期的频率合成是用多晶体直接合成,以后发展成用一个高稳定参考源来合成多个频率。

20世纪50年代出现了间接频率合成技术。

但在使用频段上,直到50年代中期仍局限于短波范围。

60年代中期,带有可变分频的数字锁相式频率合成器问世。

锁相环频率合成器介绍锁相环频率合成器(Phase Locked Loop Frequency Synthesizer)是一种广泛应用于电子通信、无线电设备和测量仪器中的电路。

它主要用于产生稳定且精确的输出频率信号,可以将输入信号的频率放大、分频或合成,以满足不同应用的需求。

原理锁相环频率合成器的基本原理是通过负反馈控制,将输出频率与参考频率(或参考信号)比较,然后通过调整VCO(Voltage Controlled Oscillator,电压控制振荡器)的控制电压,使其输出频率与参考频率保持同步。

简单来说,锁相环频率合成器就是将输入信号锁定到某个特定的频率上。

组成部分锁相环频率合成器由多个部分组成,包括相位比较器、环路滤波器、VCO和分频器。

相位比较器(Phase Comparator)相位比较器用于比较参考信号的相位与VCO输出信号的相位之间的差异,并产生一个误差信号。

常见的相位比较器有模型相位比较器和数字相位比较器。

环路滤波器(Loop Filter)环路滤波器用于滤波和增益控制,将相位比较器输出的误差信号转换为VCO控制电压。

环路滤波器的特性会影响系统的稳定性和锁定时间。

VCO(Voltage Controlled Oscillator)VCO是锁相环频率合成器的核心组件,它根据控制电压的变化来产生不同频率的输出信号。

VCO的输出频率与输入的控制电压成正比。

分频器(Divider)分频器用于降低输出频率。

在一些应用中,需要将VCO的高频输出信号分频得到稳定的低频信号。

工作原理锁相环频率合成器的工作过程可以分为以下几个步骤:1.参考信号与VCO输出信号经过相位比较器进行相位比较。

2.相位比较器产生误差信号,通过环路滤波器转换为控制电压。

3.控制电压作用于VCO,使其输出频率发生变化。

4.VCO输出信号经过分频器得到稳定的输出信号。

5.输出信号经过反馈回到相位比较器,与参考信号进行相位比较。

6.如果相位比较器检测到相位差异,则通过反馈机制调整控制电压,使输出频率与参考频率保持同步。

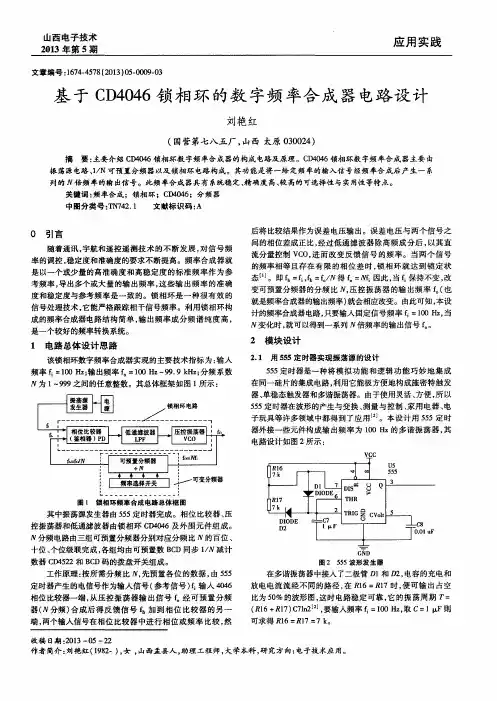

基于cd4046锁相环的数字频率合成器电路设计1. 介绍在当今的数字电子领域,频率合成器扮演着至关重要的角色,它可以将一个基础频率信号合成出多个频率信号,广泛应用于收音机、数字通信、无线电、雷达等领域。

本文将重点讨论基于cd4046锁相环的数字频率合成器电路设计,以及CD4046的基本工作原理和性能特点。

2. 基础原理CD4046作为一种锁相环集成电路,它由相位比较器、环路滤波器和振荡器组成。

在频率合成器中,CD4046可以将输入信号频率合成成另一个输出频率信号,并且具有较高的信号锁定能力。

其基本工作原理是根据输入信号频率与振荡器输出信号频率之间的差值,不断调节振荡器输出频率,直至二者频率相同,从而实现信号的合成。

3. 设计步骤(1) 确定合成频率范围:根据实际需求确定所需合成频率范围,进而选择合适的分频倍数和振荡器参数。

(2) 选择振荡器电路:根据合成频率范围选择合适的振荡器电路和频率合成器芯片,CD4046是目前较为常用的选择之一。

(3) 进行电路仿真:使用电路仿真软件对设计电路进行仿真和调试,确保电路工作稳定和合成频率准确。

(4) 调节环路参数:根据实际需求调节环路参数,如环路带宽和环路增益,以实现更精准的频率合成效果。

4. 性能分析CD4046锁相环具有较高的抗干扰能力和频率稳定性,能够在一定程度上抵抗外部环境干扰和波动。

其响应速度较快,能够实现快速锁定输入信号频率,并且具有较高的合成精度和稳定性,适用于多种频率合成场景。

5. 个人观点在设计数字频率合成器时,选择合适的频率合成器芯片对电路性能起着至关重要的作用。

CD4046锁相环作为一种可靠的集成电路芯片,具有较高的性能和稳定性,是设计高质量数字频率合成器的重要选择之一。

在实际应用中,需要根据具体需求合理设计振荡器电路和调节环路参数,以实现更加精准和稳定的频率合成效果。

总结:本文对基于CD4046锁相环的数字频率合成器电路设计进行了全面评估和探讨,介绍了其基本工作原理、设计步骤、性能分析和个人观点,并对其在数字频率合成器设计中的重要性进行了强调。

锁相环及频率合成器的原理及电路设计方案介绍引言锁相环简称PLL,是实现相位自动控制的一门技术,早期是为了解决接收机的同步接收问题而开发的,后来应用在电视机的扫描电路中。

由于锁相技术的发展,该技术已逐渐应用到通信、导航、雷达、计算机到家用电器的各个领域。

自从20世纪70年代起,随着集成电路的发展,开始出现集成的锁相环器件、通用和专用集成单片锁相环,使锁相环逐渐变成一个低成本、使用简便的多功能器件。

如今,PLL技术主要应用在调制解调、频率合成、彩电色幅载波提取、雷达、FM立体声解码等各个领域。

随着数字技术的发展,还出现了各种数字PLL器件,它们在数字通信中的载波同步、位同步、相干解调等方面起着重要的作用。

随着现代电子技术的飞快发展,具有高稳定性和准确度的频率源已经成为科研生产的重要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模集成电路的发展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环及频率合成器的原理1.1 锁相环原理PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以PLL通常用于闭环跟踪电路。

PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。

PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,PLL组成的原理框图如图1所示。

PLL中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控。

锁相式数字频率合成器的设计实验报告解析实验四锁相式数字频率合成器的设计一. 实验目的1. 掌握锁相环及频率合成器原理。

2. 利用数字锁相环CD4046设计制作频率合成器。

3. 利用有源滤波器将CD4046输出方波。

二. 实验仪器1. DSO-2902示波器/逻辑分析仪一台 2. 模拟信号源一台 3. 锁相环电路板一个 4. 微机一台5. 微机专用直流电源一台 三. 实验原理1.锁相频率合成器原理锁相频率合成器是基于锁相环路的同步原理,由一个高准度、高稳定度的参考晶体振荡器,合成出许多离散频率。

即将某一基准频率经过锁相环(PLL )的作用,产生需要的频率。

原理框图如图4-1所示。

图4-1 锁相环原理框图由图4-1可知,晶体振荡器的频率i f 经M 固定分频后得到步进参考频率REF f ,将REF f 信号作为鉴相器的基准与N 分频器的输出进行比较,鉴相器的输出d U 正比与两路输入信号是相位差,d U 经环路滤波器得到一个平均电压c U ,c U 控制压控振荡器(VCO )频率0f 的变化,使鉴相器的两路输入信号相位差不断减小,直到鉴相器的输出为零或为某一直流电平,这时称为锁定。

锁定后的频率为0//i REF f M f N f ==即()0/i REF f N M f N f ==⋅。

当预置分频数N 变化时,输出信号频率0f 随着发生变化。

锁相环中的滤波器时间常数决定了跟随输入信号的速度,同时也限制了锁相环的捕捉范围,详细原理见参考书。

2.CD4046锁相环工作原理数字锁相环CD4046由两个鉴相器、一个压控振荡器、一个源极跟随器和一个齐纳二极管组成。

鉴相器有两个共用输入端INPCA和INPCB,输入端INPCA既可以与大信号直接匹配,又可直接与小信号相接。

自偏置电路可在放大器的线性区调整小信号电压增益。

鉴相器Ⅰ为异或门,鉴相器Ⅱ为四组边沿触发器。

由于CD4046的两个鉴相器输入信号均为数字信号,所以称CD4046位数字锁相环。

锁相环频率合成器原理锁相环频率合成器是一种广泛应用于无线通信系统和频率合成器中的电路。

它通过将输入信号的频率锁定到参考信号的频率上,实现对输入信号频率的稳定和精确控制。

锁相环频率合成器的原理是基于负反馈控制和锁相环电路。

锁相环频率合成器由三个主要组成部分组成:相位比较器、低通滤波器和电压控制振荡器。

首先,锁相环的参考信号和输入信号都被送入相位比较器。

相位比较器会将两个信号的相位进行比较,并输出相位差。

相位差是参考信号和输入信号之间相位的差异值。

接下来,相位差信号通过低通滤波器进行滤波,目的是消除高频噪声。

滤波器的作用是确保锁相环的输出信号是稳定的且没有抖动的。

经过滤波的相位差信号进入电压控制振荡器(VCO),VCO根据输入信号的相位差来调整自身的输出频率。

如果输入信号的频率低于参考信号的频率,那么相位差将是正值,VCO将增加输出频率。

如果输入信号的频率高于参考信号的频率,相位差将是负值,VCO将减小输出频率。

最后,VCO的输出信号通过反馈回路连接到相位比较器,与输入信号进行反馈。

这个反馈迫使VCO的输出频率与参考信号的频率越来越接近,最终达到精确的锁定。

锁相环频率合成器在无线通信系统中的应用非常广泛。

在接收方面,锁相环可以用于从复杂多路径传输的信号中恢复出原始信号,消除传播路径引起的相位偏差。

在发射方面,锁相环可以用于产生稳定的射频信号,通过倍频器和滤波器将原始频率倍增,然后放大后用于无线电通信。

此外,锁相环频率合成器还被广泛应用于频率合成器中,用于产生非常精确的时钟信号,以供数字电路和通信设备使用。

总结起来,锁相环频率合成器是一种将输入信号的频率锁定到参考信号的频率上的电路。

它通过相位比较、滤波和VCO调频的方式实现对输入信号频率的稳定和精确控制。

锁相环频率合成器在无线通信系统和频率合成器中有着广泛的应用,能够提供稳定的射频信号和精确的时钟信号,为无线通信技术的发展提供了重要支持。

集成电路课程设计一-锁相环CD4046设计频率合成器学号:110800316 姓名:苏毅坚指导老师:罗国新2011年1月锁相环CD4046设计频率合成器实验目的:设计一个基于锁相环CD4046设计频率合成器范围是10k〜100K,步进为1K设计和制作步骤:确定电路形式,画出电路图。

计算电路元件参数并选取元件O组装焊接电路。

调试并测量电路性能。

确定电路组成方案原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。

晶体振荡器输出的信号频率n,经固定分频后(M分频)得到基准频率fi,,输入锁相环的相位比较器(PC)。

锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:n/M=fF=f2/N 故f2=N『l (Fl为基准频率)当N变化时,就可以得到一系列的输出频率f2o设计方法(一)、振荡源的设计用CMOS与非门和1M晶体组成1MHz振荡器,如图14。

图中Rf使F1工作于线性放大区。

晶体的等效电感,Cl> C2构成谐振回路。

C1、C2可利用器件的分布电容不另接。

Fl、F2、F3 使用CD4049o(二)、N分频的设计N分频采用CD40103进行分频。

CD40103是BCD码8位分频器。

采用8位拨码开关控制分频大小。

输入的二进制大小即为分频器N分频。

图中RP1为1K排阻(三)、1KHZ标准信号源设计(即M分频的设计)根据4518的输出波形图,可以看出4518包含二分频、四分频、十分频,用二片CD4518 (共4个计数器)组成一个1000分频器,也就是三个十分频器,这样信号变为2Khz.再经过双D触发器,这样就可把2MHz的晶振信号变成500hz 的标准信号。

如下图所示:(四)4046锁相环的设计锁相环4046为主芯片。

电路图如下:500Hz信号从14脚输入。

3脚4脚接N分频电路,即40103分频电路。

1 引言在无线通信领域中,高性能频率源是通信设备、雷达、电子侦察和对抗设备、精密测量仪器的核心部件。

现代通信系统对频率源的精度、分辨率、转换时间及频谱纯度等提出了越来越高的要求,性能卓越的频率源均通过频率合成技术来实现。

本文所讨论的锁相环频率合成技术是基于锁相环路的同步原理,由一个高准确度、高稳定度的参考晶体振荡器,综合出大量离散频率的一种技术。

锁相环频率合成器是一种相位锁定装置,是一种频率稳定度较高的离散间隔型频率信号发生器。

2 锁相环频率合成器的基本原理锁相环是频率合成技术的基础。

锁相环路(PLL)通常由鉴相器(PD)、环路滤波器(LP)、压控振荡器(VCO)和可变程序分频器组成。

锁相环路是一个相位误差控制系统,它比较输入信号与压控振荡器输出信号之间的相位差,产生一个对应于两个信号相位差的误差电压,该误差电压经处理后去调整压控振荡器的频率(相位)。

当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时,误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等,即fo=fr。

锁相环路的这一特点,使它在自动频率控制中得到应用,以实现精确的频率控制。

环路在锁定时要得到一定的控制电压,则鉴相器必须有一个非零的输出,即,环路作用必须有相位差,相位差维持着两信号的同步,使输出信号频率稳定。

锁相环基本原理方框图如图1所示。

鉴相器又称比相器,对输入信号与环路输出信号的相位进行比较, 产生误差控制电压;环路滤波器滤除误差电压中的高频分量和噪声,以保证环路所要求的性能,增加环路的稳定性;压控振荡器的振荡频率受环路滤波器输出电压的控制,使压控振荡器输出信号频率向输入信号频率靠拢,两个信号间的相位差减小。

可变程序分频器的作用是使压控振荡器的输出频率经分频后再与参考频率进行相位比较,从而产生误差控制电压,并以误差控制电压来调整压控振荡器的相位。

锁相环路对高稳定度的参考振荡器(通常是晶体振荡器)锁定,环路串接可编程的程序分频器,通过编程改变程序分频器的分频比R、N,从而获得N/R倍参考频率的稳定输出。

由于文件过大,分上下俩部分,下载的朋友不要忘了-。

- 《数字频率合成器》设计报告设计时间:2013年1月5~17日班级:电子本0913班姓名:报告页数:22页摘要近几年来,无线通讯获得飞速发展。

随着其应用领域的不断扩张,市场对低功耗、低造价、高性能、高集成度的收发机的需要也越来越高。

在无线通信收发机中包含一个很重要的模块,频率合成器,它通过产生一系列与参考信号具有同样精度和稳定度的离散信号,为频率转换提供基准的本地震荡信号。

频率合成器设计的优劣直接影响到无线通信收发机的性能、成本,故其实现方式一直是一个挑战。

而本次课程设计仅考虑方案的实用性,即是实验室环境的局限性以及电子器件的价格等因素。

AbstractIn recent years, the rapid development wireless communications. With the continuous expansion of its applications, the market is also increasing the need for low-power, low-cost, high-performance , highly integrated transceiver.Contains a very important in the wireless communication transceiver module, the frequency synthesizer, and by generating a series of reference signals with the same accuracy and stability of the discrete signals provided for the frequency conversion of the local oscillation signal of the reference. Frequency synthesizer designed to directly affect the wireless communication transceiver performance, cost, and its implementation has been a challenge.Only to consider the practicality of the design of the course, that the limitations of the laboratory environment, as well as factors such as the price of electronic devices.目录一.设计任务与要求 1 二.设计方案及比较 2 三.系统设计总体思路 4 四.系统原理框图及工作原理分析 5 五.组成电路主要器件的参数,工作原理、外形图及选择10 六.电路原理图12 七.产品制作及调试15 八.实验结果与数据处理16 九.结论(设计与分析)18 十.心得体会19一.设计任务与要求(一)训练目的1. 熟悉锁相环路的原理和特点,掌握VCO压控振荡器的工作原理与作用2. 加深对基本锁相环工作原理的理解,巩固相关的理论知识3. 熟悉锁相环式数字频率合成器的电路组成与工作原理,培养设计、制作、调试电路等一系列工程设计的能力4. 熟悉相关IC的性能参数及使用方法。

培养应用理论知识为实际电路设计的能力(二)预习要求与参考、收集相关信息1. 认真预习有关锁相环及频率合成技术等方面的理论知识2. 参考《高频电子电路》、《通信原理与技术》、《集成电路大全》等书(三)设计要求和设计指标(1)设计指标a. 熟悉锁相环和频率合成器的基本结构原理,熟悉相关芯片的性能参数及使用方法b. 利用锁相环设计的频率合成器,当输入频率为100Hz时,用一片CD4046、三片MCI4522时,实现输出频率为100Hz ~ 99.9kHz(2)实验测试要求a. 测VCO曲线,即压控震荡器曲线b. 测VCO中心频率c. 求VCO增益:d. 测锁相环锁定范围:e. 求频率合成器的阶数1二.设计方案根据课题要求,为了能够实现锁相式数字频率合成,下面是我们找到的四种比较具有代表性的方案,结构框图分别见图1、图2、图3及图4:图1 方案一的系统框图(一)方案的比较与选择在上面的几种方案中,方案一、二和三均属硬件电路实现,其中方案一是最容易实现的,它完全能够实现步进频率为1KHz的频率合成,但其建立时间长,相位噪声和杂散信号的影响较明显。

方案二是一种DDS驱动PLL的频率合成器,方案三是一种单片机控制频率合成器,这两种方案在性能上要优于方案一,但它们都必须由单片机参与控制。

方案四与前三个方案在思想上有很大不同,是一种EDA设计,它是一种基于FPGA的、以VHDL硬件语言实现的嵌入式系统,其技术比较领先。

由于实验室为硬件电路工作环境,故不能选择方案四,在前三个方案中,虽然二、三在性能方面比较优越,但其需要借助计算机对其单片机进行控制,对我们提出编程要求我们无法实现。

方案一虽在性能方面略有不足,但其完全能够满足设计的需要,又能够适应实验室的工作环境。

综上所述,方案一能够满足设计的要求,我们组将采用方案一实现本系统。

(二)方案阐述与论证通过对各方案进行比较,我们组最终选择了方案一来实现该系统。

下面是我们组对方案一进行一个简单的阐述:在方案一中,系统是由锁相环路和N分频器以及信号输入电路构成的。

在锁相环路模块中,鉴相器(PD)和压控振荡器(VCO)可由集成芯片提供,以降低系统的复杂度。

鉴相器输出的相位误差电压是周期性脉冲波形,需要使用环路低通滤波器将它平滑后输出一个直流控制电压,去控制VCO的频率和相位,使之向减小误差方向变化,从而消除频差与相差达到锁定状态,而高频噪声及其它交流谐波分量将受到滤波器的抑制。

N分频器是将VCO输出信号经过N位可控计数器分频后输入鉴相器,使之与参考信号进行比较。

信号输入电路实质就是产生100Hz基准信号源,系统将在此信号的基础上进行一系列的频率合成。

信号源的精度和稳定度将影响整个系统频率合成的精度和稳定度。

•系统设计总体思路时钟输入可采用从信号源上的BS信号输入(频率为),经过锁相环电路(CD4046)及分频器个、十、百位控制电路(CD4522)即分频比为N,则从VCO振荡输出口得到合成频率为N信号。

CD4522为可预置可编程的二-十进制记数器。

N分频器是锁相式数字频率合成器主要单元电路之一。

当程序分频器的分频比N置成1,也就是把SW1断开,SW2置成“0001”状态,或者不接入两级程序分频器,即把压控振荡器VCO的输入端用导线直接连接到相位比较器2的比较信号输入端第三引脚PD12,这时,该电路就是一个基本锁相环电路。

本电路采用反馈封锁的办法,实现了使用极少的器件控制着众多批频率(即从100Hz~99.9KHz)的灵活转换功能。

分频比范围控制电路,主要通过改变电阻、电容的值来改变频率合成器分频比的范围。

四.系统原理框图及工作原理分析系统原理框图(一) 数字频率合成器的组成数字锁相式频率合成器根据信道间隔和工作频率可分为直接式频率合成器和吞脉冲式频率合成器。

典型的直接式频率合成器组成框图如上图所示。

它由参考振荡器、参考分频器、鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和可编程分频器等部分组成。

其中,(二)锁相环路的工作原理锁相环(PLL)是一个相位误差控制系统,利用反馈控制原理实现频率及相位的同步技术。

锁相环通过比较输入信号和压控振荡器输出频率之间的相位差,产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。

1.锁相环路的组成锁相环路的基本组成框图如下图所示。

它由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成。

其中,PD和LF构成反馈控制器,而VCO就是它的控制对象。

锁相环路的基本组成框图2.锁相环路的基本特性(1) 捕捉与锁定特性若锁相环路原本处于失锁状态,由于环路的调节作用,最终进入锁定状态,这一过程,称环路捕捉过程。

在没有干扰的情况下,环路一经锁定,其输出信号频率等于输入信号频率。

(2) 自动跟踪特性若环路原本处于锁定状态,由于温度或电源电压的变化,使VCO输出频率变化,或者输入信号频率变化,通过环路自动相位控制作用,使VCO相位(频率)不断跟踪输入信号的相位(频率),这个过程称跟踪过程,或同步过程。

(3) 锁相环路的捕捉带与同步带环路能捕捉的最大起始频差范围称捕捉带或捕捉范围,记作ΔfP。

环路所能跟踪的最大频率范围称同步带,记作ΔfH。

当 f0>fP时,环路将不能锁定。

当 f0>fH时,环路将不能跟踪。

一般有 fH>fP。

(三)常用集成锁相环路CD4046简介CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

CD4046引脚排列CD4046是带有RC型VCO的锁相环路,属于低频锁相环路。

采用16 脚双列直插式,图4-11为CD4046的内部功能框图和构成锁相频率合成器时的外围元件连接图。

从图中可以看出,CD4046主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

芯片内含有一个低功耗、高线性VCO,两个工作方式不同的鉴相器PDI和PDII,A1为PDI和PDII的公用输入基准信号放大器,源跟随器A2与VCO输入端相连是专门作FM解调输出之用的,此外还有一个6V左右的齐纳稳压管。

1.CD4046的内部功能框图及各引脚功能如下1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端CD4046内部结构图3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

2.鉴相器PDI:CD4046芯片内的鉴相器PDI是一个数字逻辑异或门,由于CMOS门输出电平在0~VDD之间变化。

所以只要用简单的积分电路就可以取出平均电平,因而使锁项环路的捕捉范围加大。

该鉴相器主要应用在调频波的解调电路中。

PDII是一个由边沿控制的数字比相器和互补CMOS输出结构组成的三态输出式鉴相器。

由于数字比相器仅在ui和uv的上跳边沿起作用,因而该鉴相器能接收任意占空比的输入脉冲,即非常窄的脉冲。