基于CPLD的正交解码器

- 格式:doc

- 大小:532.50 KB

- 文档页数:9

一种基于CPLD的曼彻斯特编解码器设计

虽然计算机通信的办法和手段多种多样,但都必需依赖数据通信技术。

数据通信就是将数据信号加到数据传输信道上举行传输,并在接收点将原始发送的数据正确地复原过来。

因为计算机产生的普通都是数字信号,因此计算机之间的通信事实上都属于数据通信。

曼彻斯特码编是1553B 接口中不行缺少的重要组成部分。

曼彻斯特码编解码器设计的好坏挺直影响总线接口的性能。

在数控测井系统和无线监控等领域,曼彻斯特码编解码器都有广泛应用。

1 数据通信系统结构

图1所示是数据通信系统的基本构成。

在计算机通信中,通信双方传递的信息必需举行量化并以某种形式举行编码后才干举行传输。

机内信号不论采纳哪一种编码办法,它们的基本信号都是脉冲信号,为了削减信号在传输媒质上的通信带宽限制,以及噪音、衰减、时延等影响,也因为同步技术的需要,操作时都需要对容易的脉冲信号举行一些不同的变换,以适合传输的需要。

这样就会产生许多不同的代码,通常有不归零电平(NRZ-L)码,逢“1”反转(NRZ-1)码,曼彻斯特码和差分曼彻斯特等。

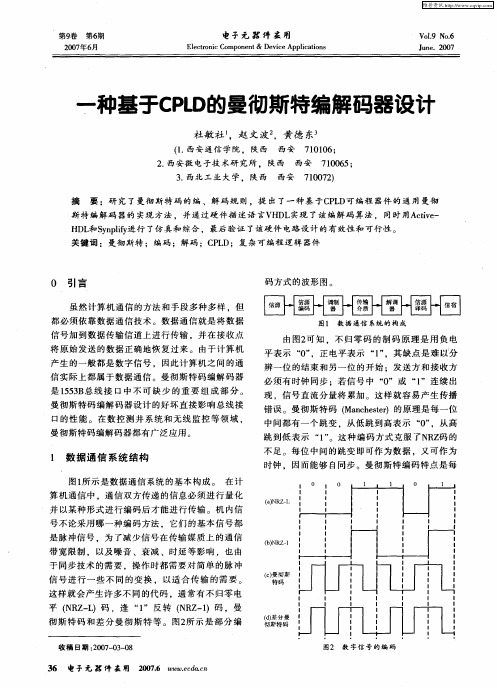

图2所示是部分编码方式的波形图。

由图2可知,不归零码的制码原理是用负电平表示“0”,正电平表示“1”,其缺点是难以辨别一位的结束和另一位的开头;发送方和接收方必需有时钟同步;若信号中“0”或“1”延续浮现,信号直流重量将累加。

这样就简单产生传扬错误。

曼彻斯特码(Manchester)的原理是每一位中间都有一个跳变,从低跳到高表示“0”,从高跳到低表示“1”。

这种编码方式克服了NRZ码的不足。

每位中间的跳变即可作为

第1页共5页。

基于CPLD的正交编码器解码系统设计

刘海成;贺亮

【期刊名称】《黑龙江工程学院学报(自然科学版)》

【年(卷),期】2013(027)002

【摘要】正交编码器广泛应用于运动测量及控制系统,在详述正交编码器角位移测量及编码工作原理基础上,设计正交编码器的X2和X4模式解码系统,并基于CPLD 通过Verilog HDL描述实现解码逻辑.实际测试应用表明,该系统精度高、纯硬件抗干扰能力强、接口方便、占用逻辑宏资源少,具有较高的实用价值.

【总页数】4页(P57-60)

【作者】刘海成;贺亮

【作者单位】黑龙江工程学院电气与信息工程学院,黑龙江哈尔滨 150050;黑龙江工程学院电气与信息工程学院,黑龙江哈尔滨 150050

【正文语种】中文

【中图分类】TM938.81

【相关文献】

1.高性能伺服系统编码器解码系统设计与实现 [J], 潘鑫;黄庆;黄守道;王家堡;陈正茂

2.基于CPLD和VS1011E解码器的电梯语音系统设计 [J], 郭稳涛;何怡刚;廖学坤

3.基于Multisim 12的正交编码器与解码器的电路设计与仿真 [J], 王玲;陈远超

4.基于FPGA的电子编码器解码系统设计 [J], 张建红;杨冬梅;薛红平;卢军平;黄伟林

5.基于CPLD的增量式调焦编码器读出电路的设计 [J], 雷增强;许辉勇;程刚;沈良吉;陈志学

因版权原因,仅展示原文概要,查看原文内容请购买。

基于CPLD的伺服系统正交脉冲的分数分频夏奇【摘要】在交流伺服系统中,对电机编码器反馈的正交脉冲信号进行分频,并发送至上位机对构成全闭环系统非常必要.为了能够实现对编码器正交脉冲信号的分数分频,并保证分频得到的脉冲方向正确,数量符合要求,仍以正交形式反馈给上位机,本文研究了伺服系统中分数分频的基本原理及分频过程,采用Altera公司的QUARTUS Ⅱ软件和CPLD产品EPM1270进行设计,通过软件仿真和实验测试,证明分频器在伺服系统中应用的可行性,有较强的工程应用价值.【期刊名称】《电子设计工程》【年(卷),期】2014(022)024【总页数】4页(P45-47,51)【关键词】伺服系统;正交脉冲;分数分频;CPLD【作者】夏奇【作者单位】同济大学电信学院,上海200092【正文语种】中文【中图分类】TN786在交流伺服系统的使用过程中,需要将电机编码器上的正交脉冲信号反馈给上位机,以实现对电机的监控,达到闭环控制的目的。

一旦伺服电机的运行发生错误,上位机能够发出指令,让电机停止运转,避免造成大的损失。

但是在编码器脉冲信号的反馈过程中,如果脉冲的频率过高,可能会导致脉冲信号无法接收,或者在传输过程中丢失,因此需要对编码器的脉冲信号进行分频[1]。

正交脉冲信号的分频与一般的信号分频不同,正交脉冲信号包括A相和B相两个信号,通过两个信号的相对位置来表示脉冲信号的方向。

在分频过程中必须考虑正交脉冲的方向,不能简单地通过对两个信号的分频达到对正交信号分频的目的。

特别是在脉冲方向切换的时候,孤立对待A相和B相信号的分频方法,极易导致脉冲信号的丢失。

整数分频的方法比较简单,只需要通过一些数字电路的搭建,就可以实现。

但是编码器反馈正交脉冲信号的频率与上位机所需要的脉冲频率往往不成整数倍关系,这两者的比例通常是一个不可整除的分数。

这时简单的几个数字器件的组合,无法满足分频设计的需要。

采用CPLD器件实现分频功能,不但电路体积大大缩小,而且可靠性大大提高了[2]。

用CPLD控制曼彻斯特编解码器摘要讨论如何使用实现单片机与曼彻斯特编解码器的接口。

设计时采用自顶向下的流程,具体电路可灵活地添加到各种曼彻斯特码接口系统中。

关键词曼彻斯特编解码器2模式5模式引言在油田测井中,井下仪在井下采集大量信息,并传送给地面测井系统;但井下仪到地面这段信道的传输性能并不好,常用的码不适合在这样的信道里传输,而且码含有丰富的直流分量,容易引起滚筒的磁化,因而选用了另外一种编码——曼彻斯特码。

曼彻斯特编码是串行数据传输的一种重要的编码方式。

和最常用的码相比,曼彻斯特码具有很多优点。

例如,消除了码的直流成分,具有时钟恢复和更好的抗干扰性能,这使它更适合于信道传输。

但曼彻斯特码的时序比较复杂,实现编解码器和单片机的接口需要添加大量的逻辑电路,给电路设计和调试带来很多困难。

使用可大大简化这一过程。

具有用户可编程、时序可预测、速度高和容易使用等优点,这几年得到了飞速发展和广泛应用。

上至高性能,下至简单的74电路,都可以用来实现。

而且的可编程性,使修改和产品升级变得十分方便。

用户可以根据原理图或硬件描述语言自由地设计一个数字系统,然后通过软件仿真,事先验证设计的正确性。

完成以后,还可以利用的在线修改能力,随时修改设计而不必改动硬件电路,从而大大缩短了设计和调试时间,减少了面积,提高了系统的可靠性。

1选用器件和开发软件11选用器件范文先生网收集整理195144公司的9500系列产品具有业界领先的速度,同时,具有增强引脚锁定结构和支持全面的11491边界扫描,向用户提供了更高的灵活性。

9500体系由多个同一功能块组成,每个功能块内含18个宏单元,引脚到引脚速度最快支持到5;支持125时钟速率,口接口电平5、33或两者皆可。

其中95144内部有144个宏单元。

2-6408和-6409-6408和-6409是公司的产品,两者均是曼彻斯特编解码器。

-6408编码器转换串行数据通常来自移位寄存器为曼彻斯特编码,增加一个同步头和一个奇偶位。

基于CPLD的正交磁通门传感器设计马乐【摘要】简述了磁通门传感器技术中二次谐波法的原理,用软磁材料坡莫合金制作传感器探头磁芯,设计了基于CPLD的正交磁通门传感器。

传感器能够实现水平载体的航向角数值,在0毅~360毅范围内航向角的测量精度可达1毅,系统分辨率可达0.1毅,可以满足水平定向导航的性能要求。

% This paper describes the principle of the fluxgate sensor technology second harmonic law, Mo alloy soft magnetic materials slope sensor probe core design of orthogonal fluxgate sensor based on CPLD. The Sensor is able to achieve the level of carrier heading angle value within the range of 0ºto360ºheading angle measurement accuracy of up to up to 0.1º resolution system, meeting the performance requirements of horizontal directional navigation.【期刊名称】《价值工程》【年(卷),期】2013(000)017【总页数】2页(P37-38)【关键词】CPLD;正交磁通门传感器;水平定向导航【作者】马乐【作者单位】哈尔滨工程大学理学院,哈尔滨150001【正文语种】中文【中图分类】TP2120 引言磁通门传感器是一种利用磁饱和法测量弱磁场的传感器,广泛应用于地磁测量、空间磁场测量、飞行器控制等[1]。

以往的磁通门传感器电路复杂,分立元件使用量大,这使得电路参数受温度影响较大且调试困难。

基于CPLD的正交解码器/计数器接口芯片电机控制设计蔡明发陈庞明新科技大学新中兴路Hsinfeng,新竹,台湾, R. O. C.摘要--在本文中我们提出了一个采用Altera FLEX lOKA CPLD的正交解码器/计数器接口芯片(ASIC)的设计,在数字运动控制系统中执行解码、计算和总线接口函数。

该ASIC包含一对数字过滤器、正交译码器,一个向上/向下计数器,一个门闩和抑制电路,一个8位数字处理系统总线接口。

数字滤波器的设计是基于有限状态机模型与数据路径(FSMD)。

用于检测电机转动方向的新方案也被提出。

该ASIC可以应用到数字电机控制系统获取的旋转速度或马达,其配备了一个光学编码器的位置。

数据采集可以由两个连续读取周期扩展到16比特整数格式。

仿真和实验测试显示验证ASIC功能正常。

关键词:电机控制,解码器/计数器接口芯片,CPLD一、引言在宽调速范围的高性能数字电机控制系统,某些接口集成电路(IC),通过它仍需要得到电机反馈的位置或速度的信号,虽然无传感器控制得到了越来越多的关注。

有许多类型的电机的传感器,例如转速计,电位计,旋转变压器和光学编码器,用于获取电机的旋转角度或转速。

其中,光学式编码器是最常用的,因为它的输出信号是数字式的高抗干扰性和高的分辨率。

有三种类型的光学编码器的运动控制常用。

他们是顺时针/逆时针(CW / CCW),脉冲,方向(脉冲/方向),以及正交A/ B相。

其中,最后一个是最流行的,因为它可以产生4分辨速率。

在过去的二十年中,大多数的数字电机控制是通过使用微处理器[2]完成的,如图1所示。

一些接口集成电路,如惠普HCTL2000 HCTL2016,正交解码和计算光学编码器的输出信号也可以在商业市场。

然而,整个控制系统的建设是复杂的,成本并不便宜。

近来,在超大规模集成电路技术的进步使得有可能对数字控制器,接口IC,或其他应用程序特定的集成电路(ASIC)的设计采用复杂可编程逻辑器件(CPLD)或现场可编程门阵列(FPGA)中相同的芯片。

虽然正交解码器/计数器接口芯片在文学的设计并不缺乏,但这项工作是在晶体管级进行。

在本文中,我们提出了接口IC在门的设计和寄存器级别,采用Altera公司的FLEX10KA CLPD设备。

通过该计划,本电路的实现比以前更轻松。

接口IC可以执行过滤,正交解码,位置计数,总线接口功能。

仿真和实验测试,验证了本接口芯片的正常工作。

该电路可以被集成为应用程序特定的数字控制IC用于运动控制的电路的一部分。

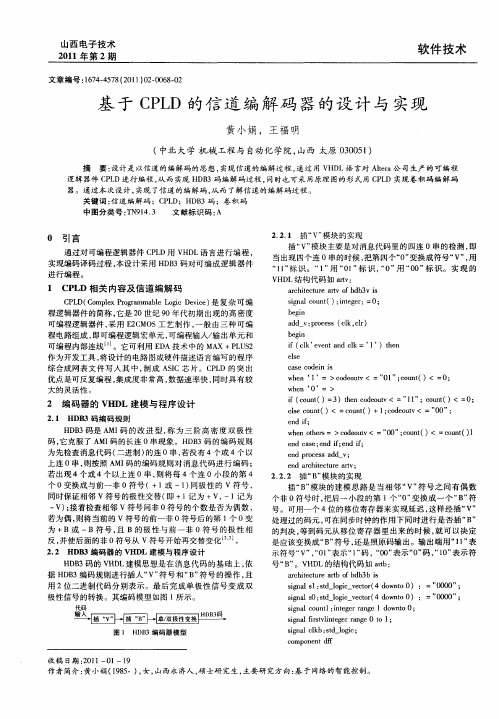

图1、基于微处理器的电机控制系统二、所需的功能图2显示了系统功能框图的接口集成电路,具有两相界面的光学编码器和一个8位接口标准微处理器或特定于应用程序的数字系统。

接口IC所要求的功能的描述如下。

由于许多电机通常工作在嘈杂的环境中,由于电磁耦合或振动,这可能会引入编码器的输出不必要的噪音。

A.一对数字滤波器,一个用于通道A,而另一个用于信道B,都需要过滤掉的输入信号中的噪声。

正交解码器电路也需要解码传入滤波的信号来确定电机的转动方向和由四个因素乘以输入信号的分辨率。

一种位置计数器,然后根据需要来向上或向下计数,根据从解码器输出中的一个的旋转方向指示所得到的译码的脉冲。

图2、接口IC的系统功能块图3、数字滤波器的电路架构脉冲数被统计后,系统可以通过两种方式利用计数器。

首先,使用16位的锁存器抑制逻辑芯片上允许访问与8位总线16位计数。

其次,当一定要8位计数时,一个简单的8位模式可通过禁用抑制逻辑。

芯片上的禁止逻辑抑制从计数器的时间间隔内数据的传送到数据锁存器的位置,该锁存输出被读取。

抑制逻辑允许微处理器或数字系统首先读取从锁存器高字节,然后读低位字节构成锁存。

同时,计数器可以继续跟踪从信道A和信道B的输入信号的正交解码器状态。

在下文中,只对数字滤波器,正交解码器和抑制逻辑设计进行叙述。

位置计数器和锁存电路,这是很常见的,这里不再叙述。

三、本接口IC的设计A、数字滤波器数字滤波器是基于数据路径的有限状态机模型(FSMD)的设计。

图3示出了数字滤波器,它由一个2:1多路复用器和一个D触发器构成,由一个识别器来检查控制单元的电路结构,如果从光学编码器的输入具有短持续时间的脉冲,然后控制所述输入数据流通过数据路径。

如果输入电平有至少三个连续的时钟周期相同的值(1或0),则输入不被认为是一个噪声。

在这种情况下,识别器的输出为高电平,然后允许输入数据流通过数据通路。

数据值成为过滤器新的输出,否则将被认为是过滤器的噪声输入和数据通路的输出保持不变。

我们假定控制单元的设计遵循有限状态机(FSM)模型,包括一个下一状态逻辑,状态寄存器,以及输出逻辑。

该模型的结构开始于一个状态图和/或下一状态和输出的表的生成。

图4(a)所示,其中包含七个优化的状态,每个状态都有不同的下一个状态或输出每个输入识别器的状态图。

用适当的状态编码的相应下一状态/输出表如图4(b)。

完成状态最小化和状态编码的过程之后,我们就可以选择有限状态机模型执行适当类型的触发器。

因为D触发器需要较少的连接,它们被选择为我们的设计。

通过使用D触发器充当了状态寄存器激发表,激励和输出方程,如图4(c)所示。

数字滤波器电路和模拟结果示于图。

分别为图5(a)和(b)。

如从图中可以看出。

5(b)所示,对输入信号(x)的短持续时间的噪声消耗3个时钟的延迟为代价输出(dfout)。

图4、数字滤波器的识别器的设计:(a)状态图,(b)下一状态1输出表,(c)激发表,激励和输出方程图5、(a)该数字滤波电路,(b)仿真结果图6、该方案确定的旋转方向B、正交解码器正交解码器部分包括一个方向译码器和一个4-时间变化率的电路。

它的样品在两个正交信号的数字滤波器的输出,并观察这些输出在时钟的上升沿变化。

两个正交信号可以被编码为四个状态。

状态变化可以通过以前的采样状态比较当前采样状态进行检测。

这频率可以依次通过四个因素乘以输入信号得到。

用于检测电动机的旋转方向的新方法示于图6。

可以看出,8,14,07和1中的顺时针方向上的编码状态不同于2,11,13,和4的状态。

因此,我们可以使用一个4到16多路分解器和一些输出逻辑来检测方向。

计数方向(向上或向下)也可以通过观察过去和当前的状态决定。

设计电路示于图7的底部。

图7的上半部分示出了4-时间变化率电路的设计,它的输出是要取到一个向上/向下位置计数器。

Ç、抑制逻辑抑制逻辑部分样品的OE和SE在时钟的下降沿的微处理器或数字系统中读命令信号和抑制位置数据锁存器,以避免在两个字节的读周期被更新为16锁存的数据位数据的访问。

图7、正交解码器和四时间率电路图8、(a)状态图,(b)下一个状态/输出表,(c)激发表和激励方程:抑制逻辑的设计抑制逻辑的设计也遵循上文所述的有限状态机模型。

状态图和下一个状态/输出表分别如图8(a)和(b)所示。

可以看出,有三个最小的状态和仅两个触发器都需要对模型的实现。

同样,我们用D触发器作为由于它的简单状态寄存器。

激发表和方程式的输入逻辑示于图8(C)。

输出是一样的作为第二触发器的输出状态。

四、模拟与试验研究通过使用Altera的MAX PLUS II开发的软件工具绘制接口IO集成电路的总体电路示于图9。

在这个工具中提供的波形仿真验证了每个电路符号的对应数字。

整体仿真结果来测试接口的IC的功能被显示在图10,通过给两个正交输入信号(CHA和CHB)和一个时钟信号的频率比输入正交信号高得多。

可以看出,4 - 时间变化率信号(4xff),其频率是与输入脉冲的成功生成另外四次,方向信号(DIR)是低电平,如果相位的信号被领先B相信号和积极的高,如果相位的信号滞后于B相的信号。

位置向上/向下计数器向上计数从0到9,而DIR信号为低电平,然后向下计数到0,而DIR信号为高电平有效。

位置数据锁存器输出(锁存)保持在6当OE/信号为低电平有效的16位数据的访问。

同时抑制逻辑输出信号(inh)为高电平并保持高电平,直到低字节数据已被读出的第二个读周期。

仿真结果表明,正交解码器/计数器接口芯片的功能是正确的。

图9、正交解码器/计数器接口芯片的整体电路图10、正交解码器/计数器接口芯片的仿真结果设计电路已经由本实验系统进一步测试,如图11所示。

电机光电编码器可以产生两个正交A/ B相的信号与2000脉冲每转的速度。

在个人电脑的测试程序已被设计为读锁存接口IC的计数。

用于解码和计数脉冲,我们在大约每五秒钟手动旋转电机轴。

在时间间隔,我们可以看到在PC显示器上的锁定计数显示清晰。

在顺时针方向旋转1周,将有8000个脉冲被计数,然后在十六进制数据格式下显示数量是1F40。

表I总结对应于旋转周期的顺时针和反时针方向,分别计数数。

该结果也验证了正交解码器/计数器接口芯片的正常工作。

图11、该实验系统,用于测试接口集成电路表1、电机的旋转周期和相应的计数五、结论本文提出了一种正交解码器/计数器接口芯片的设计,并使用Altera公司的FLEX 10KA级别设备寄存器。

使用CPLD器件的电路实现比晶体管级做以前的工作更轻松。

仿真和实验测试显示正确验证的ASIC功能。

接口IC可以作为一个接口,一个基于微处理器的电动机控制系统被应用。

它也可以集成为一个应用程序特定的数字控制IC,用于运动控制的电路的一部分。