两级开环比较器地设计

- 格式:doc

- 大小:2.84 MB

- 文档页数:27

运放的开环闭环运放的开环闭环是电子电路中常见的概念。

运放(Operational Amplifier)是一种高增益、差分输入、差模输出的电子器件,广泛应用于模拟电路和信号处理领域。

它可以实现信号放大、滤波、积分、微分等功能,是许多电路设计中重要的基础元件。

一、运放的基本结构和特性运放通常由一个差分输入级和一个差模输出级组成。

差分输入级包含两个输入端和一个差分放大器,用于将输入信号转换为差分信号。

差模输出级包含一个输出端和一个输出级,用于将差分信号转换为单端输出信号。

运放具有以下特性:1. 高增益:运放的开环增益非常高,通常在几万到几百万倍之间。

2. 大输入阻抗:运放的输入端具有很高的阻抗,可以减小外部电路对输入信号的影响。

3. 小输出阻抗:运放的输出端具有很小的阻抗,可以提供较大的输出功率。

4. 宽带宽:运放具有较宽的频带宽度,能够处理高频信号。

5. 高共模抑制比:运放可以有效抑制共模信号的干扰。

二、运放的开环和闭环1. 开环运放:当运放的输出端未连接到反馈回路时,称为开环运放。

开环运放的特点是增益非常高,但稳定性较差,容易受到噪声和温度变化的影响。

在实际应用中,很少直接使用开环运放。

2. 闭环运放:当运放的输出端连接到反馈回路时,称为闭环运放。

闭环运放通过反馈回路将一部分输出信号送回输入端,使得输出信号与输入信号之间存在负反馈关系。

闭环运放的特点是增益稳定、精确可控,能够提供稳定且精确的放大功能。

三、运放的反馈类型根据反馈回路的连接方式,可以将运放的反馈分为正反馈和负反馈两种类型。

1. 正反馈:正反馈是指将一部分输出信号直接或间接地送回到输入端,使得输出信号与输入信号之间存在正相关关系。

正反馈会增强系统的不稳定性,容易产生自激振荡等问题,在实际应用中很少使用。

2. 负反馈:负反馈是指将一部分输出信号送回到输入端,并与输入信号相减,使得输出信号与输入信号之间存在负相关关系。

负反馈能够提高系统的稳定性、减小非线性失真、扩大带宽等。

模拟比较器:将模拟量与一标准值进行比较,当高于该值时,输出高(或低)电平.反之,则输出低(或高)电平.例如,将一温度信号接于运放的同相端,反相端接一电压基准(代表某一温度),当温度高于基准值时,运放输出高电平,控制加热器关闭,反之当温度信号低于基准值时,运放输出低电平,将加热器接通.这一运放就是一个简单的比较器,因为输入与输出同相,称为同相比较器..有的模拟比较器具有迟滞回线,称为迟滞比较器,用这种比较器,有助于消除寄生在信号上的干扰.数字比较器:用来比较二组二进制数是否相同,相同时输出(或低)高电平,反之,则输出相反的电平.最简单的数字比较器是一位二进制数比较器,是一个异或门(或同或门).电压比较器的作用:它可用作模拟电路和数字电路的接口,还可以用作波形产生和变换电路等。

利用简单电压比较器可将正弦波变为同频率的方波或矩形波电压比较器是集成运放非线性应用电路,他常用于各种电子设备中,那么什么是电压比较器呢?下面我给大家介绍一下,它将一个模拟量电压信号和一个参考固定电压相比较,在二者幅度相等的附近,输出电压将产生跃变,相应输出高电平或低电平。

常用的电压比较器有过零电压比较器、具有滞回特性的过零比较器、滞回电压比较器,窗口(双限)电压比较器.1.模拟比较器将模拟量与一标准值进行比较,当高于该值时,输出高(或低)电平.反之,则输出低(或高)电平.例如,将一温度信号接于运放的同相端,反相端接一电压基准(代表某一温度),当温度高于基准值时,运放输出高电平,控制加热器关闭,反之当温度信号低于基准值时,运放输出低电平,将加热器接通.这一运放就是一个简单的比较器,因为输入与输出同相,称为同相比较器..有的模拟比较器具有迟滞回线,称为迟滞比较器,用这种比较器,有助于消除寄生在信号上的干扰.2.数字比较器用来比较二组二进制数是否相同,相同时输出(或低)高电平,反之,则输出相反的电平.最简单的数字比较器是一位二进制数比较器,是一个异或门(或同或门).电压比较器可以看作是放大倍数接近“无穷大”的运算放大器。

CMOS二级运算放大器设计(东南大学集成电路学院)一.运算放大器归纳运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常有的电路,在某种程度上,可以把它看作一个近似于BJT或FET的电子器件。

它是好多模拟系统和混杂信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、成马上间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标1.电路结构最基本的COMS二级密勒补偿运算跨导放大器的结构如图所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

图两级运放电路图2.电路描述电路由两级放大器组成,M1~M4组成有源负载的差分放大器, M5供给该放大器的工作电流。

M6、M7管组成共源放大电路,作为运放的输出级。

M6供给给M7M8~M13组成的偏置电路,供给整个放大器的工作电流。

相位补偿电路由的工作电流。

M14和Cc构成。

M14Cc一起跨接在第二级输入输出之间,工作在线性区,可等效为一个电阻,与电容组成RC密勒补偿。

3.设计指标两级运放的相关设计指标如表1。

电源电压0~5V共模输入电压固定在(VDD+VSS)/2 开环直流增益≥80dB单位增益带宽≥30MHz相位裕度≥60degree变换速率≥30V/μs静态功耗(电流)≤1mA负载电容=3pf表1两级运放设计指标三.电路设计第一级的电压增益:A1G m1R1g m2(r o2||r o4)第二级电压增益:A2G m2R2g m6(r o6||r o7)所以直流开环电压增益:A o A1A2 g m2g m6(r o2||r o4)(r o6||r o7)单位增益带宽:gm1GBW A O f d2C c偏置电流:22(W/L)121I B(W/L)13KP n(W/L)12R B2依照系统失调电压:变换速率:(3.1)(3.2) (3.3) (3.4)(3.5)(3.6)(3.7) 相位补偿:(W/L )6(W/L)11gm61(3.8)RC gm6(W/L)13g m1(W/L )14以上公式推导过程简单,详尽过程可参照相关专业书籍。

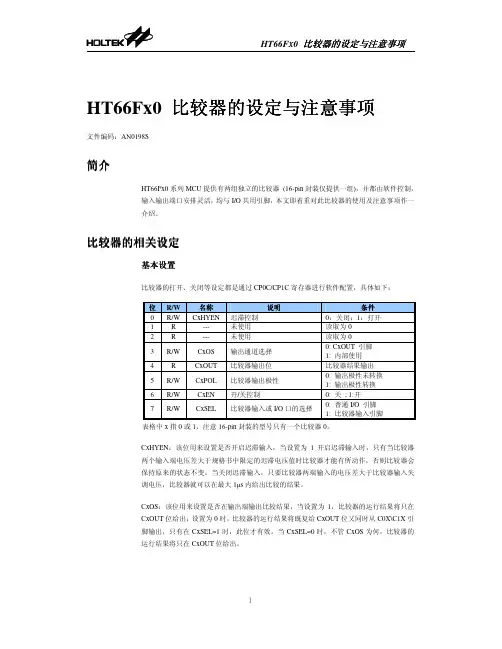

HT66Fx0 比较器比较器的设定与注意事项的设定与注意事项文件编码:A N0198S简介HT66Fx0系列MCU提供有两组独立的比较器(16-pin封装仅提供一组),并都由软件控制,输入输出端口安排灵活,均与I/O共用引脚,本文即着重对此比较器的使用及注意事项作一介绍。

比较器比较器的相关设定的相关设定基本设置比较器的打开、关闭等设定都是通过CP0C/CP1C寄存器进行软件配置,具体如下:位R/W名称说明条件0R/W CxHYEN迟滞控制0:关闭;1:打开1R --- 未使用读取为02R --- 未使用读取为03R/W CxOS 输出通道选择0: CxOUT 引脚1: 内部使用4R CxOUT 比较器输出位比较器结果输出5R/W CxPOL 比较器输出极性0: 输出极性未转换1: 输出极性转换6R/W CxEN 开/关控制0: 关; 1:开7R/W CxSEL 比较器输入或I/O口的选择0: 普通I/O 引脚1: 比较器输入引脚表格中x指0或1,注意16-pin封装的型号只有一个比较器0。

CxHYEN:该位用来设置是否开启迟滞输入,当设置为1开启迟滞输入时,只有当比较器两个输入端电压差大于规格书中限定的迟滞电压值时比较器才能有所动作,否则比较器会保持原来的状态不变。

当关闭迟滞输入,只要比较器两端输入的电压差大于比较器输入失调电压,比较器就可以在最大1µs内给出比较的结果。

CxOS:该位用来设置是否在输出端输出比较结果,当设置为1,比较器的运行结果将只在CxOUT位给出;设置为0时,比较器的运行结果将既复给CxOUT位又同时从C0X\C1X引脚输出,只有在CxSEL=1时,此位才有效。

当CxSEL=0时,不管CxOS为何,比较器的运行结果将只在CxOUT位给出。

CxOUT :该位输出比较器的比较结果,其具体结果需要参考CxPOL 的极性选择。

CxPOL :该位用来设置比较器输出的极性,具体如下表:CxPOL Inputs CxOUT Cx+ < Cx- 0 0 Cx+ > Cx- 1 Cx+ > Cx- 0 1Cx+ < Cx-1CxEN :该位用来设置比较器的打开和关闭,1为打开,0为关闭。

电压比较器(以下简称比较器)是一种常用的集成电路。

它可用于报警器电路、自动控制电路、测量技术,也可用于V/F变换电路、A/D变换电路、高速采样电路、电源电压监测电路、振荡器及压控振荡器电路、过零检测电路等。

本文主要介绍其基本概念、工作原理及典型工作电路,并介绍一些常用的电压比较器。

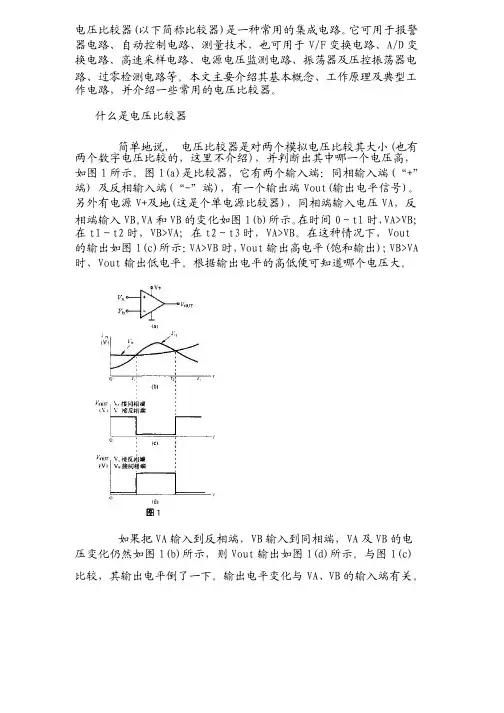

什么是电压比较器简单地说,电压比较器是对两个模拟电压比较其大小(也有两个数字电压比较的,这里不介绍),并判断出其中哪一个电压高,如图1所示。

图1(a)是比较器,它有两个输入端:同相输入端(“+”端) 及反相输入端(“-”端),有一个输出端Vout(输出电平信号)。

另外有电源V+及地(这是个单电源比较器),同相端输入电压VA,反相端输入VB。

VA和VB的变化如图1(b)所示。

在时间0~t1时,VA>VB;在t1~t2时,VB>VA;在t2~t3时,VA>VB。

在这种情况下,Vout的输出如图1(c)所示:VA>VB时,Vout输出高电平(饱和输出);VB>VA 时,Vout输出低电平。

根据输出电平的高低便可知道哪个电压大。

如果把VA输入到反相端,VB输入到同相端,VA及VB的电压变化仍然如图1(b)所示,则Vout输出如图1(d)所示。

与图1(c)比较,其输出电平倒了一下。

输出电平变化与VA、VB的输入端有关。

图2(a)是双电源(正负电源)供电的比较器。

如果它的VA、VB输入电压如图1(b)那样,它的输出特性如图2(b)所示。

VB>VA时,Vout输出饱和负电压。

如果输入电压VA与某一个固定不变的电压VB相比较,如图3(a)所示。

此VB称为参考电压、基准电压或阈值电压。

如果这参考电压是0V(地电平),如图3(b)所示,它一般用作过零检测。

比较器的工作原理比较器是由运算放大器发展而来的,比较器电路可以看作是所以开运算放大器的一种应用电路。

由于比较器电路应用较为广泛,由于比较器电路应用较为广泛,所以开发出了专门的比较器集成电路。

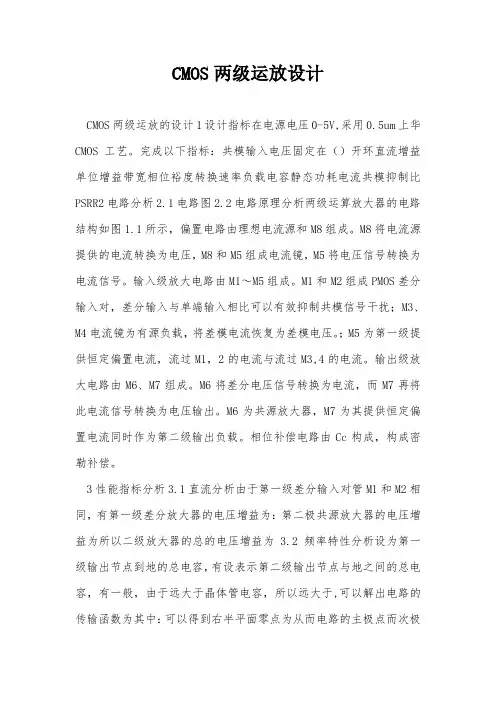

CMOS两级运放设计CMOS两级运放的设计1设计指标在电源电压0-5V,采用0.5um上华CMOS工艺。

完成以下指标:共模输入电压固定在()开环直流增益单位增益带宽相位裕度转换速率负载电容静态功耗电流共模抑制比PSRR2电路分析2.1电路图2.2电路原理分析两级运算放大器的电路结构如图1.1所示,偏置电路由理想电流源和M8组成。

M8将电流源提供的电流转换为电压,M8和M5组成电流镜,M5将电压信号转换为电流信号。

输入级放大电路由M1~M5组成。

M1和M2组成PMOS差分输入对,差分输入与单端输入相比可以有效抑制共模信号干扰;M3、M4电流镜为有源负载,将差模电流恢复为差模电压。

;M5为第一级提供恒定偏置电流,流过M1,2的电流与流过M3,4的电流。

输出级放大电路由M6、M7组成。

M6将差分电压信号转换为电流,而M7再将此电流信号转换为电压输出。

M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

相位补偿电路由Cc构成,构成密勒补偿。

3性能指标分析3.1直流分析由于第一级差分输入对管M1和M2相同,有第一级差分放大器的电压增益为:第二极共源放大器的电压增益为所以二级放大器的总的电压增益为 3.2频率特性分析设为第一级输出节点到地的总电容,有设表示第二级输出节点与地之间的总电容,有一般,由于远大于晶体管电容,所以远大于,可以解出电路的传输函数为其中:可以得到右半平面零点为从而电路的主极点而次极点由于和远大于,而中最主要的部分为,中则以为主,经过适当近似,可以得到单位增益带宽为 3.3共模抑制比分析如果运放有差分输入和单端输出,小信号输出电压可以描述为差分和共模输入电压的方程其中是差模增益,有,是共模增益。

共模抑制比的定义为从应用角度考虑可以理解为“每单位共模输入电压的变化引起的输入失调电压的变化”。

对于两级运放电路的共模抑制比,有其中,是第一级的共模抑制比,因为第二级是单端输入、单端输出,所以不贡献共模抑制比。

CMOS二级运算放大器设计(东南大学集成电路学院)一.运算放大器概述运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标1.电路结构最基本的COMS二级密勒补偿运算跨导放大器的结构如图1.1所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

图1.1 两级运放电路图2.电路描述电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。

M6、M7管构成共源放大电路,作为运放的输出级。

M6 提供给M7 的工作电流。

M8~M13组成的偏置电路,提供整个放大器的工作电流。

相位补偿电路由M14和Cc构成。

M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3.设计指标两级运放的相关设计指标如表1。

电源电压0~5V共模输入电压固定在(VDD+VSS)/2开环直流增益≥80dB单位增益带宽≥30MHz相位裕度 ≥60degree 转换速率 ≥30 V/μs 静态功耗(电流)≤1mA 负载电容=3pf表1 两级运放设计指标三.电路设计第一级的电压增益:)||(422111o o m m r r g R G A == (3.1) 第二级电压增益:)||(766222o o m m r r g R G A =-= (3.2) 所以直流开环电压增益:)||)(||(76426221o o o o m m o r r r r g g A A A -== (3.3) 单位增益带宽:cm O C g A G B W π2f 1d == (3.4) 偏置电流:213122121)/()/()/(2⎪⎪⎭⎫ ⎝⎛-=L W L W R L W KP I Bn B (3.5) 根据系统失调电压:756463)/()/(21)/()/()/()/(L W L W L W L W L W L W == (3.6)转换速率:⎭⎬⎫⎩⎨⎧-=L DS DS C DS C I I C I SR 575,min (3.7) 相位补偿:12.1)/()/()/()/(1613111466+==m m m C g g L W L W L W L W g R (3.8)以上公式推导过程简略,具体过程可参考相关专业书籍。

电路中的比较器设计与分析在电子电路设计中,比较器是一种常用的电路元件,用于比较输入信号,并产生输出信号以表示两个信号的关系。

比较器广泛应用于模拟电路和数字电路中,具有很高的实用性。

本文将介绍比较器的设计原理和分析方法,为读者提供一些有关电路中比较器的设计与分析的基本知识和技巧。

一、比较器的基本原理和分类比较器是一种电子设备,它的输入有两个或多个信号,而输出则是一个用于表示输入信号关系的二进制位。

比较器的基本原理是将两个输入信号进行比较,并产生相应的输出信号。

根据输入信号的类型和输出信号的形式,比较器可以分为模拟比较器和数字比较器两种类型。

1. 模拟比较器:模拟比较器适用于将输入电压信号进行比较,并产生相应的模拟输出信号。

模拟比较器的输出信号通常是一个连续变化的模拟电压信号,可以用于模拟电路中的各种应用,如比较两个模拟信号的大小、判断输入信号的高低电平等。

2. 数字比较器:数字比较器适用于将输入信号进行数字比较,并产生相应的数字输出信号。

数字比较器的输出信号通常是一个二进制位,用于表示两个或多个输入信号的大小关系。

数字比较器主要应用于数字电路或微处理器系统中,用于实现逻辑比较、数据排序和状态判断等功能。

二、模拟比较器的设计与分析模拟比较器是电路中常见的一种元件,用于对输入电压进行比较,并产生相应的输出电压。

常见的模拟比较器电路包括基本比较器、窗限比较器和振荡比较器等。

下面分别介绍这三种常见的模拟比较器电路的设计与分析。

1. 基本比较器:基本比较器是一种最简单的比较器电路,由一个比较元件和电压供应电源组成。

比较元件通常是根据输入电压产生不同输出电压的二极管或晶体管。

基本比较器的设计原理是根据输入电压与参考电压之间的关系,产生相应的输出电压。

2. 窗限比较器:窗限比较器是一种能够对输入电压进行范围限制的比较器电路。

窗限比较器通常由两个比较元件和两个参考电压组成,用于判断输入信号是否在指定的范围内。

窗限比较器的设计原理是通过比较输入电压与两个参考电压之间的关系,判断输入信号是否在指定的范围内,并产生相应的输出信号。

电压比较器VIO的开环测试方案

输入失调电压(VIO)是电压比较器(以下简称比较器)一个重要的电性能参数,GB/T 6798-1996中,将其定义为“使输出电压为规定值时,两输入端间所加的直流补偿电压”。

传统测试设备大都采用“被测器件(DUT,Device Under Test)-辅助运放”的测试模式。

在辅助运放A的作用下,整个系统构成稳定的闭环网络,从而使VD=0,则

VC = -VS1·R1/R2

这样,调节外加电源VS1即可控制DUT的输出。

当VC等于规定电压时,

VIO = VA - VB

显然通过测量辅助运放A的输出电压VE,便可换算出VIO。

在上述的闭环回路中,DUT工作状态与普通运算放大器无异,这种测试的好处是可以通过外加电源VS1,方便地将DUT的输出钳位在规定值,同时由于VIO多为毫伏级,而将VIO放大至伏特级进行测试,对测试设备的要求不高,但受干扰信号影响较大。

美国Credence公司研制的IC测试设备ASL-1000,配置为DVI_300二块,ACS、TMU、DOAL、MUX各一块,而比较器与运算放大器在输出特性上的差异以及运放测试回路DOAL(Dual Op Amp Loop)的电路特点,决定了比较器在ASL-1000上的测试,不能象测试运放那样,利用DOAL形成一个闭环网络,来实现DUT的输出嵌位。

所以,用两块Force和Measure源dvi_9、dvi_11,辅之以doal_8的部分资源,构成了VIO的开环测试电路。

与闭环网络不同,这样的开环测试电路无法将DUT的输出电压Vout钳位。

初级比较器设计、八, 、■刖言本文主要包括:(1)分析说明比较器工作原理;(2)比较器的设计计算方法;(3)比较器的HSPICE模拟;(4)比较器物理版图设计实现;(5)设计文件列表说明。

1 2二.比较器的原理简述比较器的电路符号如右图所示,它的功能是比较输入端的信号差异,输出以之对应1的数值上离散的两种信号之一,当Vin+>Vin-时,比较器输出为高电平(Voh);当Vin+<Vin-时,比较器输出为低电平(Vol);比较器广i泛用于模拟电路和数字电路的接口部分即连续和离散的交接部分。

D 1 •比较器静态特性(1)理想比较器模型理想比较器的电路模型如下图所示:Vi n+「A+Vin + -Vi n-〈yfo(Vi n+ - Vi n-)Vovi n--V-C理想比较器模型它的传输曲线如下图所示:CA VoVo hVin+ -Vin-Vo l理想比较器的传输曲线传输曲线可以用数学函数表示如下:f o (V in V in ) 有限增益比较器模型它的传输曲线如下图所示:V °h ,when(V nV n ) 0V 0i ,when(V n V n )AV oh V ol V ih V ii(2) 有限增益比较器模型有限增益比较器的电路模型如下图所示:有限增益比较器的传输曲线传输曲线可以用数学函数表示如下:f 1(V inV in )1V oh, Whe n(V in V in ) V ih ]A v (V inV in ), whenV ilM % ) V,1V ol,,when(V in V in )V ii代血如,为一个有限值V ih V ii(3)包含输入失调电压的比较器包含输入失调电压比较器电路模型如下图所示:包含输入失调电压比较器模型它的传输曲线如下图所示:包含输入失调电压比较器的传输曲线其中的Vos为输入失调电压,它被定义为:实际比较器输出电压为零时,输入端所加的电压,它是比较器的一个重要参数,跟比较器的精度有密切的关系,而且它的温漂很难补偿。

初级比较器设计一.前言本文主要包括:(1)分析说明比较器工作原理;(2)比较器的设计计算方法;(3)比较器的HSPICE模拟;(4)比较器物理版图设计实现;(5)设计文件列表说明。

传输曲线可以用数学函数表示如下:1()in in f V V +--=,()oh in in ihV when V V V +-->(),()v in in il in in ih A V V whenV V V V +-+--<-< ,,()ol in in il V when V V V +--<(0)(0)()11v v v c cA A A s s s w τ==++ 那么,我们下面就可以分析比较器的时延:根据时延的定义和()v A s ,进行拉普拉斯逆变换,得到输入为阶跃信号min in V 的时域响应如三.比较器的设计比较器的传输时延始终是我们关注的一个重点指标,以下侧重分析时延的限制因素和设计时常常引用的公式。

66()[1oh DD DS DD DD G MIN TP V V V V V V V ⇒=-=---v v2根据基尔霍夫电压环路(KVL )和电流节点(KCL )定理,可以得到该小信号等效电路的方程组并解得:1624676224567624675656()(1/)()()1[(')][()]out m m ds ds c m v in ds n c ds n ds ds n n c n n V s g g r r sC g A s V s s r C M C r C s r r C C C C C -==++++++M ’为密勒因子, (3)估算时延为了计算的方便,()v A s 可以采用节点时间常数近似方法估算,它的另一种表示方式如下:12(0)()(1)(1)v v A A s s s p p =++其中:低频增益161246672467(0)(//)(//)()()m m v m ds ds m ds ds ds ds ds ds g g A g r r g r r g g g g ==++,2411ds ds g g p C +=-,6722ds ds g g p C +=-,1C 为第一级输出极点5的电容,2C 为为第二级输出节点6的电容。

假设输入激励信号为Vin,那么在S 域的电路响应为:Vo(s)= ()v A s Vin(s),对它进行拉普拉斯逆变换可以得到时域的响应为:/1/2211212()(0)[1]()t t o v in p e p e V t A V t p p p p ττ--=+---,其中2416721(//),2(//)ds ds ds ds r r C r r C ττ==,根据这个时域响应可以估算比较器的线性响应传输时延,为了计算方便,对该式进行级数展开得 :2221()(0)[1(1...)(1...)]1212n n o n v in n n t m t m V t A V t mt m m ≈--+++-++--,其中,211,1n p p tm t t p τ=== 再进一步简化得:2(0)()2n v ino n mt A V V t ≈令()()/2o n oh ol V t V V =+,解得:pn t ===1pn tp t τ⇒==,(21min,in p Vinm k p V ==),这就是估算线性线性响应传输时延的关系式。

附带说明一下如何选择摆率受限或线性响应受限来估算比较器的传输时延:为了比较线性响应受限和摆率受限,我们对/1/2211212()(0)[1]()t t o v in p e p e V t A V t p p p p ττ--=+---进行归1化处理得:()'21(0)11()1,1,111o n n n v inV t t mt o n n A V p m tV t e e m t tp m m p τ--==-+=≠==--其中:, 对上式进行两次求导并令其等于0可以得到归一化响应的最大斜率为:ln ln '11max()[]1m mm o n m m ndV t me e dt m ----=--------------(3.1-1) 而两级开环比较器的输出摆率为:72I SR C -=-------------(3.1-2) 26676722()DD G MINTP V V V I I ISR C C β+----==------------(3.1-3) 比较(3.1-1)、(3.1-2)和(3.1-3),当min in in V V >且摆率比(3.1-1)小时,则应采用摆率来估算比较器电路的时延。

需要特别强调的是:如果是线性响应受限则极点的位置十分重要,如果是摆率受限则对电容的充放电的能力变得更为重要。

(4)设计常用公式:为设计方便,现将常用的设计公式及步骤总结如下:①276212N P p C p p I I λλ====+ ②667722667722,'()'()P SD SAT N DS SAT W I W I L K V L K V ==,67,SD SAT dd oh DS SAT ol ss V V V V V V =-=- ③115722C C I I C =假设一个的值,计算 ④3542343'()P SG TP W I W L L K V V ==-,3SG dd icm TN V V V V +=-+⑤2467166(0)()(),v ds ds ds ds m m m A g g g g g g g ++==2112125min,(0)m oh ol v N in g V V W W A L L K I V -=== ⑥124624gd gd gs bd bd C C C C C C =++++22123221234412344123()2()()2()AD W L L L PD W L L L AD W L L L PD W L L L =++=+++=++=+++计算出C1,如果计算出的C1大于在第三步中假设的C1,则必须加大C1且重复3~6的步骤,直道计算出来的C1小于假设的C1为止。

⑦55512552,'()DS SAT icm GS ss N DS SAT W I V V V V L K V -=--=,如果5DS SATV 小于100mV 则增大11W L 2.两级开环比较器的摆率响应设计 (1)设计中用到的分析方法设计中的分析法方法法和“1”部分讲解的类同,重点要理解电路的小信号等效电路,并利用根据基尔霍夫电压环路(KVL )和电流节点(KCL )定理来求解,并进行设计计算。

(2)时延的估算在大多数的情况下,两级开环比较器会被驱动到摆率受限,此时,传输时延由下式计算:i i i ii idv vi C C dt t ∆==∆,其中:Ci 为第i 级的对地电容,由该式可以得到第i 级的传输时延为:i i i ii V t t C I ∆=∆=,总的传输时延为ii i iV tp C I ∆=∑。

(2)设计常用公式为设计方便,现将常用的设计公式及步骤总结如下: ①2762()out oh ol dv C V V I I C dt tp-===②667722667722,'()'()P SD SAT N DS SAT W I W I L K V L K V ==,67,SD SAT dd oh DS SAT ol ss V V V V V V =-=- ③假设一个C1值并在以后检查 ④1151()o oh ol dv C V V I C dt tp-=≈ ⑤3542343'()P SG TP W I W L L K V V ==-,3SG dd icm TN V V V V +=-+⑥2467166(0)()(),v ds ds ds ds m m m A g g g g g g g ++==2112125min,(0)m oh ol v N in g V V W W A L L K I V -===⑦124624gd gd gs bd bd C C C C C C =++++22123221234412344123()2()()2()AD W L L L PD W L L L AD W L L L PD W L L L =++=+++=++=+++计算出C1,如果计算出的C1大于在第三步中假设的C1,则必须加大C1且重复3~6的步骤,直道计算出来的C1小于假设的C1为止。

⑧55512552,'()DS SAT icm GS ss N DS SAT W I V V V V L K V -=--=,如果5DS SAT V 小于100mV 则增大11W L 3.复合比较器(前置线性放大级+锁存再生级)设计在参考材料中的复合比较器的电路拓扑结构如下图所示:是再生锁存器。

前置线性放大器由MB 、M1、M2、M3和M4构成,再生锁存器M7、M8、M9和M10构成,而其他的M5、M6和M11是动态时钟控制开关管。

为了保证最小的传输时延,它的设计思想在于:强调前级的大带宽和后级的高摆率,前级按负指数响应把输入信号放大到一定的值Vx ,接着锁存器按照正指数响应把这信号Vx 进一步放大,这样可以使整体的传输延迟12tp t t =+最小化。

可以用如图阶跃响应所示:由小信号等效电路可以得到节点方程组如下:17921111792111111'()()()'0o m m o o o m m o o o o V g g V GV sC V g g V GV sC V C V s +++-=+++-=2810122228101222222'()()()'0o m m o o o m m o o o o V g g V G V sC V g g V G V sC V C V s+++-=+++-=⇒79179111112121111()()1''111111m m m m o o o o o g g R g g R R C V V V V V sR C sR C s s τττ++=-=-++++8102810222221212222()()2''112121m m m m o o o o o g g R g g R R C V V V V V sR C sR C s s τττ++=-=-++++其中:11221,2R C R C ττ==假设MOS 管采用对称设计使他们的跨导相等,令:79810m m m m m g g g g g ====,12,R R R ==12,12C C C τττ====,2121,''o o o i o o V V V V V V ∆=-∆=-,则可以解得:12'(12)'1112iim o m m V V g R V V s s g R s g Rττττττ∆∆-∆∆===+-++-,其中:'12m g R ττ=-求上式的拉普拉斯逆变换的时域响应为:(12)/2///'()'m m L t g R g Rt t t o i i i i v t V e V e e V e V ττττ---∆=∆=∆≈∆=∆,即:/()L t o i v t e V τ∆=∆其中:0.342L m C g Rττ=== 要求锁存器级的传输时延,可以令:/()()/2Lt o i oh ol v t e V V V τ∆=∆=-,解得传输时延为:ln()2oh olL iV V tp V τ-=∆,显然要改善传输时延应该从L τ和i V ∆两方面着手解决。