51单片机111条指令

- 格式:doc

- 大小:44.50 KB

- 文档页数:4

51单片机指令大全1 MOV A,Rn 寄存器内容送入累加器2 MOV A,direct 直接地址单元中的数据送入累加器3 MOV A,@Ri 间接RAM 中的数据送入累加器4 MOV A,#tata 立即数送入累加器5 MOV Rn,A 累加器内容送入寄存器6 MOV Rn,direct 直接地址单元中的数据送入寄存器7 MOV Rn,#data 立即数送入寄存器8 MOV direct,A 累加器内容送入直接地址单元9 MOV direct,Rn 寄存器内容送入直接地址单元10 MOV direct,direct 直接地址单元中的数据送入另一个直接地址单元11 MOV direct,@Ri 间接RAM 中的数据送入直接地址单元12 MOV direct,#data 立即数送入直接地址单元13 MOV @Ri,A 累加器内容送间接RAM 单元14 MOV @Ri,direct 直接地址单元数据送入间接RAM 单元15 MOV @RI,#data 立即数送入间接RAM 单元16 MOV DRTR,#dat16 16 位立即数送入地址寄存器17 MOVC A,@A+DPTR 以DPTR为基地址变址寻址单元中的数据送入累加器18 MOVC A,@A+PC 以PC 为基地址变址寻址单元中的数据送入累加器19 MOVX A,@Ri 外部RAM(8 位地址)送入累加器20 MOVX A,@DPTR 外部RAM(16 位地址)送入累加器21 MOVX @Ri,A 累计器送外部RAM(8 位地址)22 MOVX @DPTR,A 累计器送外部RAM(16 位地址)23 PUSH direct 直接地址单元中的数据压入堆栈24 POP direct 弹栈送直接地址单元25 XCH A,Rn 寄存器与累加器交换26 XCH A,direct 直接地址单元与累加器交换27 XCH A,@Ri 间接RAM 与累加器交换28 XCHD A,@Ri 间接RAM 的低半字节与累加器交换算术操作类指令:1 ADD A,Rn 寄存器内容加到累加器2 ADD A,direct 直接地址单元的内容加到累加器3 ADD A,@Ri 间接ROM 的内容加到累加器4 ADD A,#data 立即数加到累加器5 ADDC A,Rn 寄存器内容带进位加到累加器6 ADDC A,direct 直接地址单元的内容带进位加到累加器7 ADDC A,@Ri 间接ROM 的内容带进位加到累加器8 ADDC A,#data 立即数带进位加到累加器9 SUBB A,Rn 累加器带借位减寄存器内容10 SUBB A,direct 累加器带借位减直接地址单元的内容11 SUBB A,@Ri 累加器带借位减间接RAM 中的内容12 SUBB A,#data 累加器带借位减立即数13 INC A 累加器加114 INC Rn 寄存器加115 INC direct 直接地址单元加116 INC @Ri 间接RAM 单元加117 DEC A 累加器减118 DEC Rn 寄存器减1 1 1219 DEC direct 直接地址单元减120 DEC @Rj 间接RAM 单元减 121 INC DPTR 地址寄存器DPTR 加 122 MUL AB A 乘以B,结果放在A23 DIV AB A 除以B,结果放在A24 DA A 累加器十进制调整布尔变量操作类指令:1 CLR C 清进位位2 CLR bit 清直接地址位3 SETB C 置进位位4 SETB bit 置直接地址位5 CPL C 进位位求反6 CPL bit 置直接地址位求反7 ANL C,bit 进位位和直接地址位相“与”8 ANL C,bit 进位位和直接地址位的反码相“与”9 ORL C,bit 进位位和直接地址位相“或”10 ORL C,bit 进位位和直接地址位的反码相“或”11 MOV C,bit 直接地址位送入进位位12 MOV bit,C 进位位送入直接地址位13 JC rel 进位位为1 则转移14 JNC rel 进位位为0 则转移15 JB bit,rel 直接地址位为1 则转移16 JNB bit,rel 直接地址位为0 则转移17 JBC bit,rel 直接地址位为1 则转移,该位清零逻辑操作数指令:1 ANL A,Rn 累加器与寄存器相“与”2 ANL A,direct 累加器与直接地址单元相“与”3 ANL A,@Ri 累加器与间接RAM 单元相“与”4 ANL A,#data 累加器与立即数相“与”5 ANL direct,A 直接地址单元与累加器相“与”6 ANL direct,#data 直接地址单元与立即数相“与”7 ORL A,Rn 累加器与寄存器相“或”8 ORL A,direct 累加器与直接地址单元相“或”9 ORL A,@Ri 累加器与间接RAM 单元单元相“或”10 ORL A,#data 累加器与立即数相“或”11 ORL direct,A 直接地址单元与累加器相“或”12 ORL direct,#data 直接地址单元与立即数相“或”13 XRL A,Rn 累加器与寄存器相“异或”14 XRL A,direct 累加器与直接地址单元相“异或”15 XRL A,@Ri 累加器与间接RAM 单元单元相“异或”16 XRL A,#data 累加器与立即数相“异或”17 XRL direct,A 直接地址单元与累加器相“异或”18 XRL direct,#data 直接地址单元与立即数相“异或”19 CLR A 累加器清“0”20 CPL A 累加器求反21 RL A 累加器循环左移22 RLC A 累加器带进位位循环左移23 RR A 累加器循环右移24 RRC A 累加器带进位位循环右移25 SWAP A 累加器半字节交换控制转移类指令:1 ACALL addr11 绝对(短)调用子程序2 LCALL addr16 长调用子程序3 RET 子程序返回4 RETI 中数返回5 AJMP addr11 绝对(短)转移6 LJMP addr16 长转移7 SJMP rel 相对转移8 JMP @A+DPTR 相对于DPTR 的间接转移9 JZ rel 累加器为零转移10 CJNE rel 累加器非零转移11 CJNE A,direct,rel 累加器与直接地址单元比较,不相等则转移12 CJNE A,#data,rel 累加器与立即数比较,不相等则转移13 CJNE Rn,#data,rel 寄存器与立即数比较,不相等则转移14 CJNE @Ri,#data,rel 间接RAM 单元与立即数比较,不相等则转移15 DJNZ Rn,rel 寄存器减1,非零转移16 DJNZ direct,erl 直接地址单元减1,非零转移17 NOP 空操作。

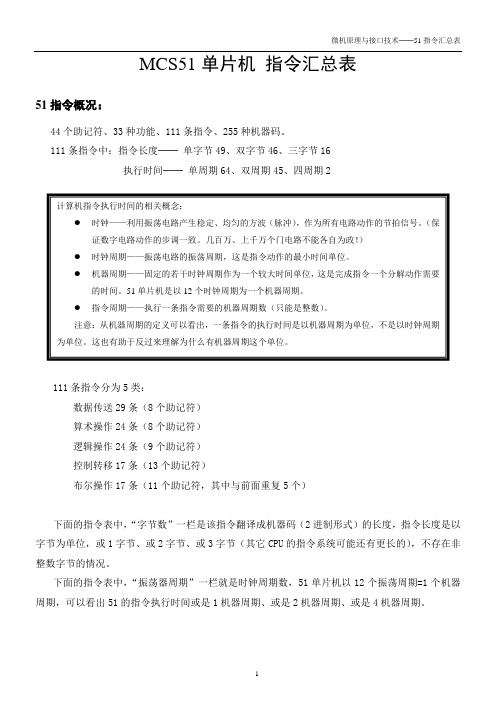

MCS51单片机指令汇总表51指令概况:44个助记符、33种功能、111条指令、255种机器码。

111条指令中:指令长度──单字节49、双字节46、三字节16执行时间──单周期64、双周期45、四周期2计算机指令执行时间的相关概念:●时钟——利用振荡电路产生稳定、均匀的方波(脉冲),作为所有电路动作的节拍信号。

(保证数字电路动作的步调一致。

几百万、上千万个门电路不能各自为政!)●时钟周期——振荡电路的振荡周期,这是指令动作的最小时间单位。

●机器周期——固定的若干时钟周期作为一个较大时间单位,这是完成指令一个分解动作需要的时间。

51单片机是以12个时钟周期为一个机器周期。

●指令周期——执行一条指令需要的机器周期数(只能是整数)。

注意:从机器周期的定义可以看出,一条指令的执行时间是以机器周期为单位,不是以时钟周期为单位。

这也有助于反过来理解为什么有机器周期这个单位。

111条指令分为5类:数据传送29条(8个助记符)算术操作24条(8个助记符)逻辑操作24条(9个助记符)控制转移17条(13个助记符)布尔操作17条(11个助记符,其中与前面重复5个)下面的指令表中,“字节数”一栏是该指令翻译成机器码(2进制形式)的长度,指令长度是以字节为单位,或1字节、或2字节、或3字节(其它CPU的指令系统可能还有更长的),不存在非整数字节的情况。

下面的指令表中,“振荡器周期”一栏就是时钟周期数,51单片机以12个振荡周期=1个机器周期,可以看出51的指令执行时间或是1机器周期、或是2机器周期、或是4机器周期。

数据传送指令一览表位操作指令一览表:。

常见51单片机指令及详解1. 简介单片机是一种集成电路,具备处理和控制功能。

51单片机是指Intel公司推出的一系列8位单片机,常用于嵌入式系统和物联网设备。

本文将介绍一些常见的51单片机指令,并对其进行详解。

2. 数据传送指令2.1 MOV指令MOV指令用于将数据从一个寄存器或内存位置传送到另一个寄存器或内存位置。

例如:MOV A, #10 ;将立即数10传送给累加器AMOV R0, R1 ;将寄存器R1的值传送给R02.2 XCH指令XCH指令用于交换两个寄存器或内存位置中的数据。

例如:XCH A, B ;交换累加器A和B的值3. 算术运算指令3.1 ADD指令ADD指令用于将两个操作数相加,并将结果保存在累加器中。

例如:ADD A, B ;将累加器A和寄存器B的值相加,结果存储在A中3.2 SUBB指令SUBB指令用于将第二个操作数的补码与累加器的值相减,并将结果存储在累加器中。

例如:SUBB A, B ;将B的补码与累加器A的值相减,结果存储在A中4. 逻辑运算指令4.1 ANL指令ANL指令用于对两个操作数进行按位与运算,并将结果存储在目的操作数中。

例如:ANL A, B ;将累加器A和寄存器B的值按位与,结果存储在A 中4.2 ORL指令ORL指令用于对两个操作数进行按位或运算,并将结果存储在目的操作数中。

例如:ORL A, B ;将累加器A和寄存器B的值按位或,结果存储在A 中5. 跳转指令5.1 JMP指令JMP指令用于无条件跳转至指定的目标地址。

例如:JMP 2000H ;跳转至内存地址2000H处执行指令5.2 JZ指令JZ指令用于在累加器为零时跳转至指定的目标地址。

例如:JZ 3000H ;当累加器为零时,跳转至内存地址3000H处执行指令6. 输入输出指令6.1 IN指令IN指令用于将外部设备的数据输入到累加器或指定的寄存器中。

例如:IN A, P1 ;将P1端口的数据输入到累加器A中6.2 OUT指令OUT指令用于将累加器或指定的寄存器中的数据输出到外部设备。

MCS-51共有111条指令,可分为5类:[1].数据传送类指令(共29条)[2].算数运算类指令(共24条)[3].逻辑运算及移位类指令(共24条)[4].控制转移类指令(共17条)[5].布尔变量操作类指令(共17条)一些特殊符号的意义Rn——当前选中的寄存器区的8个工作寄存器R0—R7(n=0-7)。

Ri——当前选中的寄存器区中可作为地址寄存器的两个寄存器R0和R1(i=0,1)direct—内部数据存储单元的8位地址。

包含0—127(255)内部存储单元地址和特殊功能寄存地址。

#data—指令中的8位常数。

#data16—指令中的16位常数。

addr16—用于LCALL和LJMP指令中的16目的地地址,目的地址的空间为64kB程序存储器地址。

#addr11—用于ACALL和AJMP指令中的11目的地地址,目的地址必须放在与下条指令第一个字节同一个2kB程序存储器空间之中。

rel—8位带符号的偏移字节,用于所有的条件转移和SJMP等指令中,偏移字节对于下条指令的第一个字节开始的-128——+127范围内。

@—间接寄存器寻址或基址寄存器的前缀。

/—为操作的前缀,声明对该位操作书取反。

DPTR—数据指针。

bit—内部RAM和特殊功能寄存器的直接寻址位。

A—累加器。

B—累加器B。

用于乘法和除法指令中。

C—进位标志位。

(x)—某地址单元中的内容。

((x))—由X寻址单元中的内容。

MCS-51的寻址方式[1].直接寻址指令中操作数直接以单元地址形式出现,例如:MOV A,68H这条指令的意义是把内部RAM中的68H单元中的数据内容传送到累加器A中。

值得注意的是直接寻址方式只能使用8位二进制地址,因此这种寻址方式仅限于内部RAM进行寻址。

低128位单元在指令中直接以单元地址的形式给出。

对于特殊功能寄存器可以使用其直接地址进行访问,还可以以它们的符号形式给出,只是特殊功能寄存器只能用直接寻址方式访问,而无其它方法。

51单片机指令表汇总51 单片机是一种广泛应用于电子工程和嵌入式系统开发的微控制器。

要熟练掌握 51 单片机的编程,了解其指令表是至关重要的。

下面就为大家汇总一下 51 单片机的常见指令。

数据传送类指令MOV 指令:这是最基本的数据传送指令,用于在寄存器之间、寄存器与存储器之间传送数据。

例如,“MOV A, 50H”就是将立即数 50H传送到累加器 A 中。

MOVX 指令:用于在片外数据存储器和累加器 A 之间进行数据传送。

比如“MOVX A, @DPTR”,将片外数据存储器中由数据指针 DPTR 所指定单元的内容传送到累加器 A 中。

MOVC 指令:用于访问程序存储器中的数据表格。

“MOVC A, @A+DPTR”是常见的用法。

算术运算类指令ADD 指令:实现加法运算。

像“ADD A, R0”就是将累加器 A 的内容和寄存器 R0 的内容相加,结果存放在累加器 A 中。

ADDC 指令:带进位加法指令。

考虑了上一次运算产生的进位标志。

SUBB 指令:用于减法运算,并且会考虑借位标志。

逻辑运算类指令ANL 指令:进行逻辑与操作。

例如“ANL A, R0”,将累加器 A 和寄存器 R0 的内容进行逻辑与运算,结果存放在累加器 A 中。

ORL 指令:执行逻辑或操作。

XRL 指令:实现逻辑异或运算。

控制转移类指令JC 指令:若进位标志为 1 则跳转。

JZ 指令:若累加器 A 的内容为 0 则跳转。

LJMP 指令:长跳转指令,可以跳转到 64KB 程序存储器空间的任意位置。

位操作类指令SETB 指令:将指定的位设置为 1。

例如“SETB P10”,将 P1 端口的第 0 位置 1。

CLR 指令:把指定的位清零。

这些只是 51 单片机指令的一部分,实际应用中还有更多的指令和组合使用方式。

在编程时,合理选择和运用这些指令能够实现各种复杂的功能。

比如,通过数据传送指令来初始化变量和读取外部数据;利用算术运算指令进行数值计算;借助逻辑运算指令处理逻辑关系;使用控制转移指令实现程序的分支和循环;运用位操作指令控制单个引脚的状态。

4条3条5条1条MCS-51指令表(共111条)操作码指令格式 (助记符) 功能简述对标志位影响字节周期备注P OV AC CY数据传送指令E8~EF MOV A, Rn 寄存器送累加器Y N N N 1 1 E5 MOV A ,direct 直接寻址单元送累加器Y N N N 2 1 E6,E7 MOV A ,@Ri 内部RAM单元送累加器Y N N N 1 1 74MOV A ,#data 立即数送累加器Y N N N 2 1 F8~FF MOV Rn,A 累加器送寄存器N N N N 1 1 A8~AF MOV Rn ,direct 直接寻址单元送寄存器N N N N 2 2 78~7F MOV Rn,#data 立即数送寄存器N N N N 2 1F5MOV direct ,A 累加器送直接寻址单元N N N N 2 1 88~8F MOV direct ,Rn 寄存器送直接寻址单元N N N N 2 2 85MOV direct1,direct2直接寻址单元2送1 N N N N 3 286,87MOV direct ,@Ri 内部RAM单元送直接寻址单元N N N N 2 275MOV direct ,#data立即数送直接寻址单元N N N N 3 2F6,F7MOV @Ri ,A 累加器送内部RAM单元N N N N 1 1A6,A7MOV @Ri ,direct 直接寻址单元送内部RAM单元N N N N 2 276,77 MOV @Ri ,#data 立即数送内部RAM单元N N N N 2 190MOV DPTR ,16位立即数送数据指针N N N N 3 2 3条#data1693 MOVC A ,@A+DPTR查表数据送累加器(DPTR为基址) Y N N N 1 2 83 MOVC A ,@A+PC查表数据送累加器(PC 为基址)Y N N N 1 2 E2,E3 MOVX A ,@Ri外部RAM 单元送累加器(8位地址)Y N N N 1 2E0MOVX A ,@DPTR外部RAM 单元送累加器(16位地址)Y N N N 1 2 F2,F3MOVX @Ri ,A累加器送外部RAM 单元(8位地址)N N N N 1 2F0MOVX @DPTR ,A累加器送外部RAM 单元(16位地址) N N N N 1 2 C0 PUSH direct 直接寻址单元压入栈顶 N N N N 2 2 D0 POP direct 栈顶弹出指令直接寻址单元N N N N 2 2 C8~CF XCH A ,Rn累加器与寄存器交换Y N N N 1 1C5XCH A ,direct累加器与直接寻址单元交换Y N N N 1 1 C6,C7XCH A ,@Ri累加器与内部RAM 单元交换Y N N N 2 1D6,D7XCHD A ,@Ri累加器与内部RAM 单元低4位交换Y N N N 1 1算术运算类指令2条4条28~2F ADD A , Rn 累加器加寄存器Y Y Y Y 1 125 ADD A , direct 累加器加直接寻址单元 Y Y Y Y 2 1 26,27 ADD A , @Ri累加器加内部RAM 单元 Y Y Y Y 1 124 ADD A , #data 累加器加立即数Y Y Y Y 2 1 38~3FADDC A , Rn累加器加寄存器和进位标志Y Y Y Y 1 135ADDC A , direct累加器加直接寻址单元和进位标志Y Y Y Y 2 1 36,37ADDC A , @Ri累加器加内部RAM 单元和进位标志Y Y Y Y 1 134ADDC A , #data累加器加立即数和进位标志Y Y Y Y 2 198~9FSUBB A , Rn累加器减寄存器和进位标志Y Y Y Y 1 195SUBB A , direct累加器减直接寻址单元和进位标志Y Y Y Y 2 1 96,97SUBB A , @Ri累加器减内部RAM 单元和进位标志Y Y Y Y 1 194 SUBB A , #data 累加器减立即数和进位标志 Y Y Y Y 2 1 04 INC A 累加器加1 Y N N N 1 1 08~0F INC Rn 寄存器加1 N N N N 1 1 05 INC direct 直接寻址单元加1 N N N N 2 1 06,07 INC @Ri 内部RAM 单元加1 N N N N 1 1 A3INC DPTR数据指针加11 214 DEC A 累加器减1 Y N N N 1 1 18~1F DEC Rn 寄存器减1 N N N N 1 1 15 DEC direct 直接寻址单元减1 N N N N 2 1 16,17 DEC @Ri 内部RAM单元减1 N N N N 1 1A4 MUL AB 累加器乘寄存器B Y Y N Y 1 4 16位积的低位在A中,高位在B中84 DIV AB 累加器除以寄存器B Y Y N Y 1 4商在A中,余数在B中D4 DA A 十进制调整Y Y Y Y 1 1逻辑运算类指令58~5F ANL A, Rn 累加器与寄存器Y N N N 1 155 ANL A, direct 累加器与直接寻址单元Y N N N 2 156,57 ANL A, @Ri 累加器与内部RAM单元Y N N N 1 154 ANL A, #data 累加器与立即数Y N N N 2 152 ANL direct, A 直接寻址单元与累加器N N N N 2 153ANL direct,#data直接寻址单元与立即数N N N N 3 248~4F ORL A, Rn 累加器或寄存器Y N N N 1 145 ORL A,direct 累加器或直接寻址单元Y N N N 2 146,47 ORL A,@Ri 累加器或内部RAM单元Y N N N 1 144 ORL A,#data 累加器或立即数Y N N N 2 142 ORL direct, A 直接寻址单元或累加器N N N N 2 143ORL direct,#data直接寻址单元或立即数N N N N 3 2 68~6F XRL A, Rn 累加器异或寄存器Y N N N 1 1 65 XRL A,direct 累加器异或直接寻址单元Y N N N 2 1 66,67 XRL A,@Ri 累加器异或内部RAM单元Y N N N 1 1 64 XRL A,#data 累加器异或立即数Y N N N 2 162 XRL direct, A 直接寻址单元异或累加器N N N N 2 163XRL direct,#data直接寻址单元异或立即数N N N N 3 2 E4 CLR A 累加器清零Y N N N 1 1 F4 CPL A 累加器取反N N N N 1 1 23 RL A 累加器左循环移位N N N N 1 133 RLC A 累加器连进位标志左循环移位Y N N Y 1 13 RR A 累加器右循环移位N N N N 1 113 RRC A 累加器连进位标志右循环移位Y N N Y 1 1C4 SWAP A累加器高4位与低4位交换N N N N 1 1 位操作类指令C3 CLR C C清零N N N Y 1 1 C2 CLR bit 直接寻址位清零N N N 2 1 D3 SETB C C置位N N N Y 1 1 D2 SETB bit 直接寻址位置位N N N 2 1B3 CPL C C取反N N N Y 1 1B2 CPL bit 直接寻址位取反N N N 2 182 ANL C, bit C逻辑与直接寻址位N N N Y 2 2B0 ANL C, /bit C逻辑与直接寻址位的反N N N Y 2 272 ORL C, bit C逻辑或直接寻址位N N N Y 2 2A0 ORL C, /bit C逻辑或直接寻址位的反N N N Y 2 2A2 MOV C, bit 直接寻址位送C N N N Y 2 192 MOV bit, C C送直接寻址位N N N N 2 2控制转移指令xxx10001 A CALL addr11 2KB范围内绝对调用N N N N 2 212 LCALL addr16 64KB范围内长调用N N N N 3 222 RET 子程序返回N N N N 1 232 RETI 中断返回N N N N 1 2xxx00001 A JMP addr11 2KB范围内绝对转移N N N N 2 22 LJMP addr16 64KB范围内长转移N N N N3 280 SJMP rel 相对短转移N N N N 2 273 JMP @A+DPTR 相对长转移N N N N 1 2 用于分枝散转60 JZ rel 累加器为零转移N N N N 2 270 JNZ rel 累加器非零转移N N N N 2 240 JC rel C为1转移N N N N 2 250 JNC rel C为零转移N N N N 2 220 JB bit,rel 直接寻址位为1转移N N N N 3 230JNB bit ,rel 直接寻址为0转移 N N N N 3 210JBC bit ,rel直接寻址位为1转移并清该位N N N N 3 2B5CJNE A ,direct ,rel累加器与直接寻址单元不等转移 N N N Y 3 2A 大于等于direct 时清C, A 小于direct 时置CB4CJNE A ,#data ,rel累加器与立即数不等转移N N N Y 3 2 A 大于等于#data 时清C, A小于#data 时置C B8~BFCJNE Rn ,#data ,rel寄存器与立即数不等转移N N N Y 3 2 Rn 大于等于#data 时清C, Rn 小于#data 时置C B6,B7CJNE @Ri ,#data ,rel RAM 单元与立即数不等转移 N N N Y 3 2@Ri 大于等于#data 时清C, @Ri 小于#data 时置CD8~DF DJNZ Rn ,rel 寄存器减1不为零转移 N N N N 2 2 D5DJNZ direct ,rel直接寻址单元减1不为零转N N N N 3 2移0 NOP 空操作N N N N 1 1。

51单片机111条指令一览表指令字节周期动作说明算数运算指令1.ADD A,Rn 1 1 将累加器与寄存器的内容相加,结果存回累加器2.ADD A,direct 2 1 将累加器与直接地址的内容相加,结果存回累加器3.ADD A,@Ri 1 1 将累加器与间接地址的内容相加,结果存回累加器4.ADD A,#data 2 1 将累加器与常数相加,结果存回累加器5.ADDC A,Rn 1 1 将累加器与寄存器的内容及进位C相加,结果存回累加器6.ADDC A,direct 2 1 将累加器与直接地址的内容及进位C相加,结果存回累加器7.ADDC A,@Ri 1 1 将累加器与间接地址的内容及进位C相加,结果存回累加器8.ADDC A,#data 2 1 将累加器与常数及进位C相加,结果存回累加器9.SUBB A,Rn 1 1 将累加器的值减去寄存器的值减借位C,结果存回累加器10.SUBB A,direct 2 1 将累加器的值减直接地址的值减借位C,结果存回累加器11.SUBB A,@Ri 1 1 将累加器的值减间接地址的值减借位C,结果存回累加器12.SUBB A,#data 2 1 将累加器的值减常数值减借位C,结果存回累加器13.INC A 1 1 将累加器的值加114.INC Rn 1 1 将寄存器的值加l15.INC direct 2 1 将直接地址的内容加116.INC @Ri 1 1 将间接地址的内容加117.INC DPTR 1 1 数据指针寄存器值加1说明:将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位18.DEC A 1 1 将累加器的值减119.DEC Rn 1 1 将寄存器的值减120.DEC direct 2 1 将直接地址的内容减121.DEC @Ri 1 1 将间接地址的内容减122.MUL AB 1 4 将累加器的值与B寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器说明:将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

如果积大于FFH,则溢出标志位(OV)被设定为1,而进位标志位为0 23.DIV AB 1 4 将累加器的值除以B寄存器的值,结果的商存回累加器,余数存回B寄存器说明:无符号的除法运算,将累加器A除以B寄存器的值,商存入A,余数存入B。

执行本指令后,进位位(C)及溢出位(OV)被清除为024.DA A 1 1 将累加器A作十进制调整,若(A) 3-0>9或(AC)=1,则(A) 3-0←(A)3-0+6若(A) 7-4>9或(C)=1,则(A) 7-4←(A)7-4+6逻辑运算指令25.ANL A,Rn 1 1 将累加器的值与寄存器的值做AND的逻辑判断,结果存回累加器26.ANL A,direct 2 1 将累加器的值与直接地址的内容做AND的逻辑判断,结果存回累加器27.ANL A,@Ri 1 1 将累加器的值与间接地址的内容做AND的逻辑判断,结果存回累加器28.ANL A,#data 2 1 将累加器的值与常数做AND的逻辑判断,结果存回累加器指令字节周期动作说明29.ANL direct,A 2 1 将直接地址的内容与累加器的值做AND的逻辑判断,结果存回该直接地址30.ANL direct,#data 3 2 将直接地址的内容与常数值做AND的逻辑判断,结果存回该直接地址31.ORL A,Rn 1 1 将累加器的值与寄存器的值做OR的逻辑判断,结果存回累加器32.ORL A,direct 2 1 将累加器的值与直接地址的内容做OR的逻辑判断,结果存回累加器33.ORL A,@Ri 1 1 将累加器的值与间接地址的内容做OR的逻辑判断,结果存回累加器34.ORL A,#data 2 1 将累加器的值与常数做OR的逻辑判断,结果存回累加器35.ORL direct,A 2 1 将直接地址的内容与累加器的值做OR的逻辑判断,结果存回该直接地址36.ORL direct,#data 3 2 将直接地址的内容与常数值做OR的逻辑判断,结果存回该直接地址37.XRL A,Rn 1 1 将累加器的值与Rn寄存器的值做XOR的逻辑判断,结果存回累加器38.XRL A,direct 2 1 将累加器的值与直接地址的内容做XOR的逻辑判断,结果存回累加器39.XRL A,@Ri 1 1 将累加器的值与间接地扯的内容做XOR的逻辑判断,结果存回累加器40.XRL A,#data 2 1 将累加器的值与常数作XOR的逻辑判断,结果存回累加器41.XRL direct,A 2 1 将直接地址的内容与累加器的值做XOR的逻辑判断,结果存回该直接地址42.XRL direct,#data 3 2 将直接地址的内容与常数的值做XOR的逻辑判断,结果存回该直接地址43.CLR A 1 1 清除累加器的值为044.CPL A 1 1 将累加器的值反相45.RL A 1 1 将累加器的值左移一位46.RLC A 1 1 将累加器含进位C左移一位47.RR A 1 1 将累加器的值右移一位48.RRC A 1 1 将累加器含进位C右移一位49.SW AP A 1 1 将累加器的高4位与低4位的内容交换。

(A)3-0←(A)7-4 数据转移指令50.MOV A,Rn 1 1 将寄存器的内容载入累加器51.MOV A,direct 2 1 将直接地址的内容载入累加器52.MOV A,@Ri 1 1 将间接地址的内容载入累加器53.MOV A,#data 2 1 将常数载入累加器54.MOV Rn,A 1 1 将累加器的内容载入寄存器55.MOV Rn,direct 2 2 将直接地址的内容载入寄存器56.MOV Rn,#data 2 1 将常数载入寄存器57.MOV direct,A 2 1 将累加器的内容存入直接地址指令字节周期动作说明58.MOV direct,Rn 2 2 将寄存器的内容存入直接地址59.MOV direct1, direct2 3 2 将直接地址2的内容存入直接地址160.MOV direct,@Ri 2 2 将间接地址的内容存入直接地址61.MOV direct,#data 3 2 将常数存入直接地址62.MOV @Ri,A 1 1 将累加器的内容存入某间接地址63.MOV @Ri,direct 2 2 将直接地址的内容存入某间接地址64.MOV @Ri,#data 2 1 将常数存入某间接地址65.MOV DPTR,#data16 3 2 将16位的常数存入数据指针寄存器66.MOVC A,@A+DPTR 1 2 (A) ←((A)+(DPTR))累加器的值再加数据指针寄存器的值为其所指定地址,将该地址的内容读入累加器67.MOVC A,@A+PC 1 2 (PC)←(PC)+1;(A)←((A)+(PC))累加器的值加程序计数器的值作为其所指定地址,将该地址的内容读入累加器68.MOVX A,@Ri 1 2 将间接地址所指定外部存储器的内容读入累加器(8位地址) 69.MOVX A,@DPTR 1 2 将数据指针所指定外部存储器的内容读入累加器(16位地址)70.MOVX @Ri,A 1 2 将累加器的内容写入间接地址所指定的外部存储器(8位地址)71.MOVX @DPTR,A 1 2 将累加器的内容写入数据指针所指定的外部存储器(16位地址)72.PUSH direct 2 2 将直接地址的内容压入堆栈区73.POP direct 2 2 从堆栈弹出该直接地址的内容74.XCH A,Rn 1 1 将累加器的内容与寄存器的内容互换75.XCH A,direct 2 1 将累加器的值与直接地址的内容互换76.XCH A,@Ri 1 1 将累加器的值与间接地址的内容互换77.XCHD A,@Ri 1 1 将累加器的低4位与间接地址的低4位互换布尔代数运算78.CLR C 1 1 清除进位C为079.CLR bit 2 1 清除直接地址的某位为080.SETB C 1 1 设定进位C为181.SETB bit 2 1 设定直接地址的某位为182.CPL C 1 1 将进位C的值反相83.CPL bit 2 1 将直接地址的某位值反相84.ANL C,bit 2 2 将进位C与直接地址的某位做AND的逻辑判断,结果存回进位C85.ANL C,/bit 2 2 将进位C与直接地址的某位的反相值做AND的逻辑判断,结果存回进位C86.ORL C,bit 2 2 将进位C与直接地址的某位做OR的逻辑判断,结果存回进位C87.ORL C,/bit 2 2 将进位C与直接地址的某位的反相值做OR的逻辑判断,结果存回进位C88.MOV C,bit 2 1 将直接地址的某位值存入进位C89.MOV bit,C 2 2 将进位C的值存入直接地址的某位90.JC rel 2 2 若进位C=1则跳至rel的相关地址91.JNC rel 2 2 若进位C=0则跳至rel的相关地址92.JB bit,rel 3 2 若直接地址的某位为1,则跳至rel的相关地址93.JNB bit,rel 3 2 若直接地址的某位为0,则跳至rel的相关地址指令字节周期动作说明94.JBC bit,rel 3 2 若直接地址的某位为1,则跳至rel的相关地址,并将该位值清除为0程序跳跃95.ACALL addr11 2 2 调用2K程序存储器范围内的子程序96.LCALL addr16 3 2 调用64K程序存储器范围内的子程序97.RET 1 2 从子程序返回98.RETI 1 2 从中断子程序返回99.AJMP addr11 2 2 绝对跳跃(2K内)100.LJMP addr16 3 2 长跳跃(64K内)101.SJMP rel 2 2 短跳跃(2K内)-128~+127字节102.JMP @A+DPTR 1 2 跳至累加器的内容加数据指针所指的相关地址103.JZ rel 2 2 累加器的内容为0,则跳至rel所指相关地址104.JNZ rel 2 2 累加器的内容不为0,则跳至rel所指相关地址105.CJNE A,direct,rel 3 2 将累加器的内容与直接地址的内容比较,不相等则跳至rel 所指的相关地址106.CJNE A,#data,rel 3 2 将累加器的内容与常数比较,若不相等则跳至rel所指的相关地址107.CJNE @Rn,#data,rel 3 2 将寄存器的内容与常数比较,若不相等则跳至rel所指的相关地址108.CJNE @Ri,#data,rel 3 2 将间接地址的内容与常数比较,若不相等则跳至rel所指的相关地址109.DJNZ Rn,rel 2 2 将寄存器的内容减1,不等于0则跳至rel所指的相关地址,等于0则顺序执行110.DJNZ direct,rel 3 2 将直接地址的内容减1,不等于0则跳至rel所指的相关地址111.NOP 1 1 无动作。