FPGA4位十进制频率计设计实验报告

- 格式:doc

- 大小:624.39 KB

- 文档页数:6

基于FPGA的数字频率计设计学院:专业:班级:姓名:学号:审阅老师:评分:目录一、课程设计目的 (3)二、设计任务 (3)三、功能要求与技术指标 (3)四、数字频率计工作原理概述 (3)五.数字频率计实现方法 (4)六.结论与误差分析 (11)七.VHDL程序: (12)一、课程设计目的熟悉EDA工具,掌握用VHDL语言进行数字系统设计的基本方法和流程,提高工程实践能力。

二、设计任务设计一数字频率计,用VHDL语言描述,用QuartusII工具编译和综合,并在实验板上实现。

三、功能要求与技术指标1.基本功能要求(1)能够测量出方波的频率,其范围50Hz~50KHz。

(2)要求测量的频率绝对误差±5Hz。

(3)将测量出的频率以十进制格式在实验板上的4个数码管上显示。

(4)测量响应时间小于等于10秒。

以上(1)~(4)基本功能要求均需实现。

2.发挥部分(1)提高测量频率范围,如10Hz~100KHz或更高、更低频率,提高频率的测量绝对值误差,如达到±1Hz。

(2)可以设置量程分档显示,如X1档(显示范围1Hz~9999Hz),X10档(显示范围0.001KHz~9.999KHz),X100档(显示范围0.100KHz~999.9KHz)...可以自定义各档位的范围。

量程选择可以通过按键选择,也可以通过程序自动选择量程。

(3)若是方波能够测量方波的占空比,并通过数码管显示。

以上(1)~(3)发挥功能可选择实现其中的若干项。

四、数字频率计工作原理概述1.数字频率计简介在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

而数字频率计是采用数字电路制成的实现对周期性变化信号的频率的测量。

2.常用频率测量方法:方案一采用周期法。

通过测量待测信号的周期并求其倒数,需要有标准倍的频率,在待测信号的一个周期内,记录标准频率的周期数,这种方法的计数值会产生最大为±1个脉冲误差,并且测试精度与计数器中记录的数值有关,为了保证测试精度,测周期法仅适用于低频信号的测量。

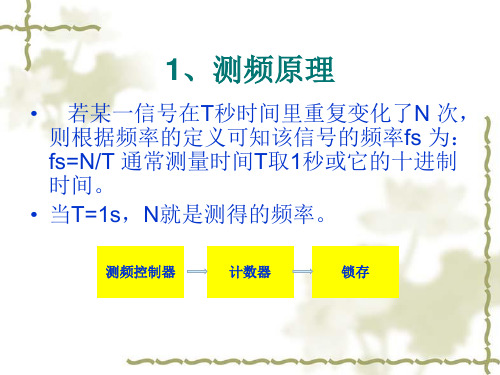

数字逻辑电路大型实验报告姓名指导教师专业班级学院信息工程学院提交日期1一、实验目的学习用FPGA实现数字系统的方法二、实验内容1.FPGA, Quartus II 和VHDL使用练习2.四位数字频率计的设计三、四位数字频率计的设计1.工作原理当系统正常工作时,8Hz信号测频控制信号发生器进行信号的变换,产生计数信号,被测信号通过信号整形电路产生同频率的矩形波,送入计数模块,计数模块对输入的矩形波进行计数,将计数结果送入锁存器中,保证系统可以稳定显示数据,显示译码驱动电路将二进制表示的计数结果转换成相应的能够在七段数码显示管上可以显示的十进制结果。

在数码显示管上可以看到计数结果。

工作原理图如下:2.设计方案21) 整形电路:整形电路是将待测信号整形变成计数器所要求的脉冲信号2)控制信号产生器(分频电路):用8Hz时钟信号产生1Hz时钟信号、锁存器信号和cs信号3)计时器:采用级联的方式表示4位数4)锁存器:计数结束后的结果在锁存信号控制下锁存5)译码器:将锁存的计数结果转换为七段显示码3.顶层原理图(总图)3注:①CLK1:8Hz时钟信号输入; CLKIN:待测信号输入;②显像时自左而右分别是个位、十位、百位、千位;③顶层原理图中:(1)consignal模块:为频率计的控制器,产生满足时序要求的三个控制信号;(2)cnt10模块:有四个,组成四位十进制(0000-1001)计数器,使计数器可以从0计数到9999;(3)lock模块:有四个,锁存计数结果;(4)decoder模块:有四个,将8421BCD码的锁存结果转换为七段显示码。

4.底层4个模块(控制信号产生模块,十进制计数器模块,锁存器模块,译码模块)的仿真结果。

cnt10模块(十进制计数器模块):输入:CLK:待测量的频率信号(时钟信号模拟);CLR:清零信号,当clr=1时计数器清零,输出始终为0000,只有当clr=0时,计数器才正常计数CS:闸门信号,当cs=1时接收clk计数,当cs=0时,不接收clk,输出为0;输出:4co:进位信号,图中,在1001(9)的上方产生一个进位信号0,其余为1。

数字频率计设计报告书一、设计要求设计一个4位十进制数字式频率计,最大测量范围为10MHz。

量程分10kHz、100kHz、1MHz和10MHz四档(最大读数分别为9.999kHz、99.99kHz、999.9kHz、9999.kHz).量程自动转换规则如下:(1)当读数大于9999时,频率计处于超量程状态,此时显示器发出溢出指示,下一次测量时,量程自动增大一档,小数点位置随量程变更自动移位。

(2)可用手动方式使量程在每次测量开始时处于最低档。

显示方式如下:(3)采用记忆显示方式,即计数过程中不显示数据,待计数过程结束以后,显示计数结果,将此显示结果保持到下一次计数结束。

显示时间应不小于1s。

(4)送入信号应是符合CMOS电路要求的脉冲波,对于小信号模拟信号应有放大整形电路。

二、方案设计<1>整体思路所谓频率就是周期性信号在单位时间 (1s)内变化的次数。

若在一定时间间隔 T内测得周期性信号的重复变化次数为 N ,则频率可表示为 f =N /T (Hz)。

被测信号fx经放大整形电路变成计数电路所要求的脉冲信号,其频率与被测信号fx的频率相同。

基准电路提供标准时间基准信号clk,其高电平持续时间 t 1 = 1 s,当 1 s信号来到时 ,闸门电路开通 ,被测脉冲信号通过闸门电路,成为计数电路的计数脉冲 CP,计数电路开始计数,直到 ls信号结束时闸门电路关闭 ,停止计数。

若在闸门时间 1 s内计数电路计得的脉冲个数为 N ,则被测信号频率 f =NHz。

控制电路的作用有两个:一是产生锁存脉冲 CLK,使显示电路上的数字稳定;二是产生清“0”脉冲,使计数电路每次测量从零开始计数。

<2>时钟信号的选择设计电路中时钟信号采用12M有源晶振产生,下面是12M有源晶振引脚图:<3>整形电路的选择整形电路中可以用运算放大器LM311组成电压选择器实现,以下是关于此芯片的资料:引脚功能:GROUND/GND 接地INPUT + 正向输入端INPUT - 反向输入端OUTPUT 输出端BALANCE 平衡BALANCE/STROBE 平衡/选通V+ 电源正V- 电源负NC 空脚LM311引脚图由于LM311过于复杂且此次设计要求精度不高,整形电路可以改为如下电路:这样产生稳定3.3V为幅值的信号送入EPM570中,对芯片起到保护作用。

FPGA四位频率计设计Verilog语言实现设计任务:用混合设计的方法设计一个4位频率计,主要设计模块为测频控制器、计数器、锁存器、译码器,显示器为7段LED显示管。

并合理选择实验模式,进行下载测试。

//计数器模块modulejishu(clk,zamen,fuwei,jieguo1,jieguo2,jieguo3,jieguo4);inputclk;inputzamen;inputfuwei;output[3:0]jieguo1,jieguo2,jieguo3,jieguo4;reg[3:0]jieguo1,jieguo2,jieguo3,jieguo4;always @(posedgeclk)if(fuwei)beginjieguo1<=4'b0000;jieguo2<=4'b0000;jieguo3<=4'b0000;jieguo4<=4'b0000;endelse if(zamen) //4个if完成4位计数器的进位beginif(jieguo1==4'b1001)begin jieguo1<=4'b0000;jieguo2<=jieguo2+1;if(jieguo2==4'b1001)begin jieguo2<=4'b0000;jieguo3<=jieguo3+1;if(jieguo3==4'b1001)begin jieguo3<=4'b0000;jieguo4<=jieguo4+1;if(jieguo4==4'b1001)jieguo4<=4'b0000;endendendelsejieguo1<=jieguo1+1;endendmodulemodule DECL7S(A,LED7S);input[3:0]A;output[6:0]LED7S;reg[6:0]LED7S;always@(A)begincase(A)4'b0000: LED7S<=7'b0111111;4'b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011: LED7S<=7'b1001111;4'b0100: LED7S<=7'b1100110;4'b0101: LED7S<=7'b1101101;4'b0110: LED7S<=7'b1111101;4'b0111: LED7S<=7'b0000111;4'b1000: LED7S<=7'b1111111;4'b1001: LED7S<=7'b1101111;4'b1010: LED7S<=7'b1110111;4'b1011: LED7S<=7'b1111100;4'b1100: LED7S<=7'b0111001;4'b1101: LED7S<=7'b1011110;4'b1110: LED7S<=7'b1111001;4'b1111: LED7S<=7'b1110001; default:LED7S<=7'b0111111; endcaseendendmodulemodulecepin(CLKK,CNT_EN,RST_CNT,LOAD);input CLKK;output CNT_EN,RST_CNT,LOAD;wire CNT_EN,LOAD;reg RST_CNT,JICUN;always @(posedge CLKK)//两个always语句块实现测频功能JICUN<=~JICUN;always @(CLKK or JICUN)beginif(CLKK==1'b0 & JICUN==1'b0) RST_CNT<=1'b1;else RST_CNT<=1'b0;endassign LOAD=~JICUN;assign CNT_EN=JICUN;endmodule//锁存器module suocun(result1,result2,result3,result4,data1,data2,data3,data4,kaiguan);output[3:0]data1,data2,data3,data4;input[3:0]result1,result2,result3,result4;inputkaiguan;reg[3:0]data1,data2,data3,data4;always @(posedgekaiguan)if(kaiguan)begindata1<=result1;data2<=result2;data3<=result3;data4<=result4;endendmodule。

4位十进制频率计设计频率计是一种用来测量信号频率的仪器或设备,它广泛应用于电子、通信、无线电、音频和视频等领域。

本文将介绍一种设计思路,用于实现一个4位十进制频率计。

==设计思路==为了设计一个能够测量高精度频率的4位十进制频率计,我们需要考虑以下几个关键因素:1.输入范围:频率计应该能够适应不同频率范围的输入信号,从几赫兹到几百兆赫兹。

为了实现这一点,我们可以选择一个高性能的计数器和适当的预分频器。

2.分辨率:分辨率是指频率计能够测量的最小变化量。

较高的分辨率可以提供更精确的测量结果。

为了实现较高的分辨率,我们可以选择一个高位数的计数器以及适当的预分频器。

3.显示和输出:频率计应该能够以易读的方式显示测量结果,并可以通过输出接口连接到其他设备或系统。

基于以上要求,我们可以采用以下设计思路来实现4位十进制频率计。

1.时钟源:选择一个高稳定性的晶振作为频率计的时钟源。

晶振的稳定性对于频率计的测量精度非常重要。

2.频率测量:我们可以使用计数器和预分频器的组合来测量输入信号的频率。

计数器将输入信号进行计数,并以预定的时间间隔将计数器的值读取到显示寄存器中。

a.计数器:选择一个具有足够位数的计数器,以提供较高的分辨率。

例如,采用16位或者更高位的计数器,可以提供较高的计数能力和分辨率。

b.预分频器:使用预分频器将输入信号的频率降低到易于计数器处理的范围内。

预分频器的选择要根据输入信号的频率范围来确定。

比如,对于输入信号频率范围为几赫兹到几百兆赫兹,我们可以选择一个可设置不同分频系数的预分频器。

c.计数时间:选择一个适当的计数时间来保证测量结果的准确性。

较短的计数时间会降低分辨率,较长的计数时间会增加测量误差。

通过权衡这两者,我们可以设定一个合适的计数时间。

3.显示和输出:在实现频率计的显示和输出功能时,我们可以采用以下几种方式:a.LED数码管:选择一个4位数码管显示器来显示频率测量结果。

设计一个驱动电路,将显示寄存器中的计数值转换为相应的数码管显示。

实验五4位十进制频率计设计一、实验目的:设计4位十进制频率计,学习较复杂的数字系统设计方法。

二、原理说明:根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。

这清0个信号可以由一个测频控制信号发生器产生,即图5-1中的TESTCTL,它的设计要求是,TESTCTL的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的EN使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进各锁存器REG4B中,并由外部的7段译码器译出,显示计数值。

设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作作准备。

【例5-1】10进制计数器,用于计算分频结果,并连接数码管显示。

module cnt10d(clk,rst,en,cq,cout);input clk;input rst;input en;output[3:0] cq;output cout;reg[3:0] cq;reg cout;always@(posedge clk or posedge rst)begin if(rst) cq<=4'b0000;else if(en) begin if(cq<9) begin cq<=cq+1'b1;cout<=1'b0; endelse begin cq<=4'b0000; cout<=1'b1; endendendendmodule【例5-2】--测频控制器,使得频率计能自动测频module testctl(clkk,cnt_en,rst_cnt,load);input clkk; // 1HZoutput cnt_en;output rst_cnt;output load;reg div2clk;wire cnt_en;reg rst_cnt;wire load;always@(posedge clkk)div2clk<=~div2clk;always @(clkk or div2clk) beginif(!clkk & !div2clk) rst_cnt<=1'b1;else rst_cnt<=1'b0;endassign load = ~div2clk;assign cnt_en = div2clk;endmodule【例5-3】锁存器,将频率计的每位数锁存后输出module reg4(clk,cq,led );input clk;input[3:0] cq;output[3:0] led;reg[3:0] led;always@(posedge clk)led<=cq;endmodule[例5-4] 用原理图方式将各模块连接起来也可以用.v文件实现系统组合。

四位十进制频率计EDA实验报告实验四四位十进制频率计实验目的1.掌握四位十进制频率计的工作原理并能够用virlog语言编写代码,进一步熟悉EDA6000实验箱的使用方法。

2.进一步熟悉quartusII建立程序编译、仿真及下载的操作流程并学会四位十进制频率计的Verilog硬件设计。

3.代码modulefrecounter(clk,uclk,ge_bit,shi_bit,bai_bit,qian_bit);input clk,uclk;output [3:0] ge_bit,shi_bit,bai_bit,qian_bit;reg [3:0]ge_bit,shi_bit,bai_bit,qian_bit;reg div,en,load,cls;reg [3:0] A,B,C,D;always @(negedge clk)begin div=~div;en=div;load=~en;cls=clk&load;endalways @(posedge uclk or posedge cls)beginif(cls) begin A=4'd0;B=4'd0;C=4'd0;D=4'd0; endelse if(en) begin A=A+4'd1;if(A==4'D10) begin A=4'd0;B=B+4'd1; endif(B==4'D10) begin B=4'd0;C=C+4'd1; endif(C==4'D10) begin C=4'd0;D=D+4'd1; endendendalways @(posedge load)beginge_bit=A;shi_bit=B;bai_bit=C;qian_bit=D;endendmodule实验步骤1.新建Verilog工程,编写代码并保存至与模块名对应的文件夹。

重庆交通大学信息科学与工程学院综合性实验报告姓名:学号班级:专业级班实验项目名称:四位十进制频率计设计实验项目性质:综合性设计实验实验所属课程: EDA技术实验室(中心):现代电子实验中心指导教师:实验完成时间: 2011 年 10月 29日一、课题任务与要求设计一个数字频率计,能用数码管动态当前输入频率,并能达到以下要求:1、四位十进制频率计2、显示范围1Hz~10KHz3、显示时间不少于1S4、具有记忆显示的功能,即在测量过程中不刷新数据,等结束后才显示测量结果,给出待测信号的频率值,并保存到下一次测量结束。

二、设计系统的概述1、分析设计要求可知:此系统需用到多路时钟信号,因此在设计时首先考虑之中信号的引入,本设计中从外部输入频率为1Hz的CLK1Hz信号,然后通过编程将此信号进行处理得到所需的多路信号:en是使能信号、l ock是锁存信号、rst是复位信号,它们的基本时序关系如下:2、设计一个4位的十进制加法计数器,用来统计1s内输入的外部脉冲个数(单位时间内的输入脉冲数即输入信号的频率)。

3、为了能够使数码管上的示数保持至少1s还需要配合lock锁存信号设计一个锁存器,在锁存信号有效期间,数码管的示数保持不变。

4、当完成了计数之后还需对4位十进制计数器的输出信号进行译码输出,在此设计了一个7段数码管的译码显示电路。

三、单元电路的设计与分析(重点描述自己设计部分)总体设计电路框图:1、时钟控制电路(clock)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock isport(clk1Hz:in std_logic;rst,en,lock:out std_logic);end entity clock;architecture one of clock issignal div2:std_logic;beginp1:process(clk1Hz)beginif(clk1Hz'event and clk1Hz='1') thendiv2<=not div2;end if;end process p1;p2:process(clk1Hz,div2)beginif clk1Hz='0' and div2='0' then rst<='1';else rst<='0';end if;end process p2;en<=div2;lock<=not div2;end one;2、一位的十进制计数电路(cnt10)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk,rst,en:in std_logic;count:out std_logic;q:out std_logic_vector(3 downto 0));end entity cnt10;architecture one of cnt10 issignal temp:std_logic_vector(3 downto 0);beginprocess(clk,rst,en)beginif rst='1' then temp<="0000";elsif(clk'event and clk='1')and en='1' thenif temp="1001" then temp<="0000";count<='1';else temp<=temp+1;count<='0';end if;end if;end process;q<=temp;end one;3、四位十进制计数器电路(cnt4_10)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4_10 isport(clkin,rst,en:in std_logic;count:out std_logic;q:out std_logic_vector(15 downto 0));end entity cnt4_10;architecture one of cnt4_10 iscomponent cnt10 isport(clk,rst,en:in std_logic;count:out std_logic;q:out std_logic_vector(3 downto 0));end component;signal temp:std_logic_vector(2 downto 0);beginu1:cnt10 port map(clkin,rst,en,temp(0),q(3 downto 0));u2:cnt10 port map(temp(0),rst,en,temp(1),q(7 downto 4));u3:cnt10 port map(temp(1),rst,en,temp(2),q(11 downto 8));u4:cnt10 port map(temp(2),rst,en,count,q(15 downto 12));end architecture one;4、锁存器电路(reg16)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity reg16 isport(lockin:in std_logic;din:in std_logic_vector(15 downto 0);dout:out std_logic_vector(15 downto 0));end entity reg16;architecture one of reg16 isbeginprocess(lockin,din)beginif lockin'event and lockin='1'then dout<=din;end if;end process;end architecture one;5、译码显示电路(shuma)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shuma isport(din:in std_logic_vector(15 downto 0);dout:out std_logic_vector(27 downto 0));end entity shuma;architecture one of shuma isbeginprocess(din)beginfor i in 0 to 3 loopcase din((4*i+3) downto (4*i)) iswhen "0000"=>dout((7*i+6) downto (7*i))<="0111111";when "0001"=>dout((7*i+6) downto (7*i))<="0000110";when "0010"=>dout((7*i+6) downto (7*i))<="1011011";when "0011"=>dout((7*i+6) downto (7*i))<="1001111";when "0100"=>dout((7*i+6) downto (7*i))<="1100110";when "0101"=>dout((7*i+6) downto (7*i))<="1101101";when "0110"=>dout((7*i+6) downto (7*i))<="1111101";when "0111"=>dout((7*i+6) downto (7*i))<="0000111";when "1000"=>dout((7*i+6) downto (7*i))<="1111111";when "1001"=>dout((7*i+6) downto (7*i))<="1101111";when others=>NULL;end case;end loop;end process;end architecture one;6、元件例化总电路library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity freq_counter isport(clockin,freq:in std_logic;cout:out std_logic;dout:out std_logic_vector(27 downto 0));end entity freq_counter;architecture one of freq_counter iscomponent clock isport(clk1Hz:in std_logic;rst,en,lock:out std_logic);end component clock;component cnt4_10 isport(clkin,rst,en:in std_logic;count:out std_logic;q:out std_logic_vector(15 downto 0));end component cnt4_10;component reg16 isport(lockin:in std_logic;din:in std_logic_vector(15 downto 0);dout:out std_logic_vector(15 downto 0));end component reg16;component shuma isport(din:in std_logic_vector(15 downto 0);dout:out std_logic_vector(27 downto 0));end component shuma;signal temp0,temp1,temp2:std_logic;signal temp3,temp4:std_logic_vector(15 downto 0);beginu1:clock port map(freq,temp0,temp1,temp2);u2:cnt4_10 port map(clockin,temp0,temp1,cout,temp3);u3:reg16 port map(temp2,temp3,temp4);u4:shuma port map(temp4,dout);end architecture one;四、电路的仿真、结果及分析当程序设计完成之后,新建波形文件仿真如下:其中:freq表示外部提供的基准时钟信号,频率为1Hz;clockin表示外部待测信号频率,输入值范围0~9999Hz;cout表示计数溢出标志,当计数器完成一轮计数后自动置1;dout表示输出信号,总共28路(每7路接一个数码管,总共可以接4个数码管),分别对应显示输入信号频率的千、百、十、个位从图中可以看出:当clockin输入值为1000Hz时,dout输出0000110011111101111110111111即:1000当clockin输入值为500Hz时,dout输出0111111110110101111110111111即:0500当clockin输入值为200Hz时,dout输出0111111101101101111110111111即:0200输出结果是正确的,和输入应该得到的结果一致,表明程序设计基本没有问题。

南通大学毕业设计(论文)摘要数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

采用FPGA现场可编程门阵列为控制核心,通过硬件描述语言VHDL编程,在QuartusII仿真平台上编译、仿真、调试,并下载到FPGA芯片上,通过严格的测试后,能够较准确地测量方波、正弦波、三角波、矩齿波等各种常用的信号的频率,而且还能对其他多种物理量进行测量。

关键词:硬件描述语言.现场可编程门阵列, 频率计, 频率测量ABSTRACTDigital frequency meter is a digital circuit in a typical application, the actual hardware design of devices used in more complicated connection, but will have relatively large delay, caused by measurement error, poor reliability. With the FPGA field programmable gate array a wide range of applications to the development of EDA tools as a means of using the VHDL hardware description language such as language, will greatly simplify the whole system to improve overall system performance and reliability.The use of field programmable gate array FPGA for the control of the core, through the VHDL hardware description language programming, in QuartusII compiled simulation platform, simulation, debugging, and downloaded to the FPGA chip, through rigorous testing, to more accurately measure square wave, sine wave, triangle wave, moment-tooth wave signals such as the frequency of commonly used, but also a variety of other physical measurements..Key words:VHDL, FPGA, the cymometer ,the frequency measurement目录摘要 (I)ABSTRACT .................................................................................................................. I I摘要 (I)ABSTRACT ............................................ I I前言 (1)第一章 FPGA及VHDL (2)1.1 FPGA简介 (2)1.2 EP1K 30相关说明 (2)(5)具有实现快速加法器和计数器的专用进位链和实现高速、多输入逻辑函数的专用级连链。

FPGA 实验报告

题目:4位十进制频率计设计

一、实验目的:

设计4位十进制频率计,学习较复杂的数字系统设计方法。

二、原理说明:

根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清0信号。

这清0个信号可以由一个测频控制信号发生器产生,即图5-1中的TESTCTL ,它的设计要求是,TESTCTL 的计数使能信号CNT_EN 能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的EN 使能端进行同步控制。

当CNT_EN 高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,首先需要一个锁存信号LOAD 的上跳沿将计数器在前1秒钟的计数值锁存进各锁存器REG4B 中,并由外部的7段译码器译出,显示计数值。

设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT 对计数器进行清零,为下1秒钟的计数操作作准备。

三、实验步骤.

1.在QUARTUSII 软件下创建一工程,工程名为frequency ,芯片名为EP2C35F672C6;

2.输入10进制计数器模块,用于计算分频结果,并连接数码管显示。

将其命名为cnt10d.v ,然后保存在与工程相同的文件夹中;

其功能和时序仿真波形分别如下:

module cnt10d(clk,rst,en,cq,cout);

input clk;

input rst; input en; output[3:0] cq; output cout; reg[3:0] cq;

reg cout;

always@(posedge clk or posedge rst)

begin

if(rst) cq<=4'b0000; else if(en) begin if(cq<9)

begin cq<=cq+1'b1;cout<=1'b0; end

else begin cq<=4'b0000; cout<=1'b1; end end end endmodule

分析:由波形可知,当rst为高时,cq为0,当en为高时,cq开始计数,可知结果正确。

3.输入测频控制器模块,使得频率计能自动测频,将其命名为testctl.v,然后保存在与工程相同的文件夹中。

module testctl(clkk,cnt_en,rst_cnt,load);

input clkk; // 1HZ

output cnt_en;

output rst_cnt;

output load;

reg div2clk;

wire cnt_en;

reg rst_cnt;

wire load;

always@(posedge clkk)

div2clk<=~div2clk; always @(clkk or div2clk) begin

if(!clkk & !div2clk)

rst_cnt<=1'b1;

else rst_cnt<=1'b0;

end

assign load = ~div2clk;

assign cnt_en = div2clk; endmodule

其功能和时序仿真波形分别如下:

4.输入锁存器模块,将频率计的每位数锁存后输出,并将其命名为reg4.v,,保存.

module reg4(clk,cq,led );

input clk;

input[3:0] cq;

output[3:0] led;

reg[3:0] led;

always@(posedge clk)

led<=cq;

endmodule

其功能和时序仿真波形分别如下:

波形分析:由波形可知,当clk有效时,cq的值被锁存后,由led输出,由此可得,结果正确。

5.输入产生测频器的clk(8Hz)d的分频模块并将其命名为div_50.v,保存.

module div_50(clk2,Q2);

input clk2;

output Q2;

reg Q2;

reg[23:0] count;

always @(posedge clk2)begin

if(count==4999999) count<=0;else

count<=count+2'b1;end always @(count)begin

if(count==4999999)

Q2<=1;else

Q2<=0;end

endmodule

endmodule

6.输入f_in (频率任意定)时钟模块,用于连接在DE2上进行测试。

并将其命名为div_2

7.v ,保存.

7.输入数码管显示模块并将其命名为decl7s.v ,保存.

其仿真波形如下所示:

module div_27(clk1,Q1); input clk1;

output Q1; reg Q1; reg[27:0] count; always @(posedge clk1)begin if(count==53999999)

count<=0;else count<=count+2'b1;end

end always @(count)begin if(count==53999999) Q1<=1; else Q1<=0;end endmodule module decl7s(a,led7s ); input[3:0] a; output[6:0] led7s; reg[6:0] led; always@(a) begin

case(a)

4'b0000:led[6:0]=7'b1000000;

4'b0001:led[6:0]=7'b1111001;

4'b0010:led[6:0]=7'b0100100; 4'b0011:led[6:0]=7'b0110000; 4'b0100:led[6:0]=7'b0011001; 4'b0101:led[6:0]=7'b0010010; 4'b0110:led[6:0]=7'b0000010; 4'b0111:led[6:0]=7'b1111000; 4'b1000:led[6:0]=7'b0000000; 4'b1001:led[6:0]=7'b0011000;

default:led[6:0]=7'b1111111;

endcase

end

assign led7s=led; endmodule

8.

用原理图方式将各模块连接起来

9.锁定引脚后,重编译,然后下载。

观察到EDA上数码管显示2000,结果正确。

四.思考题.

将频率计扩展为8位十进制频率计,并在测频速度上给予优化,使其能测出更高的频率。

module cnt10d(clk,rst,en,cq,cout);

input clk;

input rst;

input en;

output[7:0] cq;

output cout;

reg[7:0] cq;

reg cout;

always@(posedge clk or posedge rst) begin

if(rst) cq<=8'b00000000;

else

if(en) begin

if(cq<9)

begin cq<=cq+1'b1;cout<=1'b0; end else begin cq<=8'b00000000;

cout<=1'b1; end

end

end

endmodule。