数字电子技术第一章

- 格式:ppt

- 大小:4.71 MB

- 文档页数:97

第一章数字电子技术概述随着信息时代的到来,“数字”这两个字正以越来越高的频率出现在各个领域,数字手表、数字电视、数字通信、数字控制……数字化已成为当今电子技术的发展潮流。

数字电路是数字电子技术的核心,是计算机和数字通信的硬件基础。

本章首先介绍数字电路的一些基本概念及数字电路中常用的数制与码;然后讨论数字电路中二极管、三极管的工作方式;最后介绍数字逻辑中的基本逻辑运算、逻辑函数及其表示方法。

从现在开始,你将跨入数字电子技术这一神奇的世界,去探索它的奥秘,认识它的精彩。

1.1 数字电路的基本概念一.模拟信号和数字信号电子电路中的信号可以分为两大类:模拟信号和数字信号。

模拟信号——时间连续、数值也连续的信号。

数字信号——时间上和数值上均是离散的信号。

(如电子表的秒信号、生产流水线上记录零件个数的计数信号等。

这些信号的变化发生在一系列离散的瞬间,其值也是离散的。

)数字信号只有两个离散值,常用数字0和1来表示,注意,这里的0和1没有大小之分,只代表两种对立的状态,称为逻辑0和逻辑1,也称为二值数字逻辑。

数字信号在电路中往往表现为突变的电压或电流,如图1.1.1所示。

该信号有两个特点:(1)信号只有两个电压值,5V和0V。

我们可以用5V来表示逻辑1,用0V来表示逻辑0;当然也可以用0V来表示逻辑1,用5V来表示逻辑0。

因此这两个电压值又常被称为逻辑电平。

5V为高电平,0V为低电平。

(2)信号从高电平变为低电平,或者从低电平变为高电平是一个突然变化的过程,这种信号又称为脉冲信号。

二.正逻辑与负逻辑如上所述,数字信号是一种二值信号,用两个电平(高电平和低电平)分别来表示两个逻辑值(逻辑1和逻辑0)。

那么究竟是用哪个电平来表示哪个逻辑值呢?两种逻辑体制:(1)正逻辑体制规定:高电平为逻辑1,低电平为逻辑0。

(2)负逻辑体制规定:低电平为逻辑1,高电平为逻辑0。

如果采用正逻辑,图1.1.1所示的数字电压信号就成为如图1.1.2所示逻辑信号。

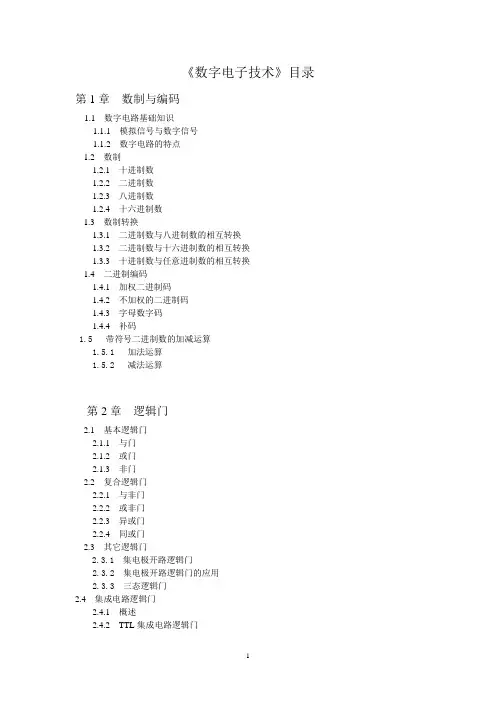

《数字电子技术》目录第1章数制与编码1.1 数字电路基础知识1.1.1 模拟信号与数字信号1.1.2 数字电路的特点1.2 数制1.2.1 十进制数1.2.2 二进制数1.2.3 八进制数1.2.4 十六进制数1.3 数制转换1.3.1 二进制数与八进制数的相互转换1.3.2 二进制数与十六进制数的相互转换1.3.3 十进制数与任意进制数的相互转换1.4 二进制编码1.4.1 加权二进制码1.4.2 不加权的二进制码1.4.3 字母数字码1.4.4 补码1.5带符号二进制数的加减运算1.5.1 加法运算1.5.2 减法运算第2章逻辑门2.1 基本逻辑门2.1.1 与门2.1.2 或门2.1.3 非门2.2 复合逻辑门2.2.1 与非门2.2.2 或非门2.2.3 异或门2.2.4 同或门2.3 其它逻辑门2.3.1 集电极开路逻辑门2.3.2 集电极开路逻辑门的应用2.3.3 三态逻辑门2.4 集成电路逻辑门2.4.1 概述2.4.2 TTL集成电路逻辑门2.4.3 CMOS集成电路逻辑门2.4.4 集成逻辑门的性能参数2.4.5 TTL与CMOS集成电路的接口*第3章逻辑代数基础3.1 概述3.1.1 逻辑函数的基本概念3.1.2 逻辑函数的表示方法3.2 逻辑代数的运算规则3.2.1 逻辑代数的基本定律3.2.2 逻辑代数的基本公式3.2.3 摩根定理3.2.4 逻辑代数的规则3.3 逻辑函数的代数化简法3.3.1 并项化简法3.3.2 吸收化简法3.3.3 配项化简法3.3.4 消去冗余项法3.4 逻辑函数的标准形式3.4.1 最小项与最大项3.4.2 标准与或表达式3.4.3 标准或与表达式3.4.4 两种标准形式的相互转换3.4.5 逻辑函数表达式与真值表的相互转换3.5 逻辑函数的卡诺图化简法3.5.1 卡诺图3.5.2 与或表达式的卡诺图表示3.5.3 与或表达式的卡诺图化简3.5.4 或与表达式的卡诺图化简3.5.5 含无关项逻辑函数的卡诺图化简3.5.6 多输出逻辑函数的化简*第4章组合逻辑电路4.1 组合逻辑电路的分析4.1.1 组合逻辑电路的定义4.1.2 组合逻辑电路的分析步骤4.1.3 组合逻辑电路的分析举例4.2 组合逻辑电路的设计4.2.1 组合逻辑电路的一般设计步骤4.2.2 组合逻辑电路的设计举例4.3 编码器4.3.1 编码器的概念4.3.2 二进制编码器4.3.3 二-十进制编码器4.3.4 编码器应用举例4.4 译码器4.4.1 译码器的概念4.4.2 二进制译码器4.4.3 二-十进制译码器4.4.4 用译码器实现逻辑函数4.4.5 显示译码器4.4.6 译码器应用举例4.5 数据选择器与数据分配器4.5.1 数据选择器4.5.2 用数据选择器实现逻辑函数4.5.3 数据分配器4.5.4 数据选择器应用举例4.6 加法器4.6.1 半加器4.6.2 全加器4.6.3 多位加法器4.6.4 加法器应用举例4.6.5 加法器构成减法运算电路*4.7 比较器4.7.1 1位数值比较器4.7.2 集成数值比较器4.7.3 集成数值比较器应用举例4.8 码组转换电路4.8.1 BCD码之间的相互转换4.8.2 BCD码与二进制码之间的相互转换4.8.3 格雷码与二进制码之间的相互转换4.9 组合逻辑电路的竞争与冒险4.9.1 冒险现象的识别4.9.2 消除冒险现象的方法第5章触发器5.1 RS触发器5.1.1 基本RS触发器5.1.2 钟控RS触发器5.1.3 RS触发器应用举例5.2 D触发器5.2.1 电平触发D触发器5.2.2 边沿D触发器5.3 JK触发器5.3.1 主从JK触发器5.3.2 边沿JK触发器5.4 不同类型触发器的相互转换5.4.1 概述5.4.2 D触发器转换为JK、T和T'触发器5.4.3 JK触发器转换为D触发器第6章寄存器与计数器6.1 寄存器与移位寄存器6.1.1 寄存器6.1.2 移位寄存器6.1.3移位寄存器应用举例6.2 异步N进制计数器6.2.1 异步n位二进制计数器6.2.2 异步非二进制计数器6.3 同步N进制计数器6.3.1 同步n位二进制计数器6.3.2 同步非二进制计数器6.4 集成计数器6.4.1 集成同步二进制计数器6.4.2 集成同步非二进制计数器6.4.3 集成异步二进制计数器6.4.4 集成异步非二进制计数器6.4.5 集成计数器的扩展6.4.6 集成计数器应用举例第7章时序逻辑电路的分析与设计7.1 概述7.1.1 时序逻辑电路的定义7.1.2 时序逻辑电路的结构7.1.3 时序逻辑电路的分类7.2 时序逻辑电路的分析7.2.1时序逻辑电路的分析步骤7.2.2 同步时序逻辑电路分析举例7.2.3 异步时序逻辑电路分析举例7.3 同步时序逻辑电路的设计7.3.1 同步时序逻辑电路的基本设计步骤7.3.2 同步时序逻辑电路设计举例第8章存储器与可编程器件8.1 存储器概述8.1.1 存储器的分类8.1.2 存储器的相关概念8.1.3 存储器的性能指标8.2 RAM8.2.1 RAM分类与结构8.2.2 SRAM8.2.3 DRAM8.3 ROM8.3.1 ROM分类与结构8.3.2 掩膜ROM8.3.3 可编程ROM8.3.4 可编程ROM的应用8.4 快闪存储器(Flash Memory)8.4.1 快闪存储器的电路结构8.4.2 闪存与其它存储器的比较8.5 存储器的扩展8.5.1 存储器的位扩展法8.5.2 存储器的字扩展法8.6 可编程阵列逻辑8.6.1 PAL的电路结构8.6.2 PAL器件举例8.6.3 PAL器件的应用8.7 通用阵列逻辑8.7.1 GAL的性能特点8.7.2 GAL的电路结构8.7.3 OLMC8.7.4 GAL器件的编程与开发8.8 CPLD、FPGA和在系统编程技术8.8.1 数字可编程器件的发展概况8.8.2数字可编程器件的编程语言8.8.3数字可编程器件的应用实例第9章D/A转换器和A/D转换器9.1 概述9.2 D/A转换器9.2.1 D/A转换器的电路结构9.2.2 二进制权电阻网络D/A转换器9.2.3 倒T型电阻网络D/A转换器9.2.4 D/A转换器的主要技术参数9.2.5 集成D/A转换器及应用举例9.3 A/D转换器9.3.1 A/D转换的一般步骤9.3.2 A/D转换器的种类9.3.3 A/D转换器的主要技术参数9.3.4 集成A/D转换器及应用举例第10章脉冲波形的产生与整形电路10.1 概述10.2 多谐振荡器10.2.1 门电路构成的多谐振荡器10.2.2 采用石英晶体的多谐振荡器10.3 单稳态触发器10.3.1 门电路构成的单稳态触发器10.3.2 集成单稳态触发器10.3.3 单稳态触发器的应用10.4 施密特触发器10.4.1 概述10.4.2 施密特触发器的应用10.5 555定时器及其应用10.5.1 电路组成及工作原理10.5.2 555定时器构成施密特触发器10.5.3 555定时器构成单稳态触发器10.5.4 555定时器构成多谐振荡器第11章数字集成电路简介11.1 TTL门电路11.1.1 TTL与非门电路11.1.2 TTL或非门电路11.1.3 TTL与或非门电路11.1.4 集电极开路门电路与三态门电路11.1.5 肖特基TTL与非门电路11.2 CMOS门电路11.2.1 概述11.2.2 CMOS非门电路11.2.3 CMOS与非门电路11.2.4 CMOS或非门电路11.2.5 CMOS门电路的构成规则11.3 数字集成电路的使用。