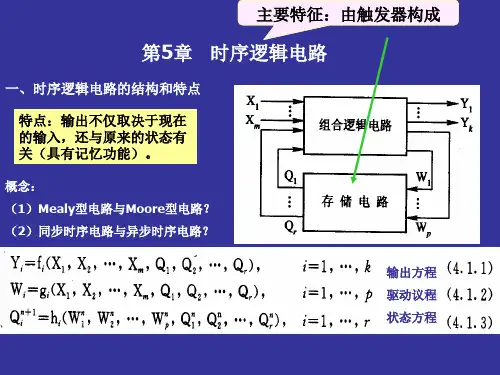

数字电子技术基础第五版 第五章

- 格式:ppt

- 大小:3.29 MB

- 文档页数:45

第五章-第六章习题习题一1、由与非门组成的基本SR锁存器,输入端分别为S、R为使锁存器处于“置1”状态,其S、R端应为。

(A)SR=00 (B)SR=01 (C)SR=10 (D)SR=112、有一个T触发器,在T=1 时,加上时钟脉冲,则触发器。

(A)保持原态(B)置0 (C)置1 (D)翻转3、假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

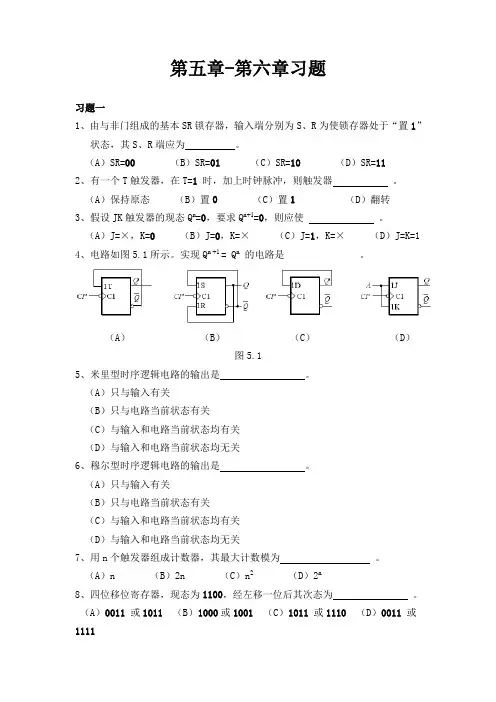

(A)J=×,K=0 (B)J=0,K=×(C)J=1,K=×(D)J=K=1 4、电路如图5.1所示。

实现Q n +1 = Q n的电路是。

(A)(B)(C)(D)图5.15、米里型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关6、穆尔型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关7、用n个触发器组成计数器,其最大计数模为。

(A)n (B)2n (C)n2(D)2n8、四位移位寄存器,现态为1100,经左移一位后其次态为。

(A)0011 或1011 (B)1000或1001 (C)1011 或1110 (D)0011 或11119、下列电路中,不属于时序逻辑电路的是。

(A)计数器(B)全加器(C)寄存器(D)分频器10、一个5 位的二进制加计数器,由00000 状态开始,经过75个时钟脉冲后,此计数器的状态为:(A)01011 (B)01100 (C)01010 (D)00111 11、图5.2所示为某时序电路的时序图,由此可知该时序电路具有的功能。

(A)十进制计数器(B)九进制计数器(C)四进制计数器(D)八进制计数器图5.2习题二5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号;与电路原来所处的状态;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号;与信号作用前电路原来所处的状态。

第五章部分习题解答5.8S a =0011 , S b =1001 , S a ^ S b T S a 计数循环共有7个状态,故此电路是七进制计数器。

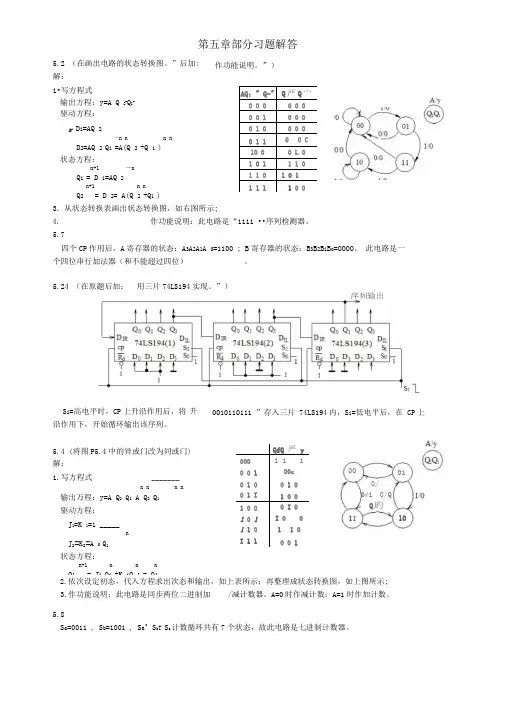

5.2 (在画出电路的状态转换图。

”后加:解:作功能说明。

”)1•写方程式输出方程:y=A Q 2nQ 1n驱动方程:r D i =AQ 2—n nn nD 2=AQ 2 Q i =A(Q 2 +Q i ) 状态方程:n+1 —nQ i = D i =AQ 2 n+1n nQ 2= D 2= A(Q 2 +Q 1 )AQ :" Q-" Q 严Q 宀0 0 0 0 0 0 0 0 1 0 0 0 0 1 00 0 0 0 1 1 0 0 C 10 0 0 L 0 1 0 1 1 1 0 1 1 01 0 1 1 1 11 0 03. 从状态转换表画出状态转换图,如右图所示;4. 作功能说明:此电路是 “1111 ••序列检测器。

5.7四个CP 作用后,A 寄存器的状态:A 3A 2A 1A 0=1100 ; B 寄存器的状态:B 3B 2B i B o =OOOO 。

此电路是一个四位串行加法器(和不能超过四位) 。

5.24 (在原题后加: 用三片74LS194实现。

”)S i =高电平时,CP 上升沿作用后,将 升沿作用下,开始循环输出该序列。

0010110111 ”存入三片 74LS194内,S i =低电平后,在 CP 上5.4 (将图P5.4中的异或门改为同或门) 解: 1.写方程式_______n nn n输出万程:y=A Q 2 Q 1 A Q 2 Q 1 驱动方程: J 1=K 1=1 _____nJ 2=K 2=A O Q 1状态方程:n+1nnnQ 1 = J i Q i +K i Q 1 = Q 1QfQ 严 y000 i 110 0 1 00c0 1 0 0 1 0 0 1 I 1 0 0 1 0 00 I 0 1 0 1I 01 1 01 1 0 I 1 10 0 12.依次设定初态,代入方程求出次态和输出,如上表所示;再整理成状态转换图,如上图所示;3.作功能说明:此电路是同步两位二进制加/减计数器。

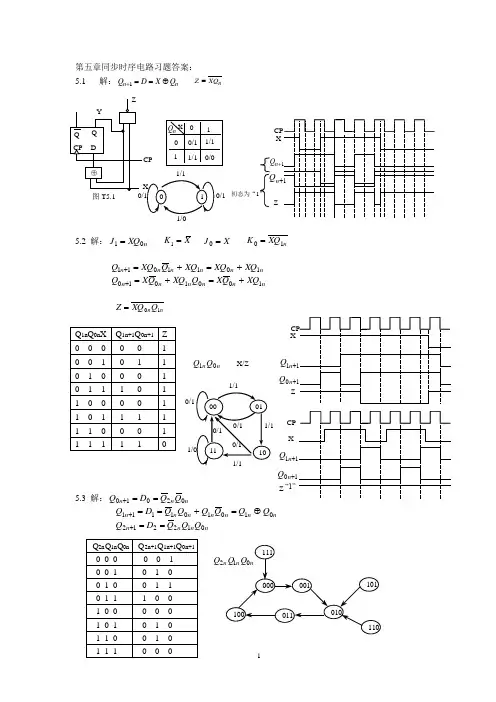

第五章同步时序电路习题答案: 5.1 解:n n Q X D Q ⊕==+1 n XQ Z =5.2 解:n XQ J 01= X K =1 X J =0 n XQ K 10=n n n n n n XQ XQ XQ Q XQQ 1011011+=+=+ n n n n n n XQ Q X Q XQ Q X Q 1001010+=+=+ n n Q XQ Z 10=5.3 解:n n n Q Q D Q 02010==+n n n n n n n Q Q Q Q Q Q D Q 010101111⊕=+==+ n n n n Q Q Q D Q 012212==+1/1 0/1 X 011 0/1 1/1 1/1 0/0n Q+n n Q Z初态为“1”nn Q Q 01X/ZX1+n Q 0+n Q ZX1+n Q 0+n Q Z “1”Q 212+n Q逻辑功能:可自启动的同步五进制加法计数器。

5.45.55.6 解:(1)当X 1X 2=“00”;初始状态为“00”时:112=+n Q 121==n Q J 1111==X J Kn n Q Q 111=+逻辑功能:电路实现2分频。

(2)当X 1X 2=“01”;初始状态为“00”时:n Q J 21= 1111==X J K n n n Q Q Q 1211=+n Q J 12= 1112==X Q K n n n n Q Q Q 1212=+ 逻辑功能: 电路实现3分频。

(3)当X 1X 2=“11”;初始状态为“00”时: n Q J 21= n Q X J K 2111==n n n n n n Q Q Q Q Q Q 2121211=+=+ n Q J 12= n n Q X Q K 1112== n n n n n n Q Q Q Q Q Q 1212112=+=+ 逻辑功能: 电路实现4分频。

Y 3 Y 2 Y 1 Y 0n n n Q Q Q J 1234= n Q K 14= n n Q Q J 143= n n Q Q K 123= n n n Q Q Q J 1342= n Q K 12= 111==K Jn n n n n n n Q Q Q Q Q Q Q 14123414+=+ n n n n n n n Q Q Q Q Q Q Q 31213413)(++=+ n n n n n n n Q Q Q Q Q Q Q 12123412)(++=+ 14+n QCP13+n Q 12+n Q 11+n QZn n Q Q 111=+n n n n Q Q Q Q Z 1234= 时序图:11+n Q12+n Q 11+n Q11+n Q12+n Q5.7 (1)(2)Q D 端输出是12分频,占空比是50%。

数字电子技术基础阎石第五版课后答案第一章:引言1.数字电子技术是现代电子技术的基础,它是将模拟电子技术应用到数字系统中的学科。

数字电子技术的发展对计算机技术、通信技术等领域起到了重要的推动作用。

2.数字电子技术的基本概念包括数字信号、模拟信号、信号采样、量化、编码等。

3.数字电子技术的应用广泛,涵盖数字计算机、数字通信、数字音频、数字视频等多个领域。

第二章:数字逻辑基础1.逻辑代数是数字电子技术的基础,它包括逻辑运算、逻辑表达式、逻辑函数等概念。

2.逻辑代数的基本运算包括与运算、或运算、非运算等。

3.逻辑函数可以用真值表、卡诺图等形式表示。

4.数字逻辑电路是由逻辑门组成的,常见的逻辑门有与门、或门、非门等。

5.在数字逻辑电路中,还有多种逻辑门的组合形式,如与或非门、与非门等。

第三章:组合逻辑电路1.组合逻辑电路是由多个逻辑门组成的电路,逻辑门的输入和输出之间没有时钟信号的约束。

2.组合逻辑电路的设计过程包括确定所需逻辑关系、选择合适的逻辑门、进行逻辑门的连线等。

3.组合逻辑电路常见的应用有加法器、减法器、译码器、多路选择器等。

4.确定组合逻辑电路的最小项和最大项是一种常用的设计方法。

5.组合逻辑电路可以用Karnaugh图来进行化简和优化。

第四章:时序逻辑电路1.时序逻辑电路是由组合逻辑电路和触发器组成的电路,触发器引入了时钟信号来控制电路的状态。

2.触发器的种类有RS触发器、D触发器、JK触发器等。

3.时序逻辑电路中常见的电路有时钟发生器、计数器、寄存器等。

4.时序逻辑电路在数字系统中起到了重要的作用,可以实现状态的存储和传输。

5.时序逻辑电路的设计需要考虑时序条件、逻辑功能、触发器的选择等因素。

第五章:数字系统的设计1.数字系统的设计包括功能设计和硬件设计两个方面。

2.功能设计是根据系统的需求,确定系统所完成的功能和算法。

3.硬件设计是根据功能设计,选择合适的逻辑门、触发器等器件,进行电路图的设计。

第5章 触发器5.1 画出图5-1由与非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D ′、R D ′的电压波形如图中所示。

图5-1解:波形图如图5-2所示。

图5-25.2 画出图5-3由或非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D 、R D 的电压波形如图中所示。

图5-3解:波形图如图5-4所示。

图5-45.3 试分析图5-5所示电路的逻辑功能,列出真值表,写出逻辑函数式。

图5-5解:当CLK=0时,S、R的值不能加到或非门,此时Q的状态保持不变。

当CLK=1时,Q的状态随SR的不同而发生变化,真值表如表5-1所示。

表5-1卡诺图如图5-6所示。

图5-6化简得n1+=+Q S R'QSR=。

5.4 图5-7所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,S D′和R D′的电压波形如图中所示,试画出Q、Q′端对应的电压波形。

图5-7解:Q 、Q′端对应的电压波形如图5-8所示。

图5-85.5 在图5-9所示电路中,若CLK 、S 、R的电压波形如图中所示,试画出Q 和Q′端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图5-9解:当CLK =0时,SR 的值不能加到或非门,此时Q 的状态保持不变。

当CLK =1时,成为与非门组成的SR 触发器。

Q 和Q′端对应的电压波形如图5-10所示。

图5-105.6 若将电平触发SR 触发器的Q 与R 、Q′与S 相连,如图5-11所示,试画出在CLK 信号作用下Q 和Q′端的电压波形。

已知CLK 信号的宽度t W =4t pd 。

t pd 为门电路的平均传输延迟时间,假定t pd ≈t PHL≈t PLH 。

设触发器的初始状态为Q =0。

图5-11解:当CLK =0时,触发器输出保持不变;当CLK =1时,输出随SR 触发器变化。

脉冲的上升沿到来时,S =1,经过G 1门和G 3门的时延,Q 被置1;同时,经过G 2门的时延,G 2门输出为1。

数电课程各章重点第一、二章逻辑代数基础知识要点各种进制间的转换,逻辑函数的化简。

一、二进制、十进制、十六进制数之间的转换;二进制数的原码、反码和补码 .8421码二、逻辑代数的三种基本运算以及5种复合运算的图形符号、表达式和真值表:与、或、非三、逻辑代数的基本公式和常用公式、基本规则逻辑代数的基本公式逻辑代数常用公式:吸收律:A+A=AB消去律:BBAAB=++AABAA+=多余项定律:CAB+=+A+CABABC反演定律:BA•+=BAAB+=BA基本规则:反演规则和对偶规则,例1-5四、逻辑函数的三种表示方法及其互相转换逻辑函数的三种表示方法为:真值表、函数式、逻辑图会从这三种中任一种推出其它二种,详见例1-7五、逻辑函数的最小项表示法:最小项的性质;例1-8六、逻辑函数的化简:要求按步骤解答1、利用公式法对逻辑函数进行化简2、利用卡诺图对逻辑函数化简3、具有约束条件的逻辑函数化简例1.1 利用公式法化简BD++F+=()ABCD+BDCABCAA解:BD C D A B A C B A ABCD F ++++=)(例1.2 利用卡诺图化简逻辑函数 ∑=)107653()(、、、、m ABCD Y 约束条件为∑8)4210(、、、、m 解:函数Y 的卡诺图如下:第三章 门电路知识要点各种门的符号,逻辑功能。

一、三极管开、关状态1、饱和、截止条件:截止:T be V V <, 饱和:βCSBS B I I i =>2、反相器饱和、截止判断 二、基本门电路及其逻辑符号与门、或非门、非门、与非门、OC 门、三态门、异或; 传输门、OC/OD 门及三态门的应用 三、门电路的外特性1、输入端电阻特性:对TTL 门电路而言,输入端通过电阻接地或低电平时,由于输入电流流过该电阻,会在电阻上产生压降,当电阻大于开门电阻时,相当于逻辑高电平。

习题2-7 5、输出低电平负载电流I OL 6、扇出系数N O一个门电路驱动同类门的最大数目第四章 组合逻辑电路知识要点组合逻辑电路的分析、设计,利用集成芯片实现逻辑函数。