数电第五版(阎石)第五章课后习题及答案pptx

- 格式:pptx

- 大小:786.75 KB

- 文档页数:27

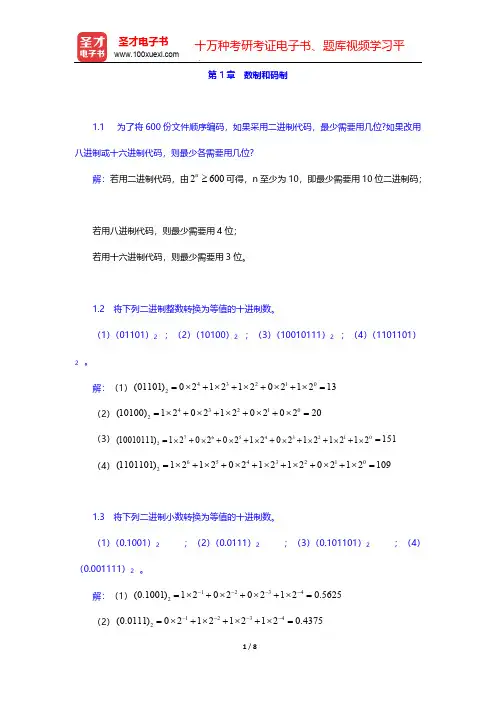

自我检查题5.1 时序电路和组合电路的根本区别是什么?同步时序电路与异步时序电路有何不同?解答:从功能上看,时序电路任何时刻的稳态输出不仅和该时刻的输入相关,而且还决定于该时刻电路的状态,从电路结构上讲,时序电路一定含有记忆和表示电路状态的存储器。

而组合电路任何时刻的稳态输出只决定于该时刻各个输入信号的取值,由常用门电路组成则是其电路结构的特点。

在同步时序电路中,各个触发器的时钟信号是相同的,都是输入CP 脉冲,异步时序电路则不同,其中有的触发器的时钟信号是输入cp 脉冲,有的则是其他触发器的输出,前者触发器的状态更新时同步的,后者触发器状态更新有先有后,是异步的。

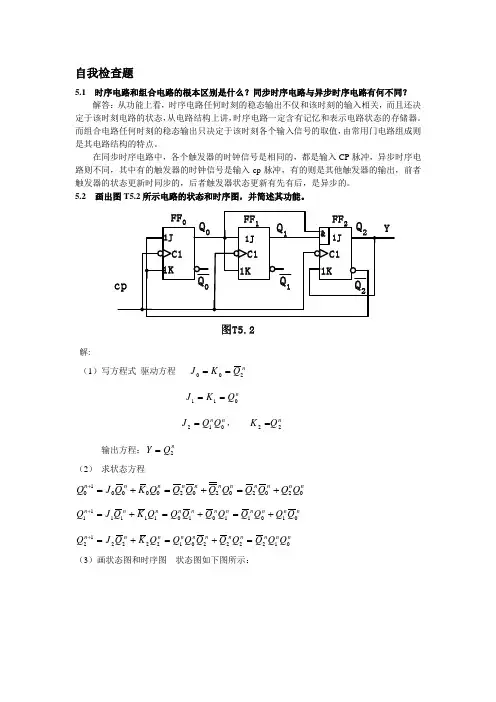

5.2 画出图T5.2所示电路的状态和时序图,并简述其功能。

图T5.2解:(1)写方程式 驱动方程 nQ K J 200==n Q K J 011==n n Q Q J 012=, n Q K 22=输出方程:nQ Y 2= (2) 求状态方程nn n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 02020202000010+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01011010111111+=+=+=+ n n n n n n n n n n n Q Q Q Q Q Q Q Q Q K Q J Q 01222201222212=+=+=+(3)画状态图和时序图 状态图如下图所示:101时序图如下图所示:CP Q 0Q 1Q 25.3 试用边沿JK 触发器和门电路设计一个按自然态序进行计数的七进制同步加法计数器。

解:(1)状态图如下图:(2)求状态方程、输出方程CQ Q Q n n n /101112+++的卡诺图如下图所示:输出方程为nn Q Q C 12=状态方程:n n n n n Q Q Q Q Q 120112+=+ n n n n n n Q Q Q Q Q Q 0120111+=+ n n n n n Q Q Q Q Q 120110+=+驱动方程:n n n n n n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 0122120121220112)(++=++=+n n n n n n Q Q Q Q Q Q 1021011+=+n n n n n Q Q Q Q Q 0012101)(++=+与JK 触发器的特性方程 比较,可以得到驱动方程 n n Q Q J 012= 、 n Q K 12=n Q J 01= 、n n Q Q K 021=n n n n Q Q Q Q J 12120=+= 10=K(4) 无效状态转换情况 111/1000 能自启动(5) 逻辑图如下图所示:5.4 画出用时钟脉冲上升沿触发的边沿D 触发器组成的4位二进制异步加法计数器和减法计数器的逻辑电路图。

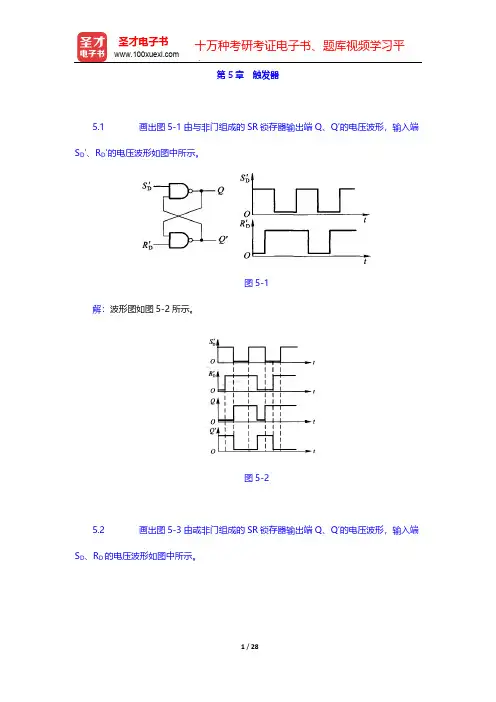

第5章 触发器5.1 画出图5-1由与非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D ′、R D ′的电压波形如图中所示。

图5-1解:波形图如图5-2所示。

图5-25.2 画出图5-3由或非门组成的SR 锁存器输出端Q 、Q′的电压波形,输入端S D 、R D 的电压波形如图中所示。

图5-3解:波形图如图5-4所示。

图5-45.3 试分析图5-5所示电路的逻辑功能,列出真值表,写出逻辑函数式。

图5-5解:当CLK=0时,S、R的值不能加到或非门,此时Q的状态保持不变。

当CLK=1时,Q的状态随SR的不同而发生变化,真值表如表5-1所示。

表5-1卡诺图如图5-6所示。

图5-6化简得n1+=+Q S R'QSR=。

5.4 图5-7所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,S D′和R D′的电压波形如图中所示,试画出Q、Q′端对应的电压波形。

图5-7解:Q 、Q′端对应的电压波形如图5-8所示。

图5-85.5 在图5-9所示电路中,若CLK 、S 、R的电压波形如图中所示,试画出Q 和Q′端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图5-9解:当CLK =0时,SR 的值不能加到或非门,此时Q 的状态保持不变。

当CLK =1时,成为与非门组成的SR 触发器。

Q 和Q′端对应的电压波形如图5-10所示。

图5-105.6 若将电平触发SR 触发器的Q 与R 、Q′与S 相连,如图5-11所示,试画出在CLK 信号作用下Q 和Q′端的电压波形。

已知CLK 信号的宽度t W =4t pd 。

t pd 为门电路的平均传输延迟时间,假定t pd ≈t PHL≈t PLH 。

设触发器的初始状态为Q =0。

图5-11解:当CLK =0时,触发器输出保持不变;当CLK =1时,输出随SR 触发器变化。

脉冲的上升沿到来时,S =1,经过G 1门和G 3门的时延,Q 被置1;同时,经过G 2门的时延,G 2门输出为1。

第5章 习题解答5-1 由与非门组成的大体RS 触发器的d d S ,R 之间什么缘故要有约束?当违背约束条件时,输出端Q 、Q 会显现什么情形?试举例说明。

解:由与非门组成的大体RS 触发器的d R 和d S 之间的约束条件是:不许诺d R 和d S 同时为0。

当违背约束条件即当d R =d S =0时,Q 、Q 端将同时为1,作为大体存储单元来讲,这既不是0状态,又不是1状态,没成心义。

5-2 试列出或非门组成的大体RS 触发器的真值表,它的输入端R d 和S d 之间是不是也要有约束?什么缘故?解:真值表如右表所示、Rd 、Sd 之同也要有约束条件,即不许诺Rd=Sd=1, 不然Q 、Q 端会同时显现低电平。

5-3 画出图5-33由与非门组成的大体RS 触发器输出端Q 、Q 的电压波形,输入端D D S R 、的电压波形如图中所示。

图5-33解:见以下图:5-4 画出图5-34由或非门组成的大体RS触发器输出端Q、Q的电压波形,输入端S D、R D的电压波形如图中所示。

图5-34解:见以下图:5-5 图5-35所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通R S、的电压波形如图中所示。

试画出Q、Q端对应的电压波形。

刹时发生振颤,D D图5-35解:见以下图:5-6 在图5-36电路中、假设CP、S、R的电压波形如图中所示,试画出Q、Q端与之对应的电压波形。

假定触发器的初始状态为Q=0。

图5-36解:见以下图:5-7 在图5-37(a)所示的主从RS触发器中,CP、R、S的波形如图5-37(b)所示,试画Q、Q和Q的波形图。

出相应的Q m、m图5-37解:主从RS触发器的工作进程是:在CP=l期间主触发器接收输入信号,但输出端并非改变状态,只有当CP下降沿到来时从触发器甚才翻转,称为下降沿触发。

依照主从RS 触发器状态转换图可画出波形图如下图所示。

5-8 在图5-38(a)所示的主从JK触发器中,CP、J、K的波形如图5-38(b)所示,试画Q、Q和Q的波形图。