数字系统设计基础 (8)

- 格式:ppt

- 大小:3.66 MB

- 文档页数:233

实验八同步时序电路逻辑设计一、实验目的:1.掌握同步时序电路逻辑设计过程。

2.掌握实验测试所设计电路的逻辑功能。

3.学习EDA软件的使用。

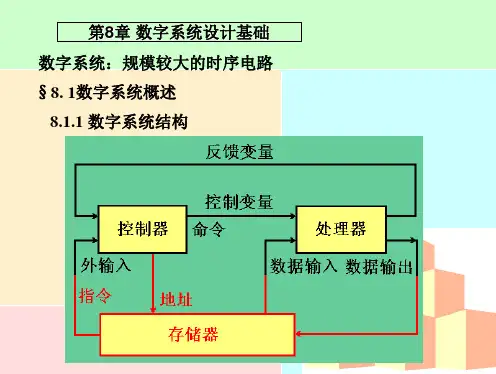

二、实验仪器:序号仪器或器件名称型号或规格数量1 逻辑实验箱 12 万用表 13 双踪示波器 14 74LS194 15 74LS112 16 74LS04 17 74LS00 18 74LS86 19 74LS10 1三、实验原理:同步时序电路逻辑设计过程方框图如图8-1所示。

设计要求状态转移图状态转移表状态化简状态分配选择触发器激励方程、输出方程逻辑电路图8-1其主要步骤有:1.确定状态转移图或状态转移表根据设计要求写出状态说明,列出状态转移图或状态转移表,这是整个逻辑设计中最困难的一步,设计者必须对所需要解决的问题有较深入的理解,并且掌握一定的设计经验和技巧,才能描绘出一个完整的、较简单的状态转移图或状态转移表。

2.状态化简将原始状态转移图或原始状态转移表中的多余状态消去,以得到最简状态转移图或状态转移表,这样所需的元器件也最少。

3.状态分配这是用二进制码对状态进行编码的过程,状态数确定以后,电路的记忆元件数目也确定了,但是状态分配方式不同也会影响电路的复杂程度。

状态分配是否合理需经过实践检验,因此往往需要用不同的编码进行尝试,以确定最合理的方案。

4.选择触发器通常可以根据实验室所提供的触发器类型,选定一种触发器来进行设计,因为同步时序电路触发器状态更新与时钟脉冲同步,所以在设计时应尽量采用同一类型的触发器。

选定触发器后,则可根据状态转移真值表和触发器的真值表作出触发器的控制输入函数的卡诺图,然后求得各触发器的控制输入方程和电路的输出方程。

5.排除孤立状态理论上完成电路的设计后,还需检查电路有否未指定状态,若有未指定状态,则必须检查未指定状态是否有孤立状态,即无循环状态,如果未指定状态中有孤立状态存在,应采取措施排除,以保证电路具有自启动性能。

经过上述设计过程,画出电路图,最后还必须用实验方法对电路的逻辑功能进行验证,如有问题,再作必要的修改。