数字电路第8章 数字系统设计基础-习题答案

- 格式:pdf

- 大小:362.59 KB

- 文档页数:9

习题8.1.1电路如图所示,试写出输出F 与输入A ,B ,C 的逻辑关系式。

并画出逻辑图。

+20 V -10 VA B图8.01 习题8.1.1的图解:F AB C =+C8.1.2 晶体管非门电路如图所示,已知U CC V =15 ,U B V =-9 ,R C k =3 Ω, R B k =20 Ω, β=40,求:(1) 求晶体管的集电极临界饱和电流I CS 和基极临界饱和电流I BS ;(2)当输 入电压U I V =5时,要使晶体管饱和导通,试求R X 值 (设 U BE V =06.)。

(3)写出它的逻辑符号。

u Iu OA图8.02 习题8.1.2的图 解:(1) I U R I I CS CC C BS CS mA mAmA mA ≈=====15355400125β. (2) 如 图 所 示I I I I U R R I U U R B BE X XBE B BmA =+=-==--'=-12125449620..故 I R ÓB X =+-449620.. 又 I BS mA =0125. 得 R X k =727.ΩEI 1u I(3) 逻 辑 符 号8.1.3 已知逻辑门电路及输入波形如图所示,试画出各输出F 1、F 2、F 3的波形, 并写出逻辑式。

&"1"F 1≥1"0"F 2B ≥1F 3ABCF 1F 2F 3AABC图8.03 习题8.1.3的图解:CF 2F 3F A A 11=⋅=F A B C3=++F B B20=+=AB F 18.1.4 已知逻辑电路及其输入波形如图所示 ,试分别画出输出 F 1,F 2 的波形 。

(a ) (b ) 图8.04 习题8.1.4的图解:F 2F 1图1图2A 1B 1A 2B 28.2.1 某 逻 辑 电 路 的 状 态 表 如 下,其 输 入 变 量 为 A ,B ,C ,输 出 为F ,试 写 A B C F 018(a)(b) 表8.01 习题8.2.1的表解:(a) F ABC =(b)F ABC A B C A B C ==++=++8.2.2 已知逻辑电路输入A ,B ,C 及输出F 的波形如图所示,试分别列出状态表,写出逻辑式,画出逻辑图。

第8章半导体存储器和可编程逻辑器件8-1存储器按读写功能以及信息的可保存性分别分为哪几类?并简述各自的特点。

解答:存储器按读写功能可分为只读存储器(ROM)和随机存储器(RAM)。

随机存取存储器在工作过程中,既可从其任意单元读出信息,又可以把外部信息写入任意单元。

因此,它具有读、写方便的优点,但由于具有易失性,所以不利于数据的长期保存。

只读存储器在正常工作时其存储的数据固定不变,只能读出,不能随时写入。

ROM为非易失性器件,当器件断电时,所存储的数据不会丢失。

存储器按信息的可保存性可分为易失性存储器和非易失性存储器。

易失性存储器在系统关闭时会失去存储的信息,它需要持续的电源供应以维持数据。

非易失存储器在系统关闭或无电源供应时仍能保持数据信息。

8-2什么是SRAM?什么是DRAM?它们在工作原理、电路结构和读/写操作上有何特点?解答:SRAM(Static Random Access Memory)为静态随机存储器,其存储单元是在静态触发器的基础上附加控制电路构成的。

DRAM(Dynamic Random Access Memory)为动态随机存储器,常利用MOS管栅极电容的电荷存储效应来组成动态存储器,为了避免存储信息的丢失,必须定时地对电路进行动态刷新。

SRAM的数据由触发器记忆,只要不断电,数据就能保存,但其存储单元所用的管子数目多,因此功耗大,集成度受到限制。

DRAM一般采用MOS管的栅极电容来存储信息,由于电荷保存时间有限,为避免存储数据的丢失,必须由刷新电路定期刷新,但其存储单元所用的管子数目少,因此功耗小,集成度高。

SRAM速度非常快,但其价格较贵;DRAM的速度比SRAM慢,不过它比ROM 快。

8-3若RAM的存储矩阵为256字⨯4位,试问其地址线和数据线各为多少条?解答:存储矩阵为256字⨯4位的RAM地址线为8根,数据线为4根。

8-4某仪器的存储器有16位地址线,8位数据线,试计算其最大存储容量是多少?解答:最大存储容量为216⨯8=524288=512k bit(位)8-5用多少片256⨯4位的RAM可以组成一片2K⨯8位的RAM?试画出其逻辑图。

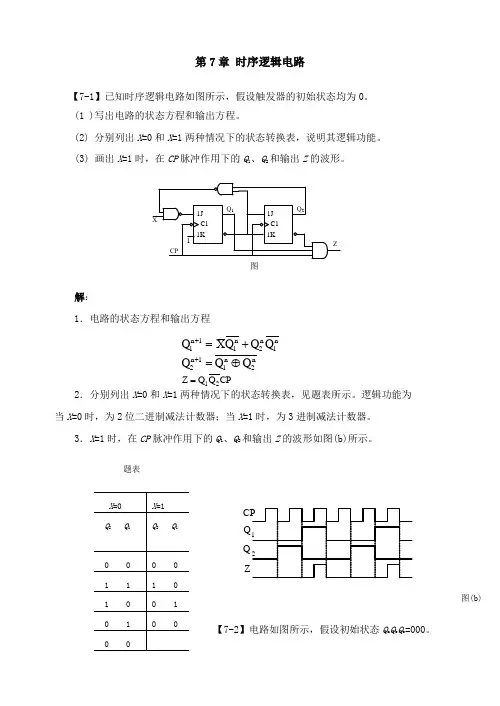

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

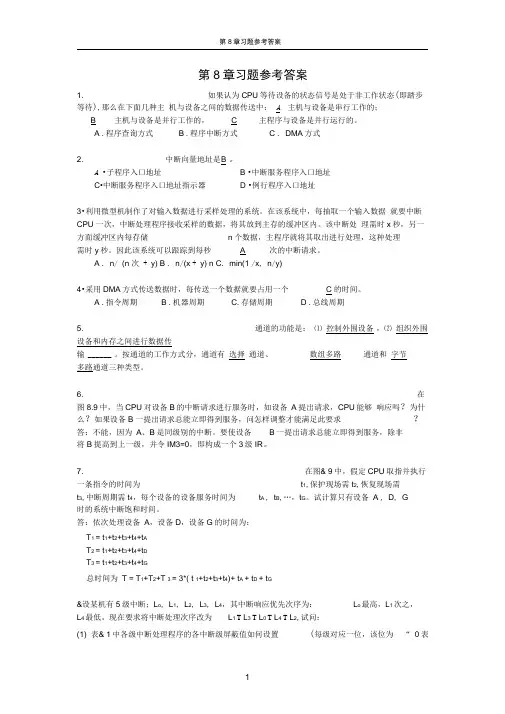

第8章习题参考答案1. 如果认为CPU等待设备的状态信号是处于非工作状态(即踏步等待),那么在下面几种主机与设备之间的数据传送中:A主机与设备是串行工作的;B 主机与设备是并行工作的,C 主程序与设备是并行运行的。

A .程序查询方式B .程序中断方式C . DMA方式2. 中断向量地址是B。

A•子程序入口地址 B •中断服务程序入口地址C•中断服务程序入口地址指示器 D •例行程序入口地址3•利用微型机制作了对输入数据进行采样处理的系统。

在该系统中,每抽取一个输入数据就要中断CPU 一次,中断处理程序接收采样的数据,将其放到主存的缓冲区内。

该中断处理需时x秒,另一方面缓冲区内每存储n个数据,主程序就将其取出进行处理,这种处理需时y秒。

因此该系统可以跟踪到每秒 A 次的中断请求。

A . n/ (n 次 + y)B . n/(x + y) n C. min(1 /x, n/y)4•采用DMA方式传送数据时,每传送一个数据就要占用一个 C 的时间。

A .指令周期B .机器周期C.存储周期 D .总线周期5. 通道的功能是:⑴ 控制外围设备,⑵ 组织外围设备和内存之间进行数据传输______ 。

按通道的工作方式分,通道有选择通道、数组多路通道和字节多路通道三种类型。

6. 在图8.9中,当CPU对设备B的中断请求进行服务时,如设备A提出请求,CPU能够响应吗?为什么?如果设备B 一提出请求总能立即得到服务,问怎样调整才能满足此要求?答:不能,因为A、B是同级别的中断。

要使设备B一提出请求总能立即得到服务,除非将B提高到上一级,并令IM3=0,即构成一个3级IR。

7. 在图& 9中,假定CPU取指并执行一条指令的时间为t1,保护现场需t2,恢复现场需t3,中断周期需t4,每个设备的设备服务时间为t A , t B,…,t G。

试计算只有设备A , D, G时的系统中断饱和时间。

答:依次处理设备A,设备D,设备G的时间为:T1 = t1+t2+t3+t4+t AT2 = t1+t2+t3+t4+t DT3 = t1+t2+t3+t4+t G总时间为T = T1+T2+T 3 = 3*( t 1+t2+t3+t4)+ t A + t D + t G&设某机有5级中断;L o, L1, L2, L3, L4,其中断响应优先次序为:L o最高,L1次之,L4最低。

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a)2K×8位()()()()(b)256×2位()()()()(c)1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有()地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是()。

(a)256×1位(b)256×8位(c)1K×4位(d)2K×1位答案:1. a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

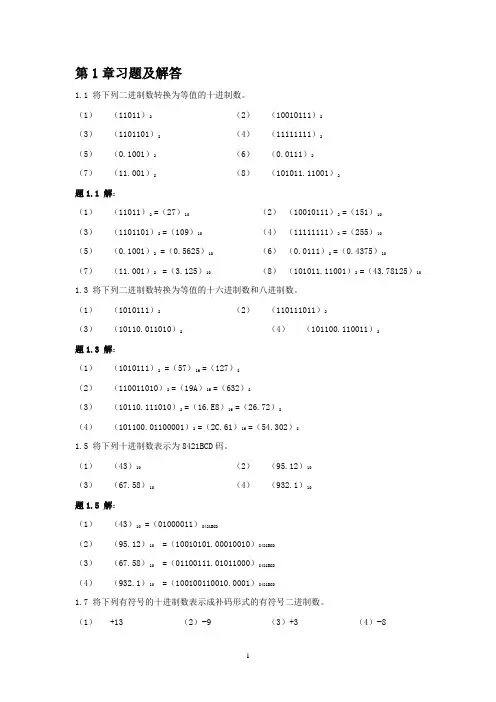

第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)(10010111)2(3)(1101101)2 (4)(11111111)2(5)(0.1001)2(6)(0.0111)2(7)(11.001)2(8)(101011.11001)2题1.1 解:(1)(11011)2 =(27)10 (2)(10010111)2 =(151)10(3)(1101101)2 =(109)10 (4)(11111111)2 =(255)10(5)(0.1001)2 =(0.5625)10(6)(0.0111)2 =(0.4375)10(7)(11.001)2=(3.125)10(8)(101011.11001)2 =(43.78125)10 1.3 将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(110111011)2(3)(10110.011010)2 (4)(101100.110011)2题1.3 解:(1)(1010111)2 =(57)16 =(127)8(2)(110011010)2 =(19A)16 =(632)8(3)(10110.111010)2 =(16.E8)16 =(26.72)8(4)(101100.01100001)2 =(2C.61)16 =(54.302)81.5 将下列十进制数表示为8421BCD码。

(1)(43)10 (2)(95.12)10(3)(67.58)10 (4)(932.1)10题1.5 解:(1)(43)10 =(01000011)8421BCD(2)(95.12)10 =(10010101.00010010)8421BCD(3)(67.58)10 =(01100111.01011000)8421BCD(4)(932.1)10 =(100100110010.0001)8421BCD1.7 将下列有符号的十进制数表示成补码形式的有符号二进制数。

第1章习题及解答将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)()2(3)(1101101)2 (4)()2(5)()2(6)()2(7)()2(8)()2题解:(1)(11011)2 =(27)10 (2)()2 =(151)10(3)(1101101)2 =(109)10 (4)()2 =(255)10(5)()2 =()10(6)()2 =()10(7)()2=()10(8)()2 =()10将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(1)2(3)()2 (4)()2题解:(1)(1010111)2 =(57)16 =(127)8(2)(0)2 =(19A)16 =(632)8(3)()2 =()16 =()8(4)()2 =(2C.61)16 =()8将下列十进制数表示为8421BCD码。

(1)(43)10 (2)()10(3)()10 (4)()10题解:(1)(43)10 =(01000011)8421BCD(2)()10 =(.00010010)8421BCD(3)()10 =()8421BCD(4)()10 =(.0001)8421BCD将下列有符号的十进制数表示成补码形式的有符号二进制数。

(1) +13 (2)−9 (3)+3 (4)−8题解:(1) +13 =(01101)2(2)−9 =(10111)2(3) +3 =(00011)2(4)−8 =(11000)2用真值表证明下列各式相等。

(1)BA+=+B+BBAA(2)()()()=⊕A⊕CACABB(3)()C BA+=+BCA(4)CAB++A=AABC题解:(1)证明BA+=++BABBA(2)证明()()()ACABCBA⊕=⊕(3)证明()C BACBA+=+(4)证明CAB++=AACBA用逻辑代数公式将下列逻辑函数化成最简与或表达式。

(1)D++A=F+BCBCACA(2)()()D++=F+AACCDA(3)()()B++F+=B+DCDBDDA(4)()D++F+=ADCBCBA(5)()C A B C B AC F ⊕++= (6)()()C B B A F ⊕⊕= 题解:(1)BC A D C A BC C A B A F +=+++= (2)()()CD A D CD A C A A F +=+++=(3)()()C B B A D B D A C B D D D B F ++=++++= (4)()D C B A D C B AD C B A F +=+++= (5)()C B AC C A B C B AC F +=⊕++=(6)()()C A BC B A C B B A F ++=⊕⊕=或C A C B AB ++= 用卡诺图将下列逻辑函数化成最简与或表达式。

第8章 Verilog有限状态机设计8.1 有限状态机摩尔型(Moore)状态机米里型(Mealy)状态机用状态机设计模5计数器module fsm(clk,clr,z,qout);input clk,clr; output reg z; output reg[2:0] qout; always @(posedge clk or posedge clr) //此过程定义状态转换begin if(clr) qout<=0; //异步复位else case(qout)3'b000: qout<=3'b001;3'b001: qout<=3'b010;3'b010: qout<=3'b011;3'b011: qout<=3'b100;3'b100: qout<=3'b000;default: qout<=3'b000;/*default语句*/endcaseendalways @(qout) /*此过程产生输出逻辑*/ begin case(qout)3'b100: z=1'b1;default:z=1'b0;endcaseendendmodule8.2 有限状态机的几种描述方式“101”序列检测器的Verilog 描述(三个过程)module fsm1_seq101(clk,clr,x,z);input clk,clr,x; output reg z; reg[1:0] state,next_state;parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; /*状态编码,采用格雷(Gray )编码方式*/always @(posedge clk or posedge clr) /*该过程定义当前状态*/begin if(clr) state<=S0; //异步复位,s0为起始状态else state<=next_state;end always @(state or x) /*该过程定义次态*/begin case (state)S0:begin if(x) next_state<=S1;else next_state<=S0; end S1:begin if(x) next_state<=S1;else next_state<=S2; endS2:beginif(x) next_state<=S3; else next_state<=S0; end S3:b e g i ni f(x)next_state<=S1;else next_state<=S2; enddefault:next_state<=S0;/*default语句*/ endcaseend always @(state)/*该过程产生输出逻辑*/ begin case(state)S3: z=1'b1;default:z=1'b0; endcaseendendmodule“101”序列检测器的Verilog描述(三个过程)“101”序列检测器(单过程描述)module fsm4_seq101(clk,clr,x,z);input clk,clr,x; output reg z; reg[1:0] state; parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10;/*状态编码,采用格雷(Gray)编码方式*/always @(posedge clk or posedge clr)Begin if(clr) state<=S0; //异步复位,s0为起始状态else case(state)S0:begin if(x) begin state<=S1; z=1'b0;endelse begin state<=S0; z=1'b0;endendS1:begin if(x) begin state<=S1; z=1'b0;endelse begin state<=S2; z=1'b0;endendS2:begin if(x) begin state<=S3; z=1'b0;endelse begin state<=S0; z=1'b0;endendS3:begin if(x) begin state<=S1; z=1'b1;endelse begin state<=S2; z=1'b1;endenddefault:begin state<=S0; z=1'b0;end /*default语句*/ endcase endendmodule8.3 状态编码常用的编码方式一位热码编码选择对话框(Quartus Ⅱ)在Verilog语言中,有两种方式可用于定义状态编码,分别用parameter和'define语句实现,比如要为state0、state1、state2、state3四个状态定义码字为:00、01、11、10,可采用下面两种方式。

第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)(10010111)2(3)(1101101)2 (4)(11111111)2(5)(0.1001)2(6)(0.0111)2(7)(11.001)2(8)(101011.11001)2题1.1 解:(1)(11011)2 =(27)10 (2)(10010111)2 =(151)10(3)(1101101)2 =(109)10 (4)(11111111)2 =(255)10(5)(0.1001)2 =(0.5625)10(6)(0.0111)2 =(0.4375)10(7)(11.001)2=(3.125)10(8)(101011.11001)2 =(43.78125)10 1.3 将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(110111011)2(3)(10110.011010)2 (4)(101100.110011)2题1.3 解:(1)(1010111)2 =(57)16 =(127)8(2)(110011010)2 =(19A)16 =(632)8(3)(10110.111010)2 =(16.E8)16 =(26.72)8(4)(101100.01100001)2 =(2C.61)16 =(54.302)81.5 将下列十进制数表示为8421BCD码。

(1)(43)10 (2)(95.12)10(3)(67.58)10 (4)(932.1)10题1.5 解:(1)(43)10 =(01000011)8421BCD(2)(95.12)10 =(10010101.00010010)8421BCD(3)(67.58)10 =(01100111.01011000)8421BCD(4)(932.1)10 =(100100110010.0001)8421BCD1.7 将下列有符号的十进制数表示成补码形式的有符号二进制数。

【最新整理,下载后即可编辑】

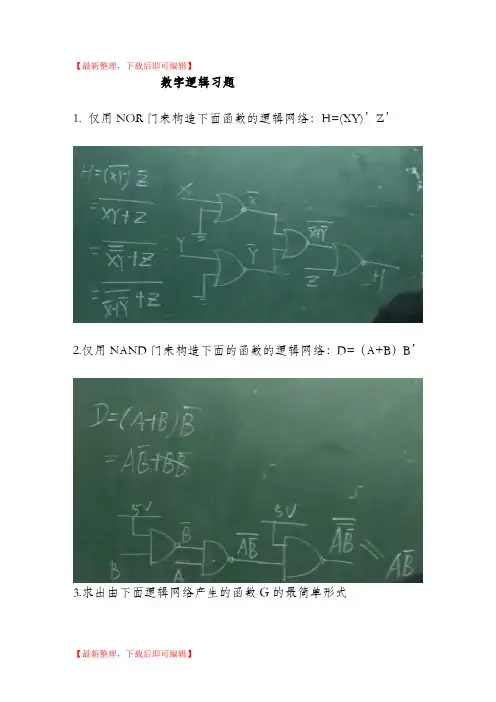

数字逻辑习题

1.仅用NOR门来构造下面函数的逻辑网络:H=(XY)’Z’

2.仅用NAND门来构造下面的函数的逻辑网络:D=(A+B)B’

3.求出由下面逻辑网络产生的函数G的最简单形式

4.卡诺图化简:G(A,B,C,D)=Σm(2,3,4,7,8,14,15)

5. 卡诺图化简:G(A,B,C,D)=Σm(0,1,3,4,6,7,12,13,14)

6.卡诺图化简:G(A,B,C,D)=Σm(0,4,5,6,7,8,13,14,15)

7.卡诺图化简:G(A,B,C,D)=Σm(1,2,3,4,6,7,9,12,13)

8.采用一个组合电路来控制一个十进制的七段显示,此电路有4个输入,并提供用压缩十进制数表示的4位代码(0(d)=0000,……8(d)=1000,9(d)=1001)。

7个输出用来定义哪段激活,以显示给定的十进制数

(1)写出这个电路的真值表

(2)用sop形式表示真值表

(3)用pos形式表示真值表(4)写出各段化简的表达式

7.时序电路分析

Q

Q

SET

CLR

D

X

Clock

Y

补充:

【最新整理,下载后即可编辑】。

4.1分析图4.1电路的逻辑功能解:(1)推导输出表达式(略)(2) 列真值表(略)4.6 试设计一个将8421BCD 码转换成余3码的电路。

解: 电路图略。

4.7 在双轨输入条件下用最少与非门设计下列组合电路: 解:略4.8 在双轨输入信号下,用最少或非门设计题4.7的组合电路。

解:将表达式化简为最简或与式:(1)F=(A+C)(⎺A+B+⎺C)= A+C+⎺A+B+⎺C(2)F=(C+⎺D)(B+D)(A+⎺B+C)= C+⎺D+B+D+A+⎺B+C(3)F=(⎺A+⎺C)(⎺A+⎺B+⎺D)(A+B+⎺D)= ⎺A+⎺C+⎺A+⎺B+⎺D+A+B+⎺D(4)F=(A+B+C)(⎺A+⎺B+⎺C)= A+B+C+⎺A+⎺B+⎺C4.9 已知输入波形A 、B 、C 、D ,如图P4.4所示。

采用与非门设计产生输出波形如F 的组合电路。

解: F=A ⎺C+⎺BC+C ⎺D 电路图略4.10 电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。

试设计该编码电路。

解:略4.11 试将2/4译码器扩展成4/16译码器 解:A 3A 2A 1 A 0⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺Y 4 ⎺Y 5⎺Y 6⎺Y 7 ⎺Y 8⎺Y 9⎺Y 10⎺Y 11 ⎺ Y 12⎺Y 13⎺Y 14⎺Y 15 A 1 ⎺EN ⎺Y 3A 0 2/4 ⎺Y 2译码器 ⎺Y 1⎺Y 0⎺EN A 1 2/4(1)A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3⎺EN A 1 2/4(2) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺EN A 1 2/4(3) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺EN A 1 2/4(4) A 0 ⎺Y 0⎺Y 1⎺Y 2⎺Y 34.12 试用74138设计一个多输出组合网络,它的输入是4位二进制码ABCD ,输出为:F 1 :ABCD 是4的倍数。

1

第8章 数字系统设计基础

8.1 数字系统在逻辑上可以划分成哪两个部分?其中哪一部分是数字系统的核心?

解:数字系统在逻辑上可以划分成控制器和数据处理器两部分,控制器是数字系统的核心。

8.2 什么是数字系统的ASM图?它与一般的算法流程图有什么不同?ASM块的时序意义是什么?

解:算法状态机(ASM)是数字系统控制过程的算法流程图。它与一般的算法流程图的区别为ASM

图表可表示事件的精确时间间隔序列,而一般的算法流程图只表示事件发生的先后序列,没有

时间概念。ASM块的时序意义是一个ASM块内的操作是在一个CLK脉冲作用下完成的。

8.3 某数字系统,在T

0状态下,下一个CLK到,完成无条件操作:寄存器R←1010,状态由T0

→

T1。在T1状态下,下一个CLK到,完成无条件操作:R左移,若外输入X=0,则完成条件操

作:计数器A←A

+ 1,状态由T1→T2;若X = 1,状态由T

1→T3

。画出该系统的ASM图。

解:ASM图表如图所示

8.4 一个数字系统在T

1状态下,若启动信号C = 0,则保持T1状态不变;若C =

1,则完成条件操作:

A←N1,B←N2,状态由T1→T2。在T2状态下,下一个CLK到,完成无条件操作B←B −

1,若

M

= 0,则完成条件操作:P右移,状态由T2→T3;若M = 1,状态由T

2→T4→T1

。画出该数字系

统的ASM图。

解:ASM图表如图

2

8.5 控制器状态图如题图8.5所示,画出其等效的ASM图。

题图8.5

解:ASM图

8.6 设计一个数字系统,它有三个4位的寄存器X、Y、Z,并实现下列操作:

① 启动信号S出现,传送两个4位二进制数N

1、N2

分别给寄存器X、Y;

② 如果X>Y,左移X的内容,并把结果传送给Z;

③ 如果X

=

Y,把X或Y传送给Z。

画出满足以上要求的ASM图。

解:ASM图如下图

3

8.7 某数字系统的ASM图如题图8.7所示,试完成下列要求:

(1)画出其等效的状态图;

(2)用每态一个触发器的方法设计控制器。

解:(1) 状态图

(2)

电路图略

题图8.7

4

8.8 某数字系统的ASM图如题图8.8所示,试根据此ASM图用MUX、D-FF、译码器方法设计控

制器。

解: 状态转换真值表

卡诺图 电路图

状态 Q

1n Q0n S X Y Z Q1n+1 Q0n+1 T0 T1 T2 T3

T0 0 0 0 0 0 φ φ φ 1 φ φ φ 0 0 0 1 1 0 0 0

1 0 0 0

T1 0 1

0 1

0 1

0 1

φ 0 0 φ

φ 0 1 0

φ 0 1 1

φ 1 φ φ

0 1

1 1

1 0

1 0

0 1 0 0

0 1 0 0

0 1 0 0

0 1 0 0

T2 1 0

1 0

1 0

1 0

φ 1 0 φ

φ 0 0 φ

φ 0 1 φ

φ 1 1 φ

1 0

1 1

0 0

0 0

0 0 1 0

0 0 1 0

0 0 1 0

0 0 1 0

T3 1 1 φ φ φ φ 0 0 0 0 0 1

题图8.8

5

8.9 某公园有一处4种颜色的彩色艺术图案灯,它的艺术图案由4种颜色顺序完成,绿色亮16 s,

红色亮10 s,蓝色亮8 s,黄色亮5 s,周而复始地循环,试设计这种灯的控制系统。

解:(1)ASM图

(2)控制器设计

根据ASM图,有四个状态T0,T1,T2,T3,可画出控制器的状态转换表

用MUX , D-FF,译码器组成的控制器如解题图8.9中虚线左部分所示。

解题图8.9

6

(3) 处理器设计

根据ASM图,可得t =1的条件方程为

t = T

0·16s + Tl·10s + T2·8s + T3

·5s

t =1时计时计数器应清0,表示以上计时结束,准备计下一个定时时间,故t应接加法计数器

的LD端,加法计数器选用 74161,其CLK周期 T

CLK

=1s。定时信号t =1的电路和计时电路74161 构

成的数据处理器如解题图8.9虚线右部分所示。解题图8.9为四色灯控制系统的整体电路。

8.10 设计十字路口交通灯控制系统:东西方向道路和南北方向道路各行车1分钟,两方向红绿灯

交换时,须亮黄灯5 s。东西方向绿、黄、红灯亮分别用EG

、EY、

ER表示,南北方向绿、黄、

红灯亮分别用SG、SY、SR表示。试按上述要求设计交通灯控制系统。

解:1)ASM图表

设E = 1分钟 (红绿灯亮时间), F = 5秒(黄灯亮时间)。时间到S=1, 计数器清零。

2)控制器设计

控制器的状态转换表

状态 Q2n Q1n E FQ2n+1 Q1n+1

输出

T0 T1 T2 T

3

T0 0 0 0 0 0 ϕ 1 ϕ 0 0 0 1 1 0 0 0

1 0 0 0

T1 0 1 0 1 ϕ 0 ϕ 1 0 1 1 0 0 1 0 0

0 1 0 0

T2 1 0 1 0 0 ϕ 1 ϕ 1 0 1 1 0 0 1 0

0 0 1 0

T3 1 1 1 1 ϕ 0 ϕ 1 1 1 0 0 0 0 0 1

0 0 0 1

卡诺图

7

控制器电路

3)数据处理器设计

定时电路方程及电路:S = (T

0+T2)E+(T1+T3

)F

产生E=1分钟和F=5秒的电路由两级160实现。

整体电路如图:

8.11 设计8种花型彩灯控制系统:由8个发光二极管组成的彩灯,一字排开,彩灯的图案循环变

换步骤如下:

① 彩灯由左至右逐个亮至最后全亮;

② 彩灯由右至左逐个灭至最后全灭;

③ 彩灯由右至左逐个亮至最后全亮;

④ 彩灯由左至右逐个灭至最后全灭;

8

⑤ 8个彩灯全亮;

⑥ 8个彩灯全灭;

⑦ 8个彩灯全亮;

⑧ 8个彩灯全灭。

按以上要求设计彩灯控制系统。

解: 设八个彩灯由左至右排列:A

7 A6 A5 A4 A3 A2 A1 A0

1.ASM图

2.控制器设计

控制器实现T

0~T7八个状态。用74161(高)的Q2Q1Q0组成模8计数器,实现T0~T7

八个状态的

转换。状态T0~T3四个状态中有8个灯的移动。

用另一74161(低) 的Q2′Q1′Q0′组成模八计数器实现移位控制。

再由74191控制移位寄存器实现左、右移和并入, 而74191的左、右移及并入由M1M0控制。

根据ASM图表得下列对应关系:

控制器和数据处理器关系表

74161(低) Q2’ Q1’ Q0’ 74161(高) Q2 Q1 Q0 状态 Ti 74194移入数据 74191控制

M1=F1, M0=F

0

000~111 000 T0 SR1→A7 =1= 0Q (左移) 0 1

000~111 001 T1 SL2→A0 =0= 0Q (左移) 1 0

000~111 010 T2 SL2→A0 =1=

0

Q

(左移) 1 0

000~111 011 T3 SR1→A7 =0=

0

Q

(右移) 0 1

ϕ ϕ ϕ 100 T4 D7~D0 =11111111=

0

Q

1 1

ϕ ϕ ϕ 101 T5 D7~D0 =00000000=

0

Q

1 1

ϕ ϕ ϕ 110 T6 D7~D0 =11111111=

0

Q

1 1

ϕ ϕ ϕ 111 T7 D7~D0 =00000000=

0

Q

1 1

∴ SR1=SL2=D7=D6=D5=D4=D3=D2=D1=D0=0Q

两个8选1的MUX74151(高)和74151(低)的地址端A

2A1A0=Q2Q1Q0

9

74151 (高)的0~7输入=M1=01101111 74151 (低)的0~7输入=M0=10011111

74194(1)和74194(2)级连实现8个灯A7~A0的移动变换, 故: Q4=DSR2, Q3=DSL1,

74161(高)在000~111状态时, 是被模8计数器74161(低)控制的加法计数器.

74161(低)在100~111状态时, 实现加法计数。 根据以上分析,得彩灯控制电路如下图所示: