双4选1数据选择器74LS153

- 格式:doc

- 大小:36.03 KB

- 文档页数:2

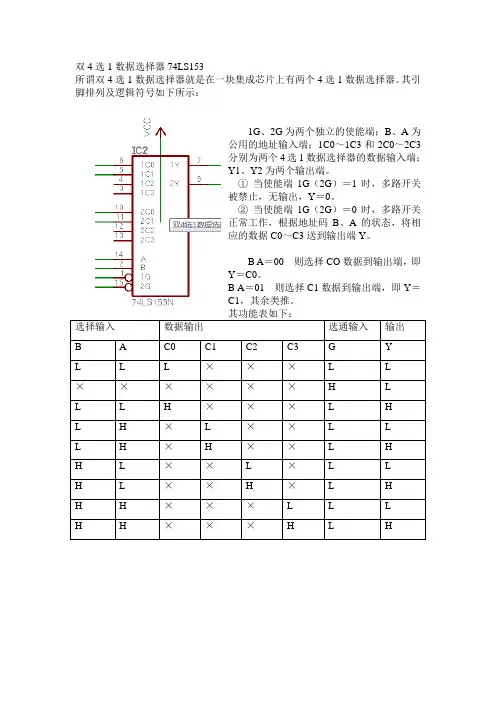

双4选1数据选择器74LS153

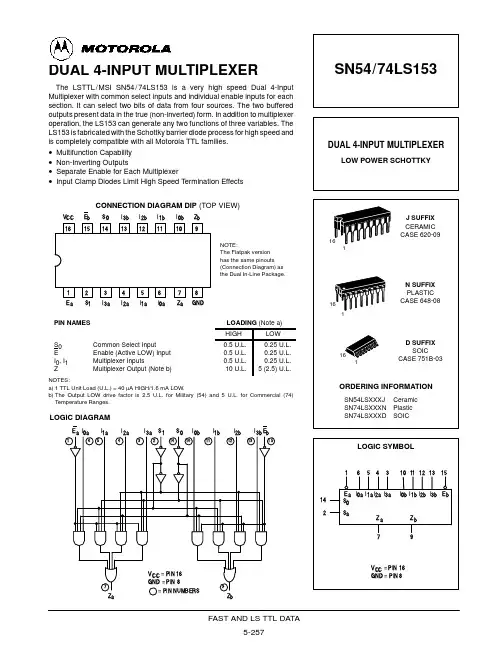

所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。

其引脚排列及逻辑符号如下所示:

1G、2G为两个独立的使能端;B、A为

公用的地址输入端;1C0~1C3和2C0~2C3

分别为两个4选1数据选择器的数据输入端;

Y1、Y2为两个输出端。

①当使能端1G(2G)=1时,多路开关

被禁止,无输出,Y=0。

②当使能端1G(2G)=0时,多路开关

正常工作,根据地址码B、A的状态,将相

应的数据C0~C3送到输出端Y。

B A=00 则选择CO数据到输出端,即

Y=C0。

B A=01 则选择C1数据到输出端,即Y=

C1,其余类推。

其功能表如下:

选择输入数据输出选通输入输出

B A C0 C1 C2 C3 G Y

L L L ×××L L

××××××H L

L L H ×××L H

L H ×L ××L L

L H ×H ××L H

H L ××L ×L L

H L ××H ×L H

H H ×××L L L

H H ×××H L H。

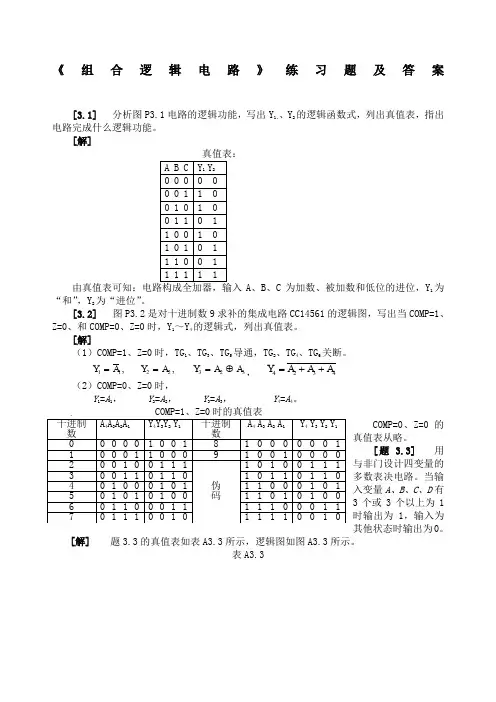

《组合逻辑电路》练习题及答案[3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]A 、B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++= (2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP=1、Z=0时的真值表 COMP=0、Z=0的真值表从略。

[题 3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

表A3.3[3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

真值表中的C B A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A3.4(a)化简后得到: C B A M S +=, B M L =(M S、M L的1状态表示工作,0状态表示停止)。

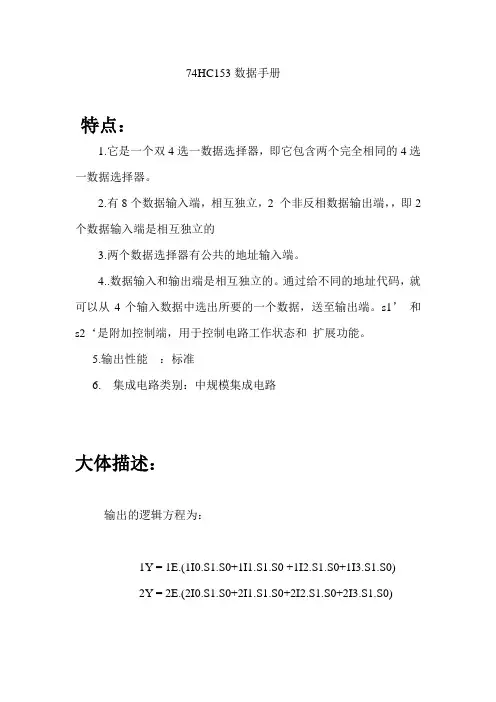

74HC153数据手册

特点:

1.它是一个双4选一数据选择器,即它包含两个完全相同的4选一数据选择器。

2.有8个数据输入端,相互独立,2 个非反相数据输出端,,即2 个数据输入端是相互独立的

3.两个数据选择器有公共的地址输入端。

4..数据输入和输出端是相互独立的。

通过给不同的地址代码,就可以从4个输入数据中选出所要的一个数据,送至输出端。

s1’和s2‘是附加控制端,用于控制电路工作状态和扩展功能。

5.输出性能:标准

6. 集成电路类别:中规模集成电路

大体描述:

输出的逻辑方程为:

1Y = 1E.(1I0.S1.S0+1I1.S1.S0 +1I2.S1.S0+1I3.S1.S0)

2Y = 2E.(2I0.S1.S0+2I1.S1.S0+2I2.S1.S0+2I3.S1.S0)

74HC153也可以把一个数据总线上的数据移动到一个寄存器中。

选择控制端的状态会决定哪个输出端输出数据。

同时,74HC153也可以产生一个含有三个变量的函数。

快速参考数据:

GND = 0 V, 温度t=25 ,tr = tf = 6ns

引脚图为1,

逻辑图为2,

国际电工组织逻辑图为3,

电路连接图为4,

74HC153数据选择器的真值表如下:

其中,L表示低电平,H表示高电平,*表示可以是高电平,也可以是低电平。

74HC153数据选择器的逻辑电路图如下:

74HC153的其他特性如下:

74HC153的直流特性如下:

74HC153数据选择器输入输出之间的延时特性图:。

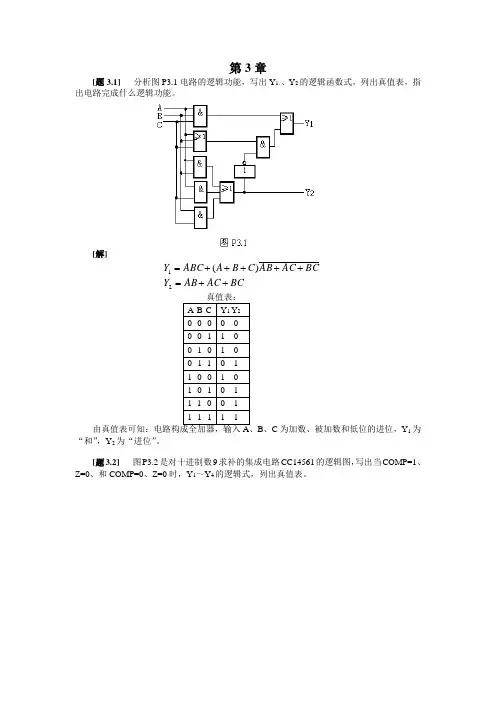

第3章[题3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]BCAC AB Y BCAC AB C B A ABC Y ++=+++++=21)(B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP =0、Z=0的真值表从略。

[题3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

ABCD D ABC D C AB CD B A BCD A Y ++++= BCD ACD ABC ABC +++=B C D A C D A B D A B C ⋅⋅⋅=[题3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +1、Y=A+B2、用卡诺图法化简为最简或与式 Y= + C +A D,约束条件:A C + A CD+AB=02、用卡诺图圈0的方法可得:Y=( +D)(A+ )( + )四、分析下列电路。

(每题6分,共12分)1、写出如图4所示电路的真值表及最简逻辑表达式。

图 41、该电路为三变量判一致电路,当三个变量都相同时输出为1,否则输出为0。

2、写出如图5所示电路的最简逻辑表达式。

2、B =1,Y = A ,B =0 Y 呈高阻态。

五、判断如图 6所示电路的逻辑功能。

若已知 u B =-20V,设二极管为理想二极管,试根据 u A 输入波形,画出 u 0 的输出波形(8分)t图 6五、 u 0 = u A · u B ,输出波形 u 0 如图 10所示:图 10六、用如图 7所示的8选1数据选择器CT74LS151实现下列函数。

(8分)Y(A,B,C,D)=Σm(1,5,6,7,9,11,12,13,14)图 7 答:七、用 4位二进制计数集成芯片CT74LS161采用两种方法实现模值为10的计数器,要求画出接线图和全状态转换图。

(CT74LS161如图8所示,其LD端为同步置数端,CR为异步复位端)。

(10分)图 8七、接线如图 12所示:图 12全状态转换图如图 13 所示:( a )( b )图 13八、电路如图 9所示,试写出电路的激励方程,状态转移方程,求出Z 1 、Z 2 、Z 3 的输出逻辑表达式,并画出在CP脉冲作用下,Q 0 、Q 1 、Z 1 、Z 2 、Z 3 的输出波形。

(设 Q 0 、Q 1 的初态为0。

)(12分)八、,,波形如图 14所示:三、将下列函数化简为最简与或表达式(本题 10分)1. (代数法)2、F 2 ( A,B,C,D)=∑m (0,1,2,4,5,9)+∑d (7,8,10,11,12,13)(卡诺图法)三、1. 2.四、分析如图 16所示电路,写出其真值表和最简表达式。

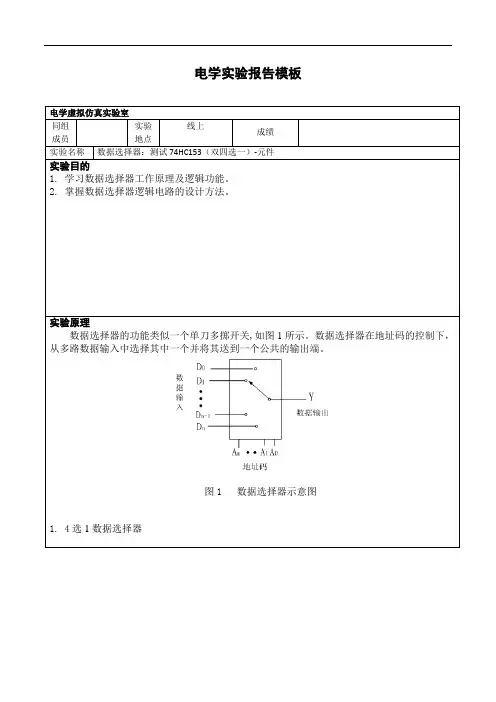

电学实验报告模板实验原理数据选择器的功能类似一个单刀多掷开关,如图1所示。

数据选择器在地址码的控制下,从多路数据输入中选择其中一个并将其送到一个公共的输出端。

图1 数据选择器示意图1. 4选1数据选择器图2 4选1数据选择器及其逻辑图2所示为4选1数据选择器及其逻辑。

该电路有4路输入数据和为地址输入。

为使能控制端,当时,数据选择器正常工作;当时,数据选择器的输出被锁定在“0”,不能选择。

由图2(b)可以得到该数据选择器的逻辑函数式为(1)2. 用4选1数据选择器扩展成8选1数据选择器8选1数据选择器有8路数据输入,3位地址输入。

如果用4选1数据选择器实现8选1,需要2片4选1数据选择器,如图所示。

其中,是通过4选1数据选择器的使能控制端接入的。

由图5并根据式(1),可以得到显然实现了8选1的逻辑功能。

图5 用4选1数据选择器扩展成8选1数据选择器实验仪器实验内容及步骤1. 测试和验证74HC153的逻辑功能(1)集成电路芯片74HC153引脚图74HC153是双4选1数据选择器,芯片内部包含两个独立的、完全相同的4选1数据选择器。

图7-5所示为引脚图。

每一个4选1数据选择器都设置了一个使能控制端。

两个4选1数据选择器共享地址输入端。

图6 74HC151引脚图(2)测试和验证74HC153的逻辑功能按图7连接电路。

实验数据记录在表7-1。

验证74HC153的逻辑功能。

图7 测试74HC151的逻辑功能实验电路表1(3)用一片74HC153扩展成8选1数据选择器图8 74HC153扩展成8选1数据选择器实验电路按图8连接电路。

实验数据记录在表2。

验证电路的逻辑功能。

表2实验结果及分析1.实验结果2.分析该实验结果表明74HC153元件实现了4选1的数据选择功能74HC153与74LS00两个4选1数据选择器拓展实现了8选1的逻辑功能实验结论1.74HC153具有4选1逻辑功能,能够实现数据选择,其有4路输入数据D0、D1、D2、D3,A0、A1为地址输入,为使能控制端,当时,数据选择器正常工作;当时,数据选择器的输出被锁定在“0”,不能选择。

![[说明]数电数据选择器](https://uimg.taocdn.com/d3b61ced760bf78a6529647d27284b73f24236f9.webp)

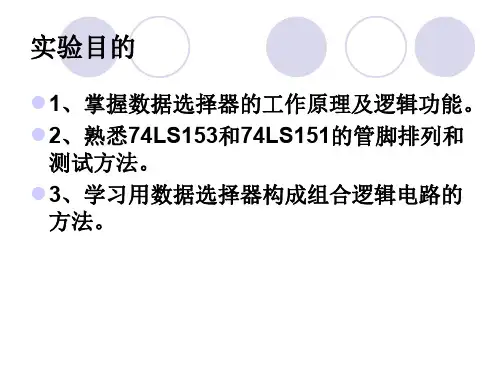

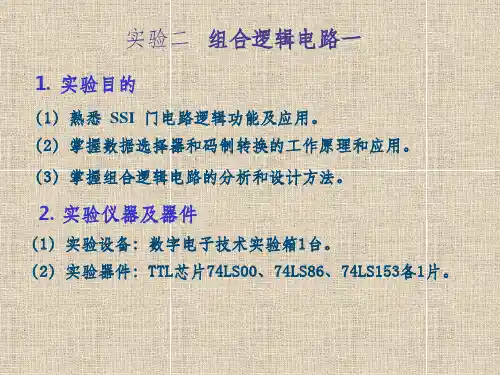

数据选择器一.实验目的1.熟悉中规模集成数据选择器的逻辑功能及测试方法。

2.学习用集成数据选择器进行逻辑设计。

二.实验原理数据选择器是常用的组合逻辑部件之一。

它由组合逻辑电路对数字信号进行控制来完成较复杂的逻辑功能。

它有若干个数据输入端0D 、1D 、…,若干个控制输入端0A 、1A 、…和一个输出端O Y 。

在控制输入端加上适当的信号,即可从多个输入数据源中将所需的数据信号选择出来,送到输出端。

使用时也可以在控制输入端上加上一组二进制编码程序的信号,使电路按要求输出一串信号,所以它也是一种可编程的逻辑部件。

中规模集成芯片74LS153为双四选一数据选择器,引脚排列如图7—1所示,其中0D ,1D ,2D ,3D 为四个数据输入端,Y 为输出端,0A ,1A 为控制输入端(或称地址端)同时控制两个四选一数据选择器的工作,G 为工作状态选择端(或称使能端)。

74LS153的逻辑功能如表7—1所示,当1)2(1==G G 时电路不工作,此时无论1A 、0A 处于什么状态,输出Y 总为零,即禁止所有数据输出,当0)2(1==G G 时,电路正常工作,被选择的数据送到输出端,如0101=A A ,则选中数据1D 输出。

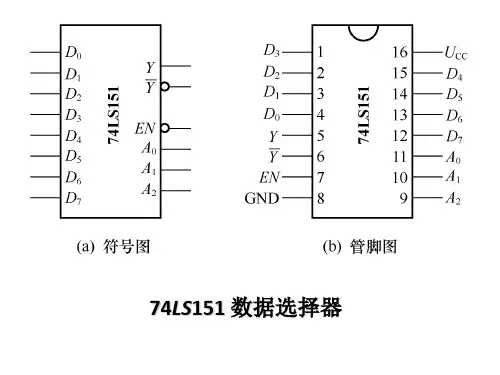

图7—1 图7—2当G =0时,74LS153的逻辑表达式为31020__1101__00__1__D A A D A A D A A D A A Y +++=中规模集成芯片74LS151为八选一数据选择器,引脚排列如图7—2所示。

其中D 0—D 7为数据输入端,)(Y Y 为输出端,2A 、1A 、0A 为地址端,74LS151的逻辑功能如表7—2所示。

逻辑表达式为 701260__12501__240__1__23102__20__12__101__2__00__1__2__D A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A Y +++++++=数据选择器是一种通用性很强的中规模集成电路,除了能传递数据外,还可用它设计成数码比较器,变并行码为串行码及组成函数发生器。

实验三数据选择器实验人员:班号:学号:一、实验目的(1) 熟悉并掌握数据选择器的功能。

(2) 用双4选1数据选择器74LS153设计出一个16选1的数据选择器。

(3) 用双4选1数据选择器74LS153 设计出一个全加法器。

二、实验设备数字电路实验箱,74LS00,74LS153。

三、实验内容(1) 测试双4选1数据选择器74LS153的逻辑功能。

74LS153含有两个4选1数据选择器,其中A0和A1为芯片的公共地址输入端,Vcc 和GND分别为芯片的公共电源端和接地端。

Figure1为其管脚图:Figure 11Q=A1A01D0+A1A0?1D1+A1A0?1D2+A1A0?1D32Q=A1A02D0+A1A0?2D1+A1A0?2D2+A1A0?2D3按下图连接电路:Figure 2(2) 设某一导弹发射控制机构有两名司令员A、B和两名操作员C、D,只有当两名司令员均同意发射导弹攻击目标且有操作员操作,则发射导弹F。

利用所给的实验仪器设计出一个符合上述要求的16选1数据选择器,并用数字电路实验箱上的小灯和开关组合表达实验结果。

思路:由于本实验需要有四个地址输入端来选中16个数据输入端的地址之中的一个,进而实现选择该数据输入端中的数据的功能,即16选1。

而公共的A0、A1两个地址输入端和S使能端(用于片选,已达到分片工作的目的,进而扩展了一位输入)一共可以提供三个地址输入端,故需要采用降维的方法,将一个地址输入隐藏到一个数据输入端Dx 中。

本实验可以降一维,也可以降两位。

由于两位比较复杂,本实验选择使用降一维的方式。

做法:画出如应用题中实现所需功能的卡诺图:将D 降到数据输入端中。

对应的卡诺图如下:其中,“1”表示高电平,“0”表低电平,均由开关上下拨动来控制;A 、B 、C 、D 分别为题中的两个司令员的同意情况和两个操作员的操作情况;F 为导弹发射情况,将F 接到小灯上即可。

电路如Figure 3所示(图中Cx 即Dx,后面的图均为如此):Figure 3(3) 用74LS00与74LS153设计一位全加器,并用数字电路实验箱上的小灯和开关组合表达实验结果。

四选一数据选择器74LS153级联方法分析与研究

张辉;李竹

【期刊名称】《电脑与电信》

【年(卷),期】2017(000)006

【摘要】本文介绍了数据选择器的功能以及常见的几种数据选择器,重点介绍了四选一数据选择器74LS153及其扩展级联方式,详细分析了最常见的利用使能端进行扩展的级联方式,提出了一种不利用使能端且采用二级级联的方式扩展数据选择器.【总页数】3页(P42-44)

【作者】张辉;李竹

【作者单位】山西师范大学临汾学院,山西临汾 041000;山西师范大学物信学院,山西临汾 041004

【正文语种】中文

【中图分类】O453

【相关文献】

1.双四选一数据选择器74 HC153的级联分析及研究 [J], 单嵛琼;单长吉

2.四川某钒钛磁铁矿选铁尾矿选钛试验研究 [J], 杨永涛;张渊;张俊辉

3.四川省文史研究馆馆员作品选—刘道容山水画选 [J],

4.四川省文史研究馆馆员作品选——抗震救灾义卖书画作品选 [J], 岑学恭

5.四川省文史研究馆馆员作品选—刘道容山水画选 [J], 刘道容

因版权原因,仅展示原文概要,查看原文内容请购买。

(单选题)1: 把一个五进制计数器与一个四进制计数器串联可得到()进制计数器

A: 4

B: 5

C: 9

D: 20

正确答案: D

(单选题)2: 以下电路中,加以适当辅助门电路,()适于实现单输出组合逻辑电路

A: 奇偶校验器

B: 数据选择器

C: 数值比较器

D: 七段显示译码器

正确答案: B

(单选题)3: 一个8选一数据选择器的数据输入端有()个

A: 1

B: 2

C: 3

D: 8

正确答案: D

(单选题)4: 在数字系统里,当某一线路作为总线使用,那么接到该总线的所有输出设备(或器件)必须具有()结构,否则会产生数据冲突。

A: 集电极开路

B: 三态门

C: 灌电流

D: 拉电流

正确答案: B

(单选题)5: 8位移位寄存器,串行输入时经()个脉冲后,8位数码全部移入寄存器中A: 1

B: 2

C: 4

D: 8

正确答案: D

(单选题)6: 欲使D触发器按Qn+1=/Qn工作,应使输入D=()

A: 0

B: 1

C: Q

D: /Q

正确答案: D

(单选题)7: 对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T=()。

三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +1、Y=A+B2、用卡诺图法化简为最简或与式 Y= + C +A D,约束条件:A C + A CD+AB=02、用卡诺图圈0的方法可得:Y=(+D)(A+ )(+ )四、分析下列电路。

(每题6分,共12分)1、写出如图4所示电路的真值表及最简逻辑表达式。

图 41、该电路为三变量判一致电路,当三个变量都相同时输出为1,否则输出为0。

2、写出如图5所示电路的最简逻辑表达式。

2、 B =1,Y = A ,B =0 Y 呈高阻态。

五、判断如图 6所示电路的逻辑功能。

若已知 u B =-20V,设二极管为理想二极管,试根据 u A 输入波形,画出 u 0 的输出波形(8分)t图 6五、 u 0 = u A · u B ,输出波形 u 0 如图 10所示:图 10六、用如图 7所示的8选1数据选择器CT74LS151实现下列函数。

(8分)Y(A,B,C,D)=Σm(1,5,6,7,9,11,12,13,14)图 7 答:七、用 4位二进制计数集成芯片CT74LS161采用两种方法实现模值为10的计数器,要求画出接线图和全状态转换图。

(CT74LS161如图8所示,其LD端为同步置数端,CR为异步复位端)。

(10分)图 8七、接线如图 12所示:图 12全状态转换图如图 13 所示:( a )( b )图 13八、电路如图 9所示,试写出电路的激励方程,状态转移方程,求出Z 1 、Z 2 、Z 3 的输出逻辑表达式,并画出在CP脉冲作用下,Q 0 、Q 1 、Z 1 、Z 2 、Z 3 的输出波形。

(设 Q 0 、Q 1 的初态为0。

)(12分)八、,,波形如图 14所示:三、将下列函数化简为最简与或表达式(本题 10分)1. (代数法)2、F 2 ( A,B,C,D)=∑m (0,1,2,4,5,9)+∑d (7,8,10,11,12,13)(卡诺图法)三、 1. 2.四、分析如图 16所示电路,写出其真值表和最简表达式。

创作编号:

GB8878185555334563BT9125XW

创作者:凤呜大王*

双4选1数据选择器74LS153

所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。

其引脚排列及逻辑符号如下所示:

1G、2G为两个独立的使能端;B、

A为公用的地址输入端;1C0~1C3和

2C0~2C3分别为两个4选1数据选择

器的数据输入端;Y1、Y2为两个输出

端。

①当使能端1G(2G)=1时,多路

开关被禁止,无输出,Y=0。

②当使能端1G(2G)=0时,多路

开关正常工作,根据地址码B、A的状

态,将相应的数据C0~C3送到输出端

Y。

B A=00 则选择CO数据到输出

端,即Y=C0。

B A=01 则选择C1数据到输出端,即Y=C1,其余类推。

选择输入数据输出选通输入输出B A C0 C1 C2 C3 G Y L L L ×××L L

××××××H L

L L H ×××L H L H ×L ××L L

L H ×H ××L H

创作编号:

GB8878185555334563BT9125XW

创作者:凤呜大王*。