用循环语句设计一个7人投票表决器

- 格式:wps

- 大小:12.00 KB

- 文档页数:1

Eda与数字系统课程设计课题名称:用VHDL文本输入法设计一个7人多数表决电路班级:09电科四班学号:2220091497姓名:楚惠一.课题题目:多数表决电路的设计之二要求:用VHDL文本输入法设计一个7人多数表决电路二.实验内容所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

三.设计步骤1、表决器主控电路代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity biao isport (xin: in std_logic_vector ( 6 downto 0 );xout,xout0,xout1,xout2 : out std_logic_vector ( 6 downto 0 ));end entity ;architecture bev of biao isbeginprocess ( xin )variable j: integer :=0;beginj:=0;for i in 0 to 6 loopif xin(i)='1' thenj:=j+1;end if;end loop;if j>3 thenxout<="0110000";else xout<="1111110";end if;case j iswhen 0 =>xout1<="1111110";when 1 =>xout1<="0110000";when 2 =>xout1<="1101101";when 3 =>xout1<="1111001";when 4 =>xout1<="0110011";when 5 =>xout1<="1011011";when 6 =>xout1<="1011111";when 7 =>xout1<="1110000";when others =>xout1<="XXXXXXX";end case;case j iswhen 7 =>xout0<="1111110";when 6 =>xout0<="0110000";when 5 =>xout0<="1101101";when 4 =>xout0<="1111001";when 3 =>xout0<="1011011";when 2 =>xout0<="0010010";when 1 =>xout0<="1011111";when 0 =>xout0<="1110000";when others =>xout0<="XXXXXXX";end case;end process;end architecture bev;2、输出显示部分数码管扫描用到的六进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt6a isport(cp,reset : in std_logic;sel :out std_logic_vector(2 downto 0));end cnt6a;architecture behave of cnt6a issignal sec :std_logic_vector (2 downto 0);beginprocess(reset,cp)beginif (reset='0')thensec<="000";elsif (cp'event and cp='1')thenif(sec="101") thensec<="000";elsesec<=sec+1;end if;end if;end process;sel<=sec;end behave;数码管的七段输出library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mux6 isport (cnthh,cnthl,cntmh,cntml,cntsh,cntsl :in std_logic_vector(6 downto 0);sel :in std_logic_vector(2 downto 0);cntout :out std_logic_vector(6 downto 0));end mux6;architecture behav of mux6 isbeginprocess(sel)begincase sel iswhen"000"=>cntout<=cntsl(6 downto 0);when"001"=>cntout<=cntsh(6 downto 0);when"010"=>cntout<=cntml(6 downto 0);when"011"=>cntout<=cntmh(6 downto 0);when"100"=>cntout<=cnthl(6 downto 0);when"101"=>cntout<=cnthh(6 downto 0);when others=>cntout<="0000000";end case;end process;end behav;顶层原理图:八.实验结果通过muxplus2对七人表决器进行设计,完成实验要求,得到实验结果,实现了七人表决的效果,4人或4人以上通过则亮绿灯,否则亮红灯。

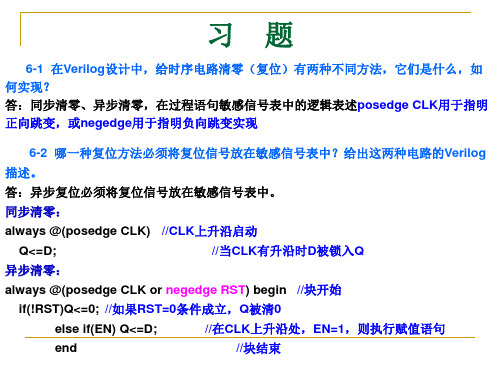

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

一、题目用VHDL设计七人表决器二、分析讨论:七人表决器这一功能用C语言、汇编语言或VHDL编程然后下载到单片机上实现,不过用VHDL编程不仅技术含量高而且能让我们更熟练的掌握使用quartus软件的步骤和方法。

所以我们使用VHDL完成。

七人表决器就是当投票的人中,同意个数过半(即大于等于4)时,认为通过;否则,不通过。

在编程中我们使用一个七位二进制输入变量表示投票人;一个七位二进制输出变量表示一个七段数码管显示同意的票数;一个一位的输出变量表示最终的投票结果。

此结果能够在quartus软件中通过时序仿真。

在硬件上我们用七个拨动开关来表示七个投票人,拨动开关为‘1’时表示同意,为‘0’表示不同意;同意的票数和表决的时间分别通过一个七段数码管显示出来;最终的表决结果用一个LED表示。

三、设计方案3.1实现原理首先,编写一个十进制的减法计数器,其输入为clk, clr, en,输出为q[3..0]。

外部的时钟信号的频率选择为1KHz,此频率太大无法显示投票的限制时间,所以要用一个分频器来增大计数时间。

设计一个分频器的程序,将时钟信号经过分频器输入到计数器中,输入为clk, 输出为new clk。

当clk 有1000个上升沿是newclk产生一个脉冲,也就是计数器计数一次。

其次,编辑七人表决器在主程序,其输入为clk, clr, en, input[6..0],q[3..0],输出为output,led[6..0]。

此程序的是时钟脉冲clk也为1KHz;当q 从9到4期间投票是有效的,在4到0期间是无效的,此时就显示之前同意的票数。

记录的票数通过casa语句转换到8位七段数码管显示出来。

投票的时间和记录的票数要通过两个数码管显示,所以要用一个三八译码器来完成。

接着编辑一个三八译码器的程序,其输入为clk, led[6..0], q[3..0], 输出为choice, data[7..0]。

程序中当用一个中间变量来选择数码管,由于clk的扫描的频率很大,所以两个数码管看上去是同时显示。

电子综合设计题目七人抢答器设计学院计信学院专业电子信息工程班级学生姓名指导教师2012 年 6 月18 日一、设计原理所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于 4 时,则认为同意;反之,当否决的票数大于或者等于4 时,则认为不同意。

二、分析讨论七人表决器这一功能可以用C语言、汇编语言或VHDL编程后下载到单片机上实现,不过用VHDL编程不仅技术含量高而且能让我们更熟练的掌握和使用quartus软件的步骤和方法。

所以我们是采用VHDL编程来实现的。

三、设计准备根据七人表决器的原理,我们的准备过程如下:1、使用Altera的Cyclone II器件,所用的芯片为EP2C35F672C8,开发平台为quartus II。

2、使用七个拨动开关(K1~K7)作为输入变量来表示七个投票人,当拨动开关输入为‘1’时,表示对应的人投同意票,否则当拨动开关输入为‘0’时,表示对应的人投反对票。

3、使用一个七段数码管来显示同意的票数。

4、使用七个LED(LED2~LED8)用来分别记录投票人的个人投票结果,当LED亮起时就表示对应的投票人同意,否则就表示不同意。

5、使用一个LED(LED1)来表示最终的投票结果,当LED1亮起时表示表决通过,不亮时就表示表决不通过。

6、使用一个拨动开关(K8)来达到复位要求,即需要复位时能够达到同时清零数码管的显示结果和LED的显示情况。

7、软件仿真成功后,通过专用的连接线再用硬件进行测试,并将硬件测试的结果以照片的形式做记录。

四、设计思路根据程序设计的一般步骤,我们首先设计出七人表决器的系统框图,也就是说先要确定一个大的设计方向;然后再根据设计要求并结合系统框图来设计程序流程图;由程序流程图来编写VHDL程序,并画出表决器的外围引脚图;再将程序用软件仿真,软件仿真成功后进行硬件测试。

1、本课程的讲授目标:了解一种新技术EDA;掌握一种设计工具(器件:Altera FPGA软件:Quartus II);掌握一种语言Verilog HDL。

2、使用Quartus II进行逻辑设计,常用的设计思想的输入方式有:原理图、HDL 等。

3、高级语言C程序经过软件程序编译器形成cpu指令/数据代码流;Verilog HDL程序经过综合器形成电路网表文件4、CPLD是在PAL,GAL等类型器件的基础上发展起来的与或阵列型PLD器件,大多数FPGA采用了查找表结构,其物理结构是静态存储器SRAM.。

5、JTAG边界扫描技术用于对高密度、引脚密集的器件和系统进行测试,如:CPU,DSP,ARM,PLD 等。

同时,JTAG接口也被赋予了更多的功能:编程下载、在线逻辑分析。

6、使用Verilog HDL进行逻辑设计,变量的值有4种状态:0、1、x、z;7、定义逻辑功能的几种基本方法:用assign持续赋值语句定义、用always过程块定义、调用元件(元件例化)。

8、整数按如下方式书写:+/-<size> '<base><value> 即+/-<位宽>'<进制><数字>size 为对应二进制数的宽度;base为进制;value是基于进制的数字序列。

进制有如下4种表示形式:二进制(b或B)、十进制(d或D或缺省)、十六进制(h或H)、八进制(o或O)9、定义reg型标量型变量:reg qout;//变量名qout10、定义wire型向量:wire[7:0] databus;//databus的宽度是8位11、在状态机设计中使用一位热码定义5种状态,并定义状态变量:parameter s0=5’b00001,s1=5’b 00010,s2=5’b 00100,s3=5’b 01000,s4=5’b 10000;reg [4:0] state,next_state;12、在状态机设计中使用顺序码定义5种状态,并定义状态变量:parameter s0=3’b 000,s1=3’b 001,s2=3’b 010,s3=3’b 011,s4=3’b 100;reg [2:0] state,next_state;1、成为IEEE 标准的HDL 有( CD )A 、ABEL-HDLB 、AHDLC 、VHDLD 、Verilog HDL2、Quartus II 是 ( A )公司的( D )开发工具。

河北科技大学实验报告2011级电信专业班学号14年4月10日姓名同组人指导教师于国庆实验名称实验一七人表决器成绩实验类型设计型批阅教师一、实验目的:(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”时,则表决器输出为“1”,否则为“0”。

表决器输入采用试验箱K1~K16,输出采用试验箱L15、L16指示;同意红灯亮,否则黄灯亮。

三、实验内容及步骤:1.打开MUXPLUS II VHDL编辑器,完成七人表决器的设计。

包括VHDL程序输入、编译、综合。

实验程序如下:library ieee;use ieee.std_logic_1164.ALL;entity GSL isport(a:in std_logic_vector(6 downto 0);b:out std_logic;c:out std_logic);end entity GSL;architecture number of GSL is beginprocess(a)variable cnt:integer range 0 to 7; begin cnt:=0;for i in 6 downto 0 loopif a(i)='1'thencnt:=cnt+1;end if;end loop;if cnt>3 then b<='1';c<='0';else b<='0';c<='1';end if;end process;end architecture number;2、建立仿真波形文件,使用 MAXPLUS II Simulator 功能进行功能仿真。

硬件课程设计课题名称:七人多数表决电路的设计七人多数表决电路的设计课题:题目:七人多数表决电路的设计要求:用VHDL文本输入法设计一个7人多数表决电路难度:10分摘要:所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED灯表示,若表决的结果为同意,则LED灯亮;否则,如果表决的结果为反对,则LED不会亮。

关键词:七人,多数,表决器,全加器,半加器。

设计要求(1)根据设计要求,绘制出电路状态转换图,实现七人四票制表决。

(2)根据电路状态转换图,用门电路设计出七人表决器。

(3)运用半加器,全加器,实现表决器的设计。

(4)逻辑设计要求:用七个开关作为表决器的七个输入变量,逻辑“1”时表示“赞同”,逻辑“0”时表示“不赞同”,用发光二极管作为输出指令,输出逻辑“1”表示“通过”;输出逻辑“0”时表示“不通过”。

当表决器的七个输入变量中的4个以上(包含4个)为“1”时,则表决器输出为“1”;否则为“0”。

设计步骤:表决结果与多数人意见相同。

设A1,A1,A2,A3,A4,A5,A6,A7为七个人(输入逻辑变量),赞成为1,不赞成为0;green和red为表决结果(输出逻辑变量),多数赞成green为1,red为0,否则,green为0,red为1,. 其真值表如表(1)所示。

(1)电路状态转换图:表(1)从真值表发现,A1 A2 A3 A4 A5 A6 A7中有四个或四个以上表示赞同,则绿灯亮,否则红灯亮。

根据电路状态转换图设计电路,用一个半加器实现设计一个全加器,运用4个全加器实现七人表决器的设计。

摘要7人表决器电路是一简单的输入信号检测与处理、产生运算控制信号的逻辑电路。

本文详细介绍了依据功能要求进行运算控制电路方案设计的过程,并在此基础上将整体电路分为数据接收模块、数据处理模块、结果显示模块等主要功能模块。

电路设计完成后通过Design Compiler对电路进行逻辑综合。

使用Tcl命令编写电路的约束文件,设定约束条件,对电路进行优化以保证设计的功能性,同时生成网表文件、时序报告、面积报告,并进行结果分析。

再通过延时文件与顶层文件的激励进行电路功能的时序仿真,分析设计的可行性。

再通过Primetime对电路进行静态时序分析,得到静态时序报告。

最后通过IC_Compler对生成的网表进行物理实现,生成GDS II版图信息。

关键词Design Compiler;Primetime;逻辑综合;静态时序分析;物理实现;目录摘要 (1)目录 (2)引言 (4)1 总体电路结构设计 (5)1.1电路功能 (5)1.2 关键功能电路设计 (5)1.3 电路接口 (6)1.4 顶层TOP的设计 (6)2 设计约束及脚本 (8)2.1 约束设计 (8)2.2 脚本设计 (8)3 逻辑综合过程 (11)3.1 综合文件 (11)3.2 综合环境 (11)3.3综合过程 (12)4 结果分析及时序仿真 (16)4.1 时序报告分析 (16)4.2 面积报告分析 (19)4.3时序仿真 (20)5 静态时序分析及脚本 (21)5.1 静态时序分析 (21)5.2 PrimeTime 进行时序分析的流程 (21)5.3 脚本 (22)5.4 静态时序报告分析 (24)6 物理实现 (28)6.1 物理实现文件 (28)6.2物理实现环境 (28)6.3物理实现过程 (29)6.3.1 Floorplan (29)6.3.2 placemant (30)6.3.3 Clock Tree synthesis (30)6.3.4 Routing (31)6.3.5 Write Design Out (32)6.4 报告输出 (32)6.5 LVS和DRC (34)结论 (35)参考文献 (36)附录A:顶层设计源代码 (37)附录B:设计约束代码 (38)附录C:静态时序分析脚本代码 (40)引言现代集成电路技术急剧发展,输百万级晶体管电路使设计面临着巨大的挑战。