PLL频率综合器中整数和小数分频器设计与实现

- 格式:pdf

- 大小:16.36 MB

- 文档页数:87

第24卷 增刊2005年9月国 外 电 子 测 量 技 术Foreign Elect ronic Measurement TechnologyVol.24,Suppl.Sep.,2005作者简介: 尹佳喜(1981-),华中科技大学电气与电子工程学院04级研究生,研究方向电力电子与电力传动。

研究与设计小数分频器的设计及其应用尹佳喜(华中科技大学电气与电子工程学院 湖北武汉430074)摘要:分频器是数字系统设计中最常见的电路之一,在数字系统设计中,经常需要对时钟进行小数倍分频。

本文给出了三种用于实现小数分频的方案,并将三种方案进行了比较。

在此基础上,介绍了小数分频器在直接数字频率合成技术和步进电机驱动速度控制中的两种常见应用。

关键词:小数分频器 直接数字频率合成 步进电机 频率The Design and Application of Decim al Fraction Frequency DividerY in Jiaxi(College of Elect ricit y and Elect ronic Engeneering ,H uaz hong Universit y of S cience and Techlonog y ,W uhan 430074,China )Abstract :Frequency division is one of t he mo st common circuit s in t he design of digital system.Generally ,decimal f raction f requency division is needed.In t his paper ,t hree met hods to realize deci 2mal f raction frequency division are given ,and t he comparison among t he t hree met hods is presented.Applications of decimal Fraction Frequency divider in t he area such as direct digital f requency syn 2t hesis technology and stepper motor drive speed controller are int roduced.K eyw ords :decimal f raction frequency divider ,direct digital frequency synt hesis (DDS ),stepper mo 2tor ,frequency.0 引言 现代电子系统设计中,数字电子系统所占的比例越来越大,现代电子系统发展的趋势是数字化和集成化。

任意数(整数、小数)分频器一、分频原理1.1偶数倍分频偶数倍分频通过计数器计数是很容易实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

1.2奇数倍分频奇数倍分频通过计数器也是比较容易实现的,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

与此同时进行下降沿触发的模N 计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

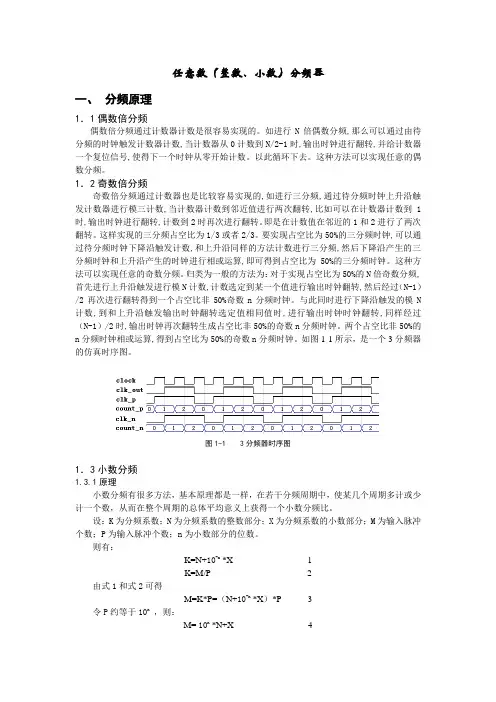

如图1-1所示,是一个3分频器的仿真时序图。

图1-1 3分频器时序图1.3小数分频1.3.1原理小数分频有很多方法,基本原理都是一样,在若干分频周期中,使某几个周期多计或少计一个数,从而在整个周期的总体平均意义上获得一个小数分频比。

设:K为分频系数;N为分频系数的整数部分;X为分频系数的小数部分;M为输入脉冲个数;P为输入脉冲个数;n为小数部分的位数。

基于FPGA的小数分频器的设计与实现【摘要】本文首先分析了现有小数分频器的优缺点,在此基础上提出了一种改进型小数分频器的设计方法。

同时结合VHDL文本输入和原理图输入方式,在FPGA开发平台上进行了电路设计,最后利用EDA设计软件QuartusII对其可行性进行了仿真验证。

仿真结果表明:通过对参数的设置,该方案可实现等占空比的任意小数分频。

【关键词】FPGA;仿真;VHDL引言分频器是控制类电路中常用的模块之一。

在实际应用中,设计人员常常需要将一个基准频率通过加、减、乘、除简单的四则运算进行频率合成,以满足不同的电路需求。

常见的偶数分频、奇数分频等成整数关系的频率合成实现相对比较容易。

但在某些的情况下,这种成整数关系的分频技术无法解决频率调整间隔过大的缺点,在此情况下本文提出了一种基于FPGA的小数分频的设计方法。

一般情况下,小数分频器包括半整数分频器和非半整数分频器。

对于半整数分频器我们在《基于FPGA 的通用数控分频器的设计与实现》[1]中有过详细介绍。

本文主要介绍非半整数分频器的设计和实现,并在FPGA开发平台上,结合VHDL文本输入和原理图输入方式进行了电路设计,同时利用EDA开发软件QuartusII对其可行性进行仿真验证。

仿真结果表明:该方法实现的小数分频,具有精度高、转化速度快、资源消耗低,可编程等优点,同时克服了小数分频中等占空比不易实现的问题。

1.几种常见小数分频器假设分频系数为K,输入频率为fin,输出频率为fout,则有:(1)其中:K>1当分频系数为小数时,则K可以表示为:(2)或:(3)其中,M、N、N1、N2均为正整数,且。

1.1 用BCD比例乘法器4527实现对于公式(2),可以利用十进制BCD比例乘法器的加法级联来实现[4]。

如图1所示,为两个4527 BCD比例乘法器的级联。

CLOCK端输入基准频率信号fin。

A、B、C、D四个端口是置数端,用以控制比例乘法器输出脉冲序列的个数。

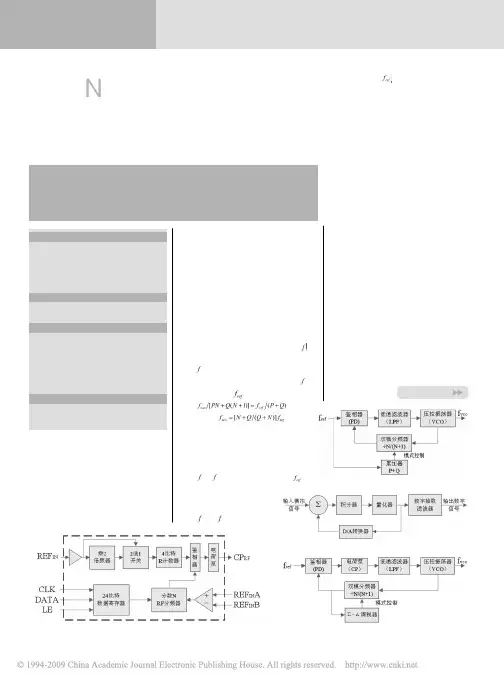

小数N分频低相噪频率合成器设计摘要:频率合成器是无线通信系统的重要组成部分,被称为系统的心脏。

换频时间及其频率稳定度、频率分辨率、相噪噪声是其关键参数。

本文介绍一种基于小数N分频的锁相环(PLL),结合高稳压控振荡器(VCO),输出精度准确,换频时间短,频率步进小的频率合成器,能实现每秒1000跳及以上的频率变换,切换频时间部超过20us。

1 绪论1.1课题研究的背景和意义从20世纪80年代以来,随着计算机、数字信号处理、扩频通信、自适应通信等现代电子信息技术的发展,各种先进的电子技术和新型的元器件被广泛地应用在现代军事通信领域。

跳频通信作为扩频通信的一种主要形式,由于其具有抗干扰、保密、抗截获和抗衰落等特点,并能做到频谱资源共享,在当前军事抗干扰通信系统中被广泛应用。

跳频通信系统的一项重要参数是频率的跳变速度,它在很大程度上决定了跳频通信系统抗跟踪式干扰的能力,这一点在电子对抗中尤为重要。

因此,高速的频率合成器就成为跳频通信系统中的关键部件之一。

本课题的主要任务是研制一个高跳速、高分辨率、高频谱纯度的小型化频率合成器,其设计基于集成的PLL芯片及高度稳定的VCO,能够满足高分辨率、高频谱纯度的频率合成器,系统能快速适应风云变化的战场环境,提高通信装备的灵活性。

本课题运用当今先进的器件资源和设计思想,研究具有高跳速、高分辨率、高频谱纯度的小型化频率合成器,实践军事通信的前沿技术,因此这是一项值得深入研究的课题。

1.2 国内外的研究现状随着现代电子技术进步和器件制造工艺的提高,目前频率合成主有三种方法:直接模拟合成法、直接数字合成法和锁相环合成法。

直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参考频率中产生多个所需的频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,目前已基本不被采用。

直接数字合成(DDS)是从相位概念出发直接合成所需波形。

DDS应用在射频段的一个缺点是它的时钟频率要高于输出信号至少两倍,而如此高的时钟频率是不易实现的,并且D/A变换器的速度也限制了DDS的工作频率。

频率合成实验(虚拟实验)姓名:刘文学号: 04009616(一)锁相环频率合成器示波器1‐6波形初始值设为4e7(40MHz/V)分析:30M参考频率经过3分频fr即为10M,fo经过10倍分频等于fr,所以fo就是100m,如图所示。

示波器1为示波器6的波形经过3分频后的方波,频率为1MHz。

压控振荡器上的控制电压的变化情况:从0开始震荡到1.75。

示波器4上的方波频率为10MHz。

经过N分频后和参考频率异或形成示波器2中的方波。

低通滤波器的作用是平滑平滑VCO的控制电压。

如果将低通滤波器的带宽减小,那么环路锁定时间会增加,锁定后控制电压更稳定。

将synSen 的初始值设为3e6(3MHz/V),示波器1‐6波形将synSen 的初始值设为5e6(5MHz/V),示波器1‐6波形分析:(将synSen的初始值为3e6与5e6与初始情况作比较)两种情况稳定后结果均与synSen为4e6时相同,捕捉时间也基本相同,这是由于PLL换频时间仅与参考信号频率有关。

但由VCO控制信号波形可以看出,30M参考频率经过3分频fr即为10M,fo经过10倍分频等于fr,所以fo就是100m,如图所示。

由于灵敏度不同导致需要的压控电压不同,如图3M的压控电压明显大于5M时的压控电压。

synSen为3e6时,捕捉过程控制信号波动较大,稳定后控制信号波动也较大,这是由于VCO压控灵敏度小导致同样的频偏需要的控制电压更高。

synSen为5e6时,捕捉过程信号波动较小,稳定后信号波动也较小。

(二)小数频率合成器分析:小数分频既是双模分频,十分之七个循环周期的时间,进行3分频,其余时间进行4分频,导致3.3倍分频。

输入信号频率为10MHz。

由图像可以看出,输出信号频率约为103.1MHz,分频比为10.31,与要求基本相符。

从波形中我们可以看到,由于相位累加器每次大约约累计1/3*2π的相位,使得Carry信号频率大约1/3输入信号。

小数分频论文频率合成器论文摘要:本文进行了基于小数分频技术的频率合成器的研究与设计。

首先分析小数分频锁相的工作原理,随后设定了设计指标,进行控制部分设计、环路滤波器设计、压控振荡器的设计,从而实现基于小数分频技术的频率合成器。

并通过测试,其性能指标已达到设计要求。

关键词:小数分频;频率合成器;分频frequency synthesizer design based on fractional frequency division technologywang xiaoning(dalian air traffic controlstation,dalian116033,china)abstract:this article was based on fractional frequency synthesizer technology,research and design.first of fractional pll works,then set the design specifications,the control part of the design,loop filter design,the vco design,enabling technology-based fractional frequency synthesizer.and tested,its performance has reached the design requirements.keywords:fractional frequency division;frequencysynthesizer;frequency一、引言小数分频频率合成器是近年来出现的一种新技术,与传统的频率合成的技术方式相比,它具有分辨率高,相位噪声低的优点。

dds也是今年出现的一种新型技术,但是dds的工作频率一般较低,如果实现的频率合成器需要较高的频率,仅仅使用dds很难满足。

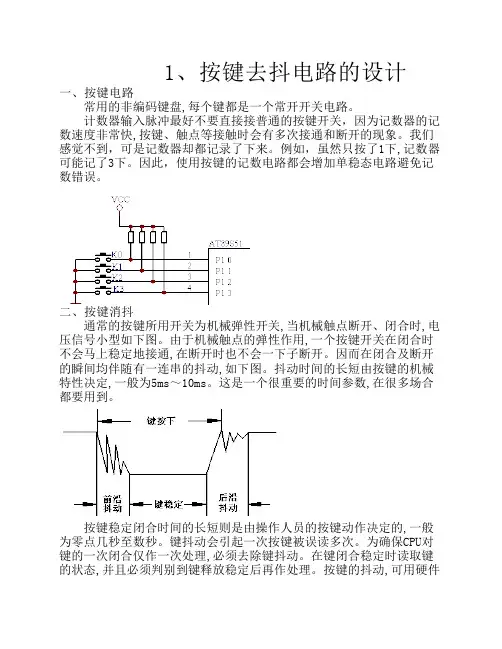

1、按键去抖电路的设计一、按键电路常用的非编码键盘,每个键都是一个常开开关电路。

计数器输入脉冲最好不要直接接普通的按键开关,因为记数器的记数速度非常快,按键、触点等接触时会有多次接通和断开的现象。

我们感觉不到,可是记数器却都记录了下来。

例如,虽然只按了1下,记数器可能记了3下。

因此,使用按键的记数电路都会增加单稳态电路避免记数错误。

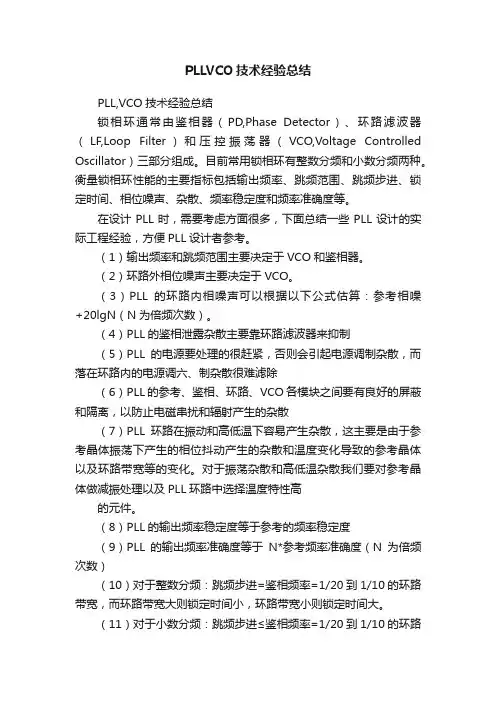

二、按键消抖通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,电压信号小型如下图。

由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。

因而在闭合及断开的瞬间均伴随有一连串的抖动,如下图。

抖动时间的长短由按键的机械特性决定,一般为5ms~10ms。

这是一个很重要的时间参数,在很多场合都要用到。

按键稳定闭合时间的长短则是由操作人员的按键动作决定的,一般为零点几秒至数秒。

键抖动会引起一次按键被误读多次。

为确保CPU对键的一次闭合仅作一次处理,必须去除键抖动。

在键闭合稳定时读取键的状态,并且必须判别到键释放稳定后再作处理。

按键的抖动,可用硬件或软件两种方法。

三、硬件消抖在键数较少时可用硬件方法消除键抖动。

下图所示的RS触发器为常用的硬件去抖。

图中两个“与非”门构成一个RS触发器。

当按键未按下时,输出为1;当键按下时,输出为0。

此时即使用按键的机械性能,使按键因弹性抖动而产生瞬时断开(抖动跳开B),中要按键不返回原始状态A,双稳态电路的状态不改变,输出保持为0,不会产生抖动的波形。

也就是说,即使B 点的电压波形是抖动的,但经双稳态电路之后,其输出为正规的矩形波。

这一点通过分析RS触发器的工作过程很容易得到验证。

利用电容的放电延时,采用并联电容法,也可以实现硬件消抖:四、软件延时消抖如果按键较多,常用软件方法去抖,即检测出键闭合后执行一个延时程序,产生5ms~10ms的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。

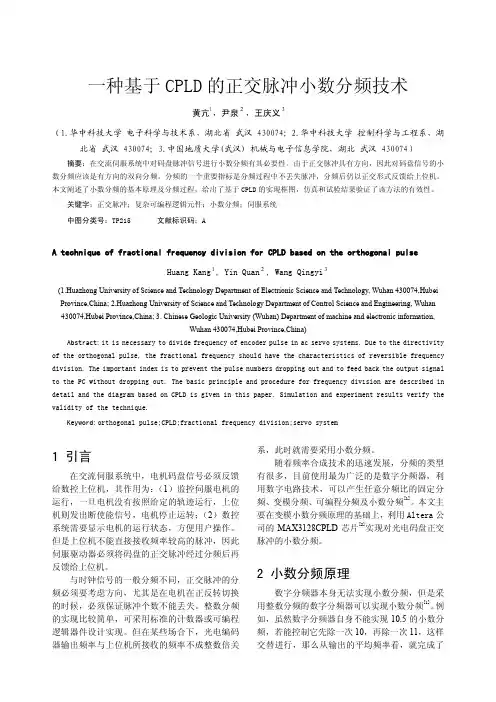

PLLVCO技术经验总结PLL,VCO技术经验总结锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成。

目前常用锁相环有整数分频和小数分频两种。

衡量锁相环性能的主要指标包括输出频率、跳频范围、跳频步进、锁定时间、相位噪声、杂散、频率稳定度和频率准确度等。

在设计PLL时,需要考虑方面很多,下面总结一些PLL设计的实际工程经验,方便PLL设计者参考。

(1)输出频率和跳频范围主要决定于VCO和鉴相器。

(2)环路外相位噪声主要决定于VCO。

(3)PLL的环路内相噪声可以根据以下公式估算:参考相噪+20lgN(N为倍频次数)。

(4)PLL的鉴相泄露杂散主要靠环路滤波器来抑制(5)PLL的电源要处理的很赶紧,否则会引起电源调制杂散,而落在环路内的电源调六、制杂散很难滤除(6)PLL的参考、鉴相、环路、VCO各模块之间要有良好的屏蔽和隔离,以防止电磁串扰和辐射产生的杂散(7)PLL环路在振动和高低温下容易产生杂散,这主要是由于参考晶体振荡下产生的相位抖动产生的杂散和温度变化导致的参考晶体以及环路带宽等的变化。

对于振荡杂散和高低温杂散我们要对参考晶体做减振处理以及PLL环路中选择温度特性高的元件。

(8)PLL的输出频率稳定度等于参考的频率稳定度(9)PLL的输出频率准确度等于N*参考频率准确度(N为倍频次数)(10)对于整数分频:跳频步进=鉴相频率=1/20到1/10的环路带宽,而环路带宽大则锁定时间小,环路带宽小则锁定时间大。

(11)对于小数分频:跳频步进≤鉴相频率=1/20到1/10的环路带宽,而环路带宽大则锁定时间小,环路带宽小则锁定时间大。

(12)根据经验环路滤波器相位裕量在时,锁定时间和过冲都可以设计的最小。

小于的相裕会产生过度的过冲和振铃,而大于则会导致一个过阻尼的环路,环路就会慢慢爬行到锁定。

任意数(整数、小数)分频器一、分频原理1.1偶数倍分频偶数倍分频通过计数器计数是很容易实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

1.2奇数倍分频奇数倍分频通过计数器也是比较容易实现的,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

与此同时进行下降沿触发的模N 计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

如图1-1所示,是一个3分频器的仿真时序图。

图1-1 3分频器时序图1.3小数分频小数分频有很多方法,基本原理都是一样,在若干分频周期中,使某几个周期多计或少计一个数,从而在整个周期的总体平均意义上获得一个小数分频比。

设:K为分频系数;N为分频系数的整数部分;X为分频系数的小数部分;M为输入脉冲个数;P为输入脉冲个数;n为小数部分的位数。

verilog 实现小数分频(小数分频器)小数分频无法做到1:1 的占空比。

例如用77 分频得到16M 时钟的生成原理如下:对于77 M的时钟,一个sts-12帧有9720拍。

对于16M时钟,一个sts-12帧有32*8*8拍。

即77M下每计数1215,16M下计数256.1215/256 =4.76 考虑到数字处理只能是整数,则需要在每m 个5拍扣一拍,每 n个4拍扣一拍。

列方程为:m + n =2565m + 4n =1215得到 m= 191, n = 65, 即通过191个5分频和65个4分频实现16M的时钟。

小数分频是通过可变分频和多次平均的方法实现的。

例如要实现4.7分频,需要在10次分频中做3 次4分频和7次5分频就可以做到,再如实现 5.67分频,只要在100次分频中,做67次6分频,33次5分频即可。

因为从N分频到N+1分频和从N+1分频到N分频的切换,会产生一个随时间增长的相位移。

考虑到小数分频中需要多次进行两种频率分频,必须将两种分频均匀,这种“均匀”工作是通过计数器完成的,这里仅给出一位小数的情况,下面简要介绍这种混合的方法:每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。

若累加结果小于10,则进行 N +1 分频,若大于或等于10,则进行N分频。

以8.7 分频为例进行设计时,需要进行3次 8分频,7次 9 分频。

该例中计数值(10-7)=3,前三次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,下表给出了该分频器的分频过程。

分频系数8.7--------------------------------------序号累加结果分频系数1 3 92 6 93 9 94 12-10 =2 85 5 96 8 97 11-10 =1 88 4 99 7 910 10 8 以下是代码模块://top modulemodule fd89bits( clkin,reset,a,clkout);input clkin;input reset;input a;output reg clkout;wire clkout1,clkout2;fd8bits dut1(clkin,reset,clkout1);fd9bits dut2(clkin,reset,clkout2);always@(posedge clkin) beginif(a)clkout <= clkout1;elseclkout <= clkout2;endendmodule`timescale 1ns / 1psmodule fd8bits(clk_in,reset,clk_out );input clk_in;input reset;output reg clk_out;reg[3:0] count;always@(posedge clk_in) beginif(!reset)count <= 0;else beginif(count < 7)count <= count + 1;elsecount <= 0;endclk_out <= count[2];endendmodule// 9 分频module fd9bits(clk_in,reset,clk_out );input clk_in;input reset;output reg clk_out;reg[3:0] count;always@(posedge clk_in) beginif(!reset)count <= 0;else beginif(count < 8)count <= count + 1;elsecount <= 0;endclk_out <= count[2];endendmodule// testbenchmodule testbench();reg clk_in;reg reset;reg a;wire clk_out;fd89bits dut(clk_in,reset,a,clk_out);initial beginclk_in= 0;reset = 0;#11;reset = 1;forever begina = 1;#60;a = 0;#20;a = 1;#40;a = 0;#20;a = 1;#40;a = 0;#20;endendalways #10 clk_in = ~clk_in; endmodule//result。

1、半整数分频占空比不为50%//说明:我设计的史上最好用的半整数分频占空比不为50%,包含设计思路module div_5(clk,clk_div,cnt1,cnt2,temp1,temp2);//N+0.5input clk;output clk_div;output reg[31:0]cnt1,cnt2;output reg temp1,temp2;initial begin temp1=0;temp2=1;end //首先进行初始化,temp1=0;temp2=1 parameter N=5; //设定分频系数为N+0.5always @(posedge clk) //temp1上升沿跳变beginif(cnt1==2*N) //2*Nbegin cnt1[31:0]<=32'd0;endelse begin cnt1[31:0]<=cnt1[31:0]+32'd1;endif(cnt1==32'd0) begin temp1<=1;end //高电平时间为N+1;if(cnt1==N+1) begin temp1<=0;end//低电平时间为N;endalways@(negedge clk) //temp2下降沿跳变beginif(cnt2==2*N) //2*Nbegin cnt2[31:0]<=32'd0;endelse begin cnt2[31:0]<=cnt2[31:0]+32'd1;endif(cnt2==32'd0) begin temp2<=0;end //低电平时间为N;if(cnt2==N) begin temp2<=1;end //高电平时间为N+1;endassign clk_div=temp1&&temp2; //逻辑与endmodule//如果要进行N+0.5分频//思路:总的来说要进行N+1+N=2N+1次分频//在时钟的上升沿和下降沿都进行跳变//上升沿进行占空比为N+1比N的时钟temp1;//下降沿进行占空比为N比N+1的时钟temp2;//最后div=temp1&&temp2 即可得到所需要的半整数分频分频5.5仿真结果2、奇数分频占空比为50%//说明:奇数分频。

锁相环频率合成器中整数分频器的设计摘要:本文介绍了整数分频器的电路结构和设计,它应用于Galileo\WCDMA双模卫星接收机中的锁相环(PLL)频率综合成器中。

电路由双模前置分频器(DMP)和可编程分频器(PFD)构成,分频比在513~760范围内可调。

电路采用0.18μm RF CMOS工艺制作,供电电压为1.8V。

仿真结果表明,电路具有良好的稳定性,工作频率为1.5~5.8GHz,完全覆盖了所需的频率范围(2.3~4.4GHz),在4.5GHz工作频率下电流消耗约为3.45mA。

关键词:锁相环;整数分频器;前置双模分频器;可编程分频器近年来,以GPS为代表的卫星导航系统的应用领域不断扩展,与之相关的卫星导航接收机也在不断发展中,从近期的发展趋势看,随着Galileo系统投入使用,卫星导航系统的发展将经历从GPS时代向GNSS (Global Navigation Satellite System)时代的转变,及由主要依赖GPS系统向GPS+Galileo+其它系统的多系统并存的局面转变。

多模接收机在可用性、连续性和性价比上都大大超过单一系统的接收机。

因此,多模兼容是卫星导航接收机未来发展的必然方向。

此外,卫星导航与移动通信的融合,将使卫星导航如虎添翼。

近年来,定位收集和车载移动定位产品销售的大幅增长表明,与移动通信融合是卫星导航应用市场的客观需求和发展方向。

将GPS/Galileo接收机和TD/WCDMA/CDMA2000等新一代蜂窝无线接收机结合形成组合导航定位接收机,可提供无缝室内室外高精度高效导航定位服务,在未来的通信导航领域具有广阔的应用前景。

作为接收机系统最重要的模块,人们对于频率合成器的研究从未中止,经历了直接合成模拟式频率合成器、锁相环频率合成器、直接数字频率合成器几个发展阶段。

锁相环(PLL)频率合成器由于其高频率稳定性、低噪声、可编程、易于集成等突出优点,成为目前频率合成器的主流技术。

基于FPGA 的小数分频器的实现刘亚海,林争辉(同济大学研究生院电路与系统 上海 200092)摘 要:介绍了一种基于FPGA 的双模前置小数分频器的分频原理及电路设计,并用V erilog HDL 编程,在M odelSi mSE 平台下实现分频器的仿真,并用X ilinx 公司的芯片Spartan 3来实现。

关键词:小数分频器;频率合成;FPGA ;V erilog HDL中图分类号:TN 772 文献标识码:B 文章编号:1004373X (2005)0311302Rea l iza tion of D ec i m a l Frequency D iv ider Ba sed on FPGAL I U Yahai ,L I N Zhenghu i(C ircuit and Syste m of Graduate Schoo l ,TongjiU niversity ,Shanghai ,200092,Ch ina )Abs tra c t :T h is paper p resen ts the frequency divisi on theo ry and circu it design of dual modu lu s p reset deci m al frequency dividerbased on FPGA 1T he frequency devider i m p lem en ted w ith a Spartan 3ch i p is described in V erilog HDL ,and si m u lated w ithM odelSi m SE 1Ke yw o rds :deci m al frequency divider ;frequency syn thesize ;FPGA ;V erilog HDL收稿日期:20040914 频率合成技术是现代通讯系统的重要组成部分,他将一个高稳定和高准确度的基准频率,经过四则运算,产生同样稳定度和基准度的频率。