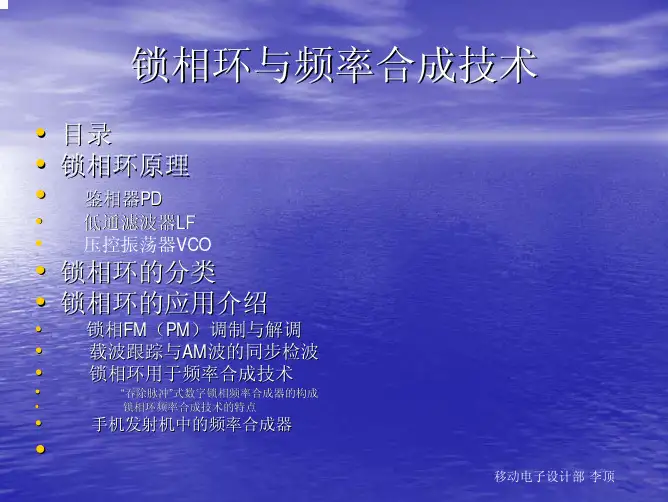

pll频率合成技术简介

- 格式:ppt

- 大小:991.50 KB

- 文档页数:30

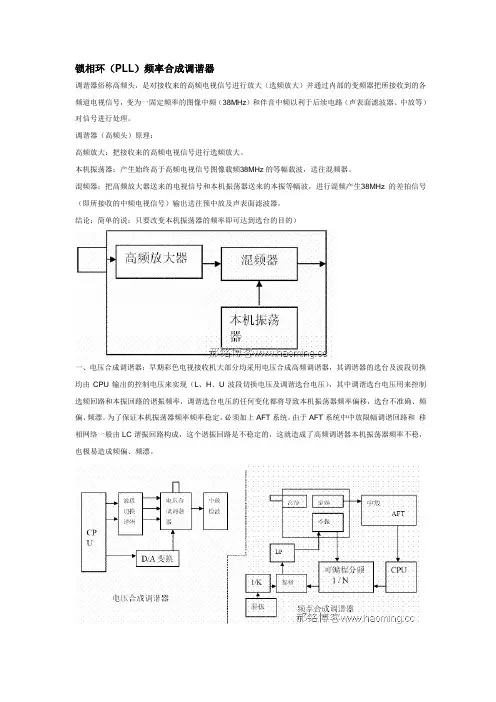

锁相环(PLL)频率合成调谐器调谐器俗称高频头,是对接收来的高频电视信号进行放大(选频放大)并通过内部的变频器把所接收到的各频道电视信号,变为一固定频率的图像中频(38MHz)和伴音中频以利于后续电路(声表面滤波器、中放等)对信号进行处理。

调谐器(高频头)原理:高频放大:把接收来的高频电视信号进行选频放大。

本机振荡器:产生始终高于高频电视信号图像载频38MHz的等幅载波,送往混频器。

混频器:把高频放大器送来的电视信号和本机振荡器送来的本振等幅波,进行混频产生38MHz的差拍信号(即所接收的中频电视信号)输出送往预中放及声表面滤波器。

结论:简单的说:只要改变本机振荡器的频率即可达到选台的目的)一、电压合成调谐器:早期彩色电视接收机大部分均采用电压合成高频调谐器,其调谐器的选台及波段切换均由CPU输出的控制电压来实现(L、H、U波段切换电压及调谐选台电压),其中调谐选台电压用来控制选频回路和本振回路的谐振频率,调谐选台电压的任何变化都将导致本机振荡器频率偏移,选台不准确、频偏、频漂。

为了保证本机振荡器频率频率稳定,必须加上AFT系统。

由于AFT系统中中放限幅调谐回路和移相网络一般由LC谐振回路构成,这个谐振回路是不稳定的,这就造成了高频调谐器本机振荡器频率不稳,也极易造成频偏、频漂。

二、频率合成调谐器1、频率合成的基本含义:是指用若干个单一频率的正弦波合成多个新的频率分量的方法(频率合成调谐器的本振频率是由晶振分频合成的)。

频率合成的方法有很多种。

下图为混频式频率合成器方框图以上图中除了三个基频外还有其“和频”及“差频”输出(还有各个频率的高次谐波输出)。

输出信号的频率稳定性由基准信号频率稳定性决定,而且输出信号频率误差等于各基准信号误差之和,因此要想减少误差除了要提高基准信号稳定度之外还应减少基准信号的个数。

2、锁相环频率合成器:其方框图类似于彩色电视接收机中的副载波恢复电路,只是在输入回路插入了一个基准信号分频器(代替色同步信号输入)而在反馈支路插入一个可编程分频器(代替900移相)。

综合课程设计频率合成器的设计与仿真前言现代通信系统中,为确保通信的稳定与可靠,对通信设备的频率准确率和稳定度提出了极高的要求. 随着电子技术的发展,要求信号的频率越来越准确和越来越稳定,一般的振荡器已不能满足系统设计的要求。

晶体振荡器的高准确度和高稳定度早已被人们认识,成为各种电子系统的必选部件。

但是晶体振荡器的频率变化范围很小,其频率值不高,很难满足通信、雷达、测控、仪器仪表等电子系统的需求,在这些应用领域,往往需要在一个频率范围内提供一系列高准确度和高稳定度的频率源,这就需要应用频率合成技术来满足这一需求。

本次实验利用SystemView实现通信系统中锁相频率合成器的仿真,并对结果进行了分析。

一、频率合成器简介频率合成是指以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出频率的准确度与稳定度与参考频率是一致的。

用来产生这些频率的部件就成为频率合成器或频率综合器。

频率合成器通过一个或多个标准频率产生大量的输出频率,它是通过对标准频率在频域进行加、减、乘、除来实现的,可以用混频、倍频和分频等电路来实现。

其主要技术指标包括频率范围、频率间隔、准确度、频率稳定度、频率纯度以及体积、重量、功能和成本。

频率合成器的合成方法有直接模拟合成法、锁相环合成法和直接数字合成法。

直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。

该方法频率转换时间快(小于100ns),但是体积大、功耗大,成本高,目前已基本不被采用。

锁相频率合成器通过锁相环完成频率的加、减、乘、除运算,其结构是一种闭环系统。

其主要优势在于结构简化、便于集成,且频率纯度高,目前广泛应用于各种电子系统。

直接式频率合成器中所固有的那些缺点,在锁相频率合成器中大大减少。

本次实验设计的是锁相频率合成器。

二、锁相环频率合成器原理2.1 锁相环路设计基础这一部分首先阐明了锁相环的基本原理及构成,导出了环路的相位模型和基本方程,概述了环路的工作过程, 2.1.1锁相环基本原理锁相环(PLL )是一个相位跟踪系统。

新型数字化可编程频率合成器唐如林摘要:频率合成器是从一个或多个参考频率中产生多种频率的器件。

它在信息通信方面得到了广泛的应用,并有新的发展。

本文主要介绍新型数字化可编程频率合成器的原理、特点及其在传输测量仪中的应用。

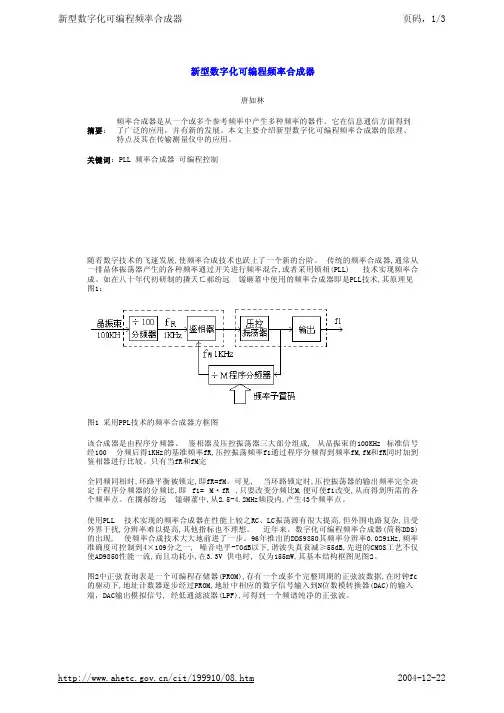

关键词:PLL 频率合成器可编程控制随着数字技术的飞速发展,使频率合成技术也跃上了一个新的台阶。

传统的频率合成器,通常从一排晶体振荡器产生的各种频率通过开关进行频率混合,或者采用锁相(PLL) 技术实现频率合成。

如在八十年代初研制的撛夭ㄈ郝纷远馐砸菙中使用的频率合成器即是PLL技术,其原理见图1:图1 采用PPL技术的频率合成器方框图该合成器是由程序分频器、鉴相器及压控振荡器三大部分组成, 从晶振束的100KHz 标准信号经100 分频后得1KHz的基准频率fR,压控振荡频率f1通过程序分频得到频率fM,fM和fR同时加到鉴相器进行比较。

只有当fR和fM完全同频同相时,环路平衡被锁定,即fR=fM。

可见, 当环路锁定时,压控振荡器的输出频率完全决定于程序分频器的分频比,即f1= M·fR ,只要改变分频比M,便可使f1改变,从而得到所需的各个频率点。

在撊郝纷远馐砸菙中,从2.5-4.2MHz频段内,产生43个频率点。

使用PLL 技术实现的频率合成器在性能上较之RC、LC振荡源有很大提高,但外围电路复杂,且受外界干扰,分辨率难以提高,其他指标也不理想。

近年来,数字化可编程频率合成器(简称DDS)的出现, 使频率合成技术大大地前进了一步。

96年推出的DDS9850其频率分辨率0.0291Hz,频率准确度可控制到4×109分之一, 噪音电平-70dB以下,谐波失真衰减≥55dB,先进的CMOS工艺不仅使AD9850性能一流,而且功耗小,在3.3V 供电时, 仅为155mW,其基本结构框图见图2。

图2中正弦查询表是一个可编程存储器(PROM),存有一个或多个完整周期的正弦波数据,在时钟fc 的驱动下,地址计数器逐步经过PROM,地址中相应的数字信号输入到N位数模转换器(DAC)的输入端,DAC输出模拟信号, 经低通滤波器(LPF),可得到一个频谱纯净的正弦波。

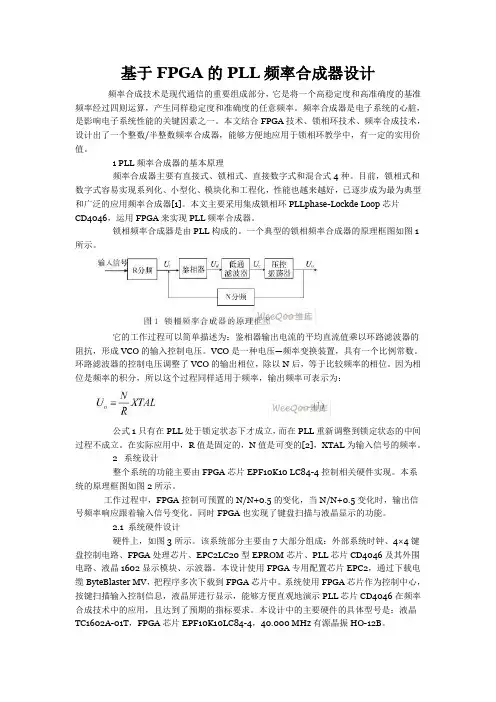

基于FPGA的PLL频率合成器设计频率合成技术是现代通信的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。

频率合成器是电子系统的心脏,是影响电子系统性能的关键因素之一。

本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。

1 PLL频率合成器的基本原理频率合成器主要有直接式、锁相式、直接数字式和混合式4种。

目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。

本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

锁相频率合成器是由PLL构成的。

一个典型的锁相频率合成器的原理框图如图1所示。

它的工作过程可以简单描述为:鉴相器输出电流的平均直流值乘以环路滤波器的阻抗,形成VCO的输入控制电压。

VCO是一种电压—频率变换装置,具有一个比例常数。

环路滤波器的控制电压调整了VCO的输出相位,除以N后,等于比较频率的相位。

因为相位是频率的积分,所以这个过程同样适用于频率,输出频率可表示为:公式1只有在PLL处于锁定状态下才成立,而在PLL重新调整到锁定状态的中间过程不成立。

在实际应用中,R值是固定的,N值是可变的[2],XTAL为输入信号的频率。

2 系统设计整个系统的功能主要由FPGA芯片EPF10K10 LC84-4控制相关硬件实现。

本系统的原理框图如图2所示。

工作过程中,FPGA控制可预置的N/N+0.5的变化,当N/N+0.5变化时,输出信号频率响应跟着输入信号变化。

同时FPGA也实现了键盘扫描与液晶显示的功能。

2.1 系统硬件设计硬件上,如图3所示。

该系统部分主要由7大部分组成:外部系统时钟、4×4键盘控制电路、FPGA处理芯片、EPC2LC20型EPROM芯片、PLL芯片CD4046及其外围电路、液晶1602显示模块、示波器。

认识有理数教学反思

《认识有理数教学反思》

在学习有理数的这段时间里,我感觉自己就像在数学的海洋里遨游,有时风平浪静,有时却波涛汹涌。

一开始,老师在黑板上写下那些数字,正数、负数、零,我眼睛都看直啦!心想:“这都是些啥呀?”特别是负数,那小小的负号,就像一个调皮的小精灵,总是让我迷糊。

记得有一次课堂上,老师问:“同学们,负数表示的意义你们懂了吗?”我心里直打鼓,不敢吭声。

旁边的同桌却自信满满地说:“老师,我懂!负数就是比零还小的数嘛!”老师笑着点头,我心里那个羡慕呀,反问自己:“我咋就没这么快明白呢?”

后来做练习题的时候,那一道道题目就像一个个小怪兽,张牙舞爪地等着我去打败它们。

有时候我能一下子就把它们解决掉,心里那叫一个美,就好像在炎热的夏天吃到了最爱的冰淇淋;可有时候,我却被它们难住了,抓耳挠腮,急得像热锅上的蚂蚁,嘴里嘟囔着:“这题咋这么难啊!”

小组讨论的时候可热闹啦!大家七嘴八舌地说着自己的想法。

“哎呀,这道题我觉得应该这样做!”“不对不对,你那样做错啦!”“那到底该咋办呀?”我们争得面红耳赤,可最后在大家的共同努力下,难题还是被我们攻克了,那种成就感,简直没法形容!

经过这段时间的学习,我发现有理数其实也没那么可怕。

它们就像我的小伙伴,虽然有时候会调皮捣蛋,但只要我用心去了解它们,就能和它们友好相处。

我觉得学习有理数就像爬山,一开始觉得山好高好难爬,但是只要一步一个脚印,坚持往上走,总会到达山顶,看到美丽的风景。

所以呀,遇到困难别害怕,勇敢面对,总会找到解决办法的!。

DDS+PLL 高性能频率合成器的设计与实现

频率合成器是决定电子系统性能的关键设备,随着通信、数字电视、卫

星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越

来越高的要求。

频率合成理论自20 世纪30 年代提出以来,已取得了迅速的

发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率

合成技术三种基本频率合成方法。

直接频率合成技术原理简单,易于实现,

频率转换时间短,但是频率范围受限,且输出频谱质量差。

锁相频率合成技

术(PLL)具有输出频带宽、工作频率高、频谱质量好的优点,但是频率分辨率

和频率转换速度却很低。

直接式数字频率合成技术(DDS)的频率分辨率高、

频率转换时间快、频率稳定度高、相位噪声低,但目前尚不能做到宽带,频

谱纯度也不如PLL。

低相位噪声、高纯频谱、高速捷变和高输出频段的频率

合成器已成为频率合成发展的主要趋势,传统的单一合成方式很难兼顾上述

各项性能指标,达到现代通信系统对频率合成器的要求。

本文采用DDS 和

PLL 相结合的方法,设计一个应用于(GSM 1 800 MHz 系统中的频率合成器,其中输出频带为1 805~1 880 MHz,分辨率为200 kHz,相位噪声为-80 dBc /Hz@1 kHz,频率误差为5 kHz,杂波抑制大于50 dB。

1 电路设计

1.1 设计原理

DDS 直接激励PLL 的频率合成技术,与单纯的PLL 技术相比,作为参考

源的DDS 具有很高的频率分辨率,可以在不改变PLL 分频比的情况下,提。

pll工作原理PLL,全称为Phase-Locked Loop。

它是一种电子电路,具有频率合成和时钟重构的功能,被广泛应用于通信、控制、测量和工业等领域。

PLL的基本原理是将一个输入信号与一个本地信号进行比较,将比较结果反馈给控制器,以调整本地信号的频率和相位,使其与输入信号保持同步。

下面我们来分步骤阐述PLL的工作原理。

第一步,当输入信号f_in进入PLL时,首先经过一个分频器,将其频率降低到与一个参考信号f_ref相同的频率。

这个参考信号可以是一个参考振荡器产生的稳定信号,也可以是来自于其他源的稳定信号。

分频比为N,即将f_in分频N倍,得到f_p = f_in/N,这样使输入信号与参考信号在频率上保持一致,方便进行比较和调整。

第二步,将分频后的f_p信号与参考信号f_ref进行比较,得到一个误差电压e(t)。

这个误差电压代表了f_p与f_ref之间的相位误差,如果f_p和f_ref相位相同,那么误差电压为0;如果它们相位不同,那么误差电压将是一个正负交替的信号。

第三步,将误差电压e(t)反馈给控制器,其中最常用的控制器是一个环路滤波器(loop filter)。

环路滤波器是一个积分器,它将误差电压e(t)进行积分,并将积分结果作为输出信号V_c(t)。

这个输出信号将被发送给一个控制电压控制振荡器(VCO),作为其输入信号。

第四步,控制器的输出信号(V_c(t))被加到VCO的控制电压输入端,控制VCO的频率。

这样在VCO产生的本地信号f_out的频率将被调整,以减小f_p与f_ref之间的相位误差。

反馈环路会不断地进行调整,直到f_p与f_ref之间的相位差为0,也就是说f_out与f_in频率相同且相位相同。

这就完成了一个PLL的工作过程。

总的来说,PLL是一种非常重要的电子电路,它可以实现高精度的频率合成和时钟重构,可以提高通信系统的稳定性,增强信号质量,扩展数据传输能力等。

基于锁相环(PLL)L波段的频率合成技术赵慧娟【摘要】Frequency synthesizer is the core component of the electronic equipment,the performance of the performance of the overall performance of the electronic equipment.In this paper,a phase locked loop frequency technique based on phase locked loop (PLL) L band is studied.Its design scheme uses MC145152 to realize the phase locked loop,the external loop filter LPF and the voltage controlled oscillator VCO and other devices to achieve,with a strong research and design value.%频率合成器是电子设备的核心部件,其性能的优劣影响电子设备的整体性能。

本文研究了一种基于锁相环(PLL)L波段的锁相频率技术。

其设计方案使用MC145152来实现锁相环路,外加环路滤波器LPF和压控振荡器VCO等器件来实现,具有较强的研究设计价值。

【期刊名称】《电子测试》【年(卷),期】2016(000)001【总页数】4页(P24-27)【关键词】频率合成;锁相环;压控振荡器【作者】赵慧娟【作者单位】九州职业技术学院,江苏徐州,221116【正文语种】中文人类进入信息社会和知识经济发展的时代,信息产业是未来发展的重点,将为社会创造巨大的经济效益。

因此,信息产业的兴衰,将是21世纪衡量和再现一个民族创新和发展能力、生存和竞争能力的重要标志。

基于锁相环的频率合成电路设计-技术方案0 引言锁相环简称PLL,是实现相位自动控制的一门技术,早期是为了解决接收机的同步接收问题而开发的,后来应用在电视机的扫描电路中。

由于锁相技术的发展,该技术已逐渐应用到通信、导航、雷达、计算机到家用电器的各个领域。

自从20世纪70年代起,随着集成电路的发展,开始出现集成的锁相环器件、通用和专用集成单片锁相环,使锁相环逐渐变成一个低成本、使用简便的多功能器件。

如今,PLL 技术主要应用在调制解调、频率合成、彩电色幅载波提取、雷达、FM 立体声解码等各个领域。

随着数字技术的发展,还出现了各种数字PLL器件,它们在数字通信中的载波同步、位同步、相干解调等方面起着重要的作用。

随着现代电子技术的飞快发展,具有高稳定性和准确度的频率源已经成为科研生产的重要组成部分。

高性能的频率源可通过频率合成技术获得。

随着大规模集成电路的发展,锁相式频率合成技术占有越来越重要的地位。

由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

1 锁相环及频率合成器的原理1.1 锁相环原理PLL是一种反馈控制电路,其特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因PLL可以实现输出信号频率对输入信号频率的自动跟踪,所以PLL通常用于闭环跟踪电路。

PLL在工作的过程中,当输出信号的频率与输入信号的频率相同时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是PLL名称的由来。

PLL通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,PLL组成的原理框图如图1所示。

PLL中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图2所示。

S 波段DDS+PLL 频率合成技术研究(S波段是指频率范围在 1.55—3.4GHz的电磁波频段,U波段是指频率范围在470-798MHz的电磁波频段。

CMMB的卫星信号使用S波段进行覆盖,城市地面信号使用U波段进行覆盖。

)DDS 直接数字频率合成参考源在线路设计中采用了AD 公司的AD7008, 构成一个输出频率为10. 7MHz 的DDS 直接数字频率合成参考源, 其时钟频率为40MHz.DDS+PLL 频率合成器由DDS 直接数字频率合成器作为参考源, 驱动PLL 环路。

在线路设计中采用AD 公司的AD7008 直接数字频率合成芯片和QUALCOMM 公司的Q3236 频率合成芯片构成一个DDS+PLL 频率合成器。

DDS+PLL 频率合成源中的PLL 采用单环频率合成技术, 以使DDS+PLL 频率合成器其结构简单, 性能稳定。

基于DDS 技术的杂散分析及抑制方法DDS 的杂散主要来自三个方面:*相位截断引入的杂散*存储器的幅度量化误差*DAC 转换误差2.1 相位截断引入的杂散在DDS 中, 一般相位累加器的位数N 大于ROM的寻址位数P,因此累加器的输出寻址其N 一P 个低位就必须舍掉,这样就不可避免地产生相位误差,称为相位截断误差,表现在输出频谱上就是杂散分量。

因为DDS 输出信号通常是正弦信号,因此它的相位截断具有明显的周期性。

这相当于周期性的引入一个截断误差,最终影响就是输出信号带有一定的谐波分量。

相位截断并不是每个输出点都产生杂散。

它们的大小取决于三个因素:累加器的位数N,寻址位数P,频率控制字FCW。

杂散分量分布在基频两边,是DDS 杂散的主要来源。

2.2 幅度量化引入的杂散由于DDS 内部波形存储器中存储的正弦幅度值是用二进制表示的, 对于越过存储器字长的正弦幅度值必须进行量化处理,这样就引人了量化误差。

幅度量化主要有两种方式,即舍入量化和截尾量化,实际中DDS 多采用舍入量化方式。