第3章-逻辑门电路.

- 格式:doc

- 大小:821.50 KB

- 文档页数:12

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

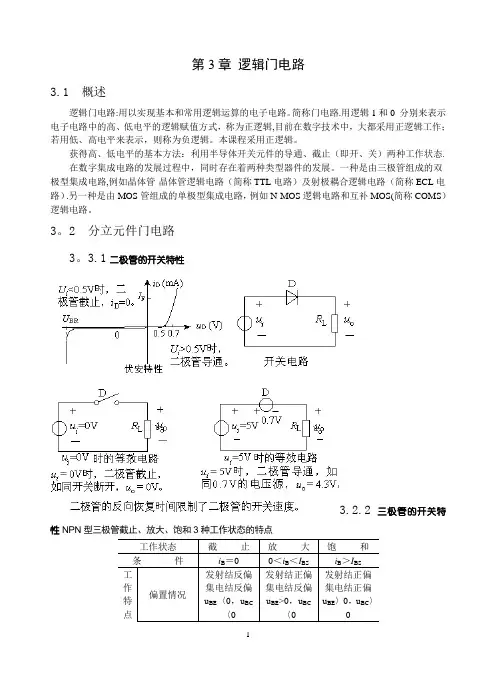

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

路。

简称门电路。

5V一、TTL 与非门图3-1 典型TTL 与非门电路3.2 TTL 集成门电路•数字集成电路中应用最广的为TTL 电路(Transister-Transister-Logic 的缩写)•由若干晶体三极管、二极管和电阻组成,TTL 集成电路有54/74系列 ①输出高电平UOH 和输出低电平UOL 。

•输出高电平U OH:至少有一个输入端接低电平时的输出电平。

•输出低电平U OL:输入全为高电平时的输出电平。

• 电压传输特性的截止区的输出电压UOH=3.6V,饱和区的输出电压UOL=0.3V。

一般产品规定U OH≥2.4V、U OL<0.4V时即为合格。

二、TTL与非门的特性参数③开门电平U ON 和关门电平U OFF 。

开门电平U ON 是保证输出电平达到额定低电平(0.3V )时,所允许输入高电平的最低值,表示使与非门开通的最小输入电平。

通常U ON =1.4V ,一般产品规定U ON ≤1.8V 。

关门电平U OFF 是保证输出电平为额定高电平(2.7V 左右)时,允许输入低电平的最大值,表示与非门关断所允许的最大输入电平。

通常U OFF ≈1V ,一般产品要求U OFF ≥0.8V 。

5). 扇入系数Ni和扇出系数N O 是指与非门的输入端数目。

扇入系数Ni是指与非门输出端连接同类门的个数。

反扇出系数NO映了与非门的带负载能力。

6)输入短路电流I IS 。

当与非门的一个输入端接地而其余输入端悬空时,流过接地输入端的电流称为输入短路电流。

7)8)平均功耗P 指在空载条件下工作时所消耗的电功率。

三、TTL门电路的改进 74LS系列 性能比较好的门电路应该是工作速度既快,功耗又小的门电路。

因此,通常用功耗和传输延迟时间的乘积(简称功耗—延迟积或pd积)来评价门电路性能的优劣。

74LS系列又称低功耗肖特基系列。

74LS系列是功耗延迟积较小的系列(一般t pd<5 ns,功耗仅有2 mW) 并得到广泛应用。

3 逻辑门电路MOS 逻辑门电路3.1.2 求下列情况下TTL 逻辑门的扇出数:(1)74LS 门驱动同类门;(2)74LS 门驱动74ALS 系列TTL 门。

解:首先分别求出拉电流工作时的扇出数N OH 和灌电流工作时的扇出数N OL ,两者中的最小值即为扇出数。

从附录A 可查得74LS 系列电流参数的数值为I OH =,I OL =8mA ,I IH =,I IL =;74ALS 系列输入电流参数的数值为I IH =,I IL =,其实省略了表示电流流向的符号。

(1) 根据(3.1.4)和式()计算扇出数74LS 系列驱动同类门时,输出为高电平的扇出数0.4200.02OH OH IH I mA N I mA=== 输出为低电平的扇出数 8200.4OL OL IL I mA N I mA ===所以,74LS 系列驱动同类门时的扇出数N O 为20。

(2) 同理可计算出74LS 系列驱动74ALS 系列时,有0.4200.02OH OH IH I mA N I mA=== 8800.1OL OL IL I mA N I mA === 所以,74LS 系列驱动74ALS 系列时的扇出数N O 为20。

3.1.4 已知图题所示各MOSFET 管的T V =2V ,忽略电阻上的压降,试确定其工作状态(导通或截止)。

解:图题3.1.4(a )和(c )的N 沟道增强型MOS ,图题(b )和(d )为P 沟道增强型MOS 。

N 沟道增强型MOS 管得开启电压V T 为正。

当GS V <V T 时,MOS 管处于截止状态;当GS V ≥V T ,且DS v ≥(GS V —V T )时,MOS 管处于饱和导通状态。

对于图题3.1.4(a ),GS V =5V ,DS v =5V ,可以判断该MOS 管处于饱和导通状态。

对于图题3.1.4(c ),GS V =0V <V T ,所以MOS 管处于截止状态。

第三章逻辑门电路[题3.1] 选择题1. 三态门输出高阻状态时,是正确的说法。

A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动2. 以下电路中可以实现“线与”功能的有。

A.与非门B.三态输出门C.集电极开路门D.漏极开路门3.以下电路中常用于总线应用的有。

A.T S L门B.O C门C.漏极开路门D.C M O S与非门4.三极管作为开关使用时,要提高开关速度,可。

A.降低饱和深度B.增加饱和深度C.采用有源泄放回路D.采用抗饱和三极管5.T T L电路在正逻辑系统中,以下各种输入中相当于输入逻辑“1”。

A.悬空B.通过电阻 2.7kΩ接电源C.通过电阻 2.7kΩ接地D.通过电阻510Ω接地6.对于T T L与非门闲置输入端的处理,可以。

A.接电源B.通过电阻3kΩ接电源C.接地D.与有用输入端并联7.C M O S数字集成电路与T T L数字集成电路相比突出的优点是。

A.微功耗B.高速度C.高抗干扰能力D.电源范围宽8.逻辑表达式Y=AB可以用实现。

A.正或门B.正非门C.正与门9.要使TTL与非门工作在转折区,可使输入端对地外接电阻R I。

A.>R ONB.<R OFFC.R OFF<R I<R OND.>R OFF10.与CT4000系列相对应的国际通用标准型号为。

A.CT74S肖特基系列B. CT74LS低功耗肖特基系列C.CT74L低功耗系列D. CT74H高速系列[题3.2] 判断题(正确打√,错误的打×)1.TTL与非门的多余输入端可以接固定高电平。

()2.当TTL与非门的输入端悬空时相当于输入为逻辑1。

()3.普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

()4.CMOS OD门(漏极开路门)的输出端可以直接相连,实现线与。

()5.CMOS或非门与TTL或非门的逻辑功能完全相同。

()6.三态门的三种状态分别为:高电平、低电平、不高不低的电压。

第三章逻辑门电路[题3.1] 选择题1. 三态门输出高阻状态时,是正确的说法。

A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动2. 以下电路中可以实现“线与”功能的有。

A.与非门B.三态输出门C.集电极开路门D.漏极开路门3.以下电路中常用于总线应用的有。

A.TS L门B.O C门C.漏极开路门D.CM OS与非门4.三极管作为开关使用时,要提高开关速度,可。

A.降低饱和深度B.增加饱和深度C.采用有源泄放回路D.采用抗饱和三极管5.T TL电路在正逻辑系统中,以下各种输入中相当于输入逻辑“1”。

A.悬空B.通过电阻 2.7kΩ接电源C.通过电阻 2.7kΩ接地D.通过电阻510Ω接地6.对于T T L与非门闲置输入端的处理,可以。

A.接电源B.通过电阻3kΩ接电源C.接地D.与有用输入端并联7.C MO S数字集成电路与TT L数字集成电路相比突出的优点是。

A.微功耗B.高速度C.高抗干扰能力D.电源范围宽8.逻辑表达式Y=AB可以用实现。

A.正或门B.正非门C.正与门9.要使TTL与非门工作在转折区,可使输入端对地外接电阻R I。

A.>R ONB.<R OFFC.R OFF<R I<R OND.>R OFF10.与CT4000系列相对应的国际通用标准型号为。

A.CT74S肖特基系列B. CT74LS低功耗肖特基系列C.CT74L低功耗系列D. CT74H高速系列[题3.2] 判断题(正确打√,错误的打×)1.TTL与非门的多余输入端可以接固定高电平。

()2.当TTL与非门的输入端悬空时相当于输入为逻辑1。

()3.普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

()4.CMOS OD门(漏极开路门)的输出端可以直接相连,实现线与。

()5.CMOS或非门与TTL或非门的逻辑功能完全相同。

()6.三态门的三种状态分别为:高电平、低电平、不高不低的电压。

3 逻辑门电路3.1 MOS 逻辑门电路3.1.2 求下列情况下TTL 逻辑门的扇出数:(1)74LS 门驱动同类门;(2)74LS 门驱动74ALS 系列TTL 门。

解:首先分别求出拉电流工作时的扇出数N OH 和灌电流工作时的扇出数N OL ,两者中的最小值即为扇出数。

从附录A 可查得74LS 系列电流参数的数值为I OH =0.4mA ,I OL =8mA ,I IH =0.02mA,I IL =0.4mA ;74ALS 系列输入电流参数的数值为I IH =0.02mA ,I IL =0.1mA ,其实省略了表示电流流向的符号。

(1) 根据(3.1.4)和式(3.1.5)计算扇出数74LS 系列驱动同类门时,输出为高电平的扇出数0.4200.02OH OH IH I mA N I mA=== 输出为低电平的扇出数 8200.4OL OL IL I mA N I mA ===所以,74LS 系列驱动同类门时的扇出数N O 为20。

(2) 同理可计算出74LS 系列驱动74ALS 系列时,有0.4200.02OH OH IH I mA N I mA=== 8800.1OL OL IL I mA N I mA === 所以,74LS 系列驱动74ALS 系列时的扇出数N O 为20。

3.1.4 已知图题3.1.4所示各MOSFET 管的T V =2V ,忽略电阻上的压降,试确定其工作状态(导通或截止)。

解:图题3.1.4(a )和(c )的N 沟道增强型MOS ,图题3.1.4(b )和(d )为P 沟道增强型MOS 。

N 沟道增强型MOS 管得开启电压V T 为正。

当GS V <V T 时,MOS 管处于截止状态;当GS V ≥V T ,且DS v ≥(GS V —V T )时,MOS 管处于饱和导通状态。

对于图题3.1.4(a ),GS V =5V ,DS v =5V ,可以判断该MOS 管处于饱和导通状态。

对于图题3.1.4(c ),GS V =0V <V T ,所以MOS 管处于截止状态。

P 沟道增强型MOS 管得开启电压V T 为负。

当GS V >V T 时,MOS 管处于截止状态;当GS V ≤V T ,且DS v ≤(GS V —V T )时,MOS 管处于饱和导通状态。

对于图题3.1.4(b ),GS V =0V >﹣2V ,该MOS 管处于截止状态。

对于图题3.1.4(d ),GS V =-5V ,GS V =﹣5V ,可以判断该MOS 管处于饱和导通状态。

3.1.5 为什么说74HC 系列CMOS 与非门在﹢5V 电源工作时,输入端在以下四种接法下都属于逻辑0:(1)输入端接地;(2)输入端低于1.5V 的电源;(3)输入端同类与非门的输出低电压0.1V ;(4)输入端接10k Ω的电阻到地。

解:对于74HC 系列CMOS 门电路来说,输出和输入低电平的标准电压值为:V OL =0.1V , V IL =1.5V 。

因此,有:(1) I v =0<V IL =1.5V ,属于逻辑0。

(2) I v <1.5V=V IL ,属于逻辑0。

(3) I v =0.1V <V IL =1.5V ,属于逻辑0。

(4) 由于CMOS 管得栅极电流非常小,通常小于1uA ,在10k Ω电阻上产生的压降小于10mV 即I v <0.01V <V IL =1.5V ,故亦属于逻辑0。

3.1.6 试分析图题3.1.6所示的电路,写出其逻辑表达式,说明它是说明逻辑电路?解:该电路由两部分组成,如图题3.1.6所示,细线左边为一级与非门,虚线右边组成与或非门,其中T 1N 和T 2N 并联实现与功能,两者再与T 3N 串联实现或功能。

与非门的输出X AB =。

与或非门的输出L 为()()L A B X A B AB AB AB AB =+=+=+=该电路实现同或功能。

3.1.7 求图题3.1.7所示电路的输出逻辑表达式。

解:图题3.1.7所示电路中,1234,,,L AB L BC L D L ===实现与功能,即4123L L L L =⋅⋅,而4L L E =⋅,所以输出逻辑表达式为L AB BC D E =⋅⋅⋅。

3.1.8 用三个漏极开路与非门74HC03和一个TTL 与非门74LS00实现图题3.1.7所示的电路,已知CMOS 管截止时的漏电流I OZ =5uA, 试计算R P(min)和R P(max)。

解:第一级的两个与非门和一个非门用漏极开路与非门74HC03组成,第二级的与非门用TTL 与非门74LS00实现。

从附录A 查得74HC 系列的参数为:V OL(max)=0.33V ,I OL(max)=4 mA ,V OH(min)=3.84V ;74LS 系列的参数为:I IL(max)=0.4mA ,I IH(max)=0.02mA 。

因为三个漏极开路门的公共上拉电阻R P 的下端74LS00的一个输入端,即:在灌电流情况下,求出R P 的最小值:(max)(min)(max)()(50.33) 1.3(40.4)DD OL p OL IL total V V V R k I I mA--==≈Ω-- 在拉电流情况下,求出R P 的最大值(min)(max)()()(5 3.84)33.1(0.00530.02)DD OH p OZ total IH total V V V R k I I mA--==≈Ω+⨯+ 3.1.9 .图题.3.1.9表示三态门作总线传输的示意图,图中n 个三态门的输出接数据传输总线,D 1、D 2、…、n D 为数据输入端,CS 1、CS 2、…、i CS 为片选信号输入端。

试问:(1)CS 信号如何进行控制,以便数据D 1、D 2、…、n D 通过该总线进行正常传输;(2)CS 信号能否有两个或两个以上同时有效?如果CS 出现两个或两个以上有效,可能发生什么情况?(3)如果CS 信号均无效,总线处在什么状态?解:(1)根据图题3.1.9可知,片选信号CS 1、CS 2、…、i CS 为高电平有效,当i CS =1时,第i 个三态门被选中,其输入数据被送到数据传输总线上。

根据数据传输的速度,分时地给CS 1、CS 2、…、i CS 端以正脉冲信号,使其相应的三态门的输出数据能分时地到达总线上。

(2)CS 信号不能有两个或两个以上同时有效,否则两个不同的信号将在总线上发生冲突。

即总线不能同时既为0又为1。

(3)如果所有CS 信号均无效,总线处于高阻状态。

3.1.10 某厂生产的双互补对及反相器(4007)引出端如图题3.1.10所示,试分别连接:(1)三个反相器;(2)三输入端或非门;(3)三输入端与非门;(4)或与非门[()L C A B =+];(5)传输门(一个非门控制两个传输门分时传送)。

解:(1)三个反相器将图题3.1.10所示电路按下列方式连接,可以得到三个反相器。

①8、13相连,6端为输入,8端为输出,14端接V DD,7端接地;②1、5相连,3端为输入,5端为输出,2端接V DD,4端接地;③10端为输入,12端为输出,11端接V DD,9端接地。

(2)三输入端或非门电路图如图题解3.1.10(a)所示。

(3)三输入端与非门电路图如图题解3.1.10(b)所示。

(4)或与非门电路图如图题解3.1.10(c)所示。

(5)传输门电路图如图题解3.1.10(d)所示,由6端输入的信号控制TG1、TG2、分时传送数据。

6端接低电平时,TG1、导通,2端得数据传送到12端;6端接高电平时,TG2导通,4端得数据传送到12端。

3.1.11试分析图题3.1.11所示某CMOS器件的电路,写出其逻辑表达式,说明它是什么逻辑电路。

解:电路由两个输入反相器、一个输出反相器、一个传输门T1、T2、和T3构成的电路组成。

传输门由B和B控制,当B=0时传输门导通,当B=1时传输门截止。

T1、T2、和T3构成电路的工作状态由B控制,当B=1时T1、T3均截止,T1、T2、和T3构成的电路不工作;当B=0时T1、T3均导通,T1、T2和T3构成的电路工作,并且起反相作用,其输出等于A。

综上所述,当B=0时,T1、T2、和T3构成的电路不工作,传输门导通,输出L=A;当B=1=。

列出真值表如表题解3.1.11时T1、T2、和T3构成的电路工作,传输门截止,输出L A=+=⊕,故电路为异或门电路。

所示。

其逻辑表达式L AB AB A B3.1.12试分析图题3.1.12所示的CMOS电路,说明它们的逻辑功能。

解:对于图题3.1.12(a)所示的CMOS电路,当EN=0时,T P2和T N2均导通,T P1和=;当EN=1时,T P2和T N2均截止,无论A为高电平T N2构成的的反相器正常工作,L A还是低电平,输出端均为高阻状态,其真值表如表题解3.1.12所示,该电路是低电平使能三态非门,其表示符号如图题解3.1.12(a)所示。

图题3.1.12(b)所示的CMOS电路,EN=0时,T P2导通,或非门打开,T P1和T N1构成的反相器正常工作,L=A;当EN=1时,T P2截止,或非门输出低电平,使T N1截止,输出端处于高阻状态,该电路是低电平使能三态缓冲器,其标示符号如图题解3.1.12(b)所示。

同理可以分析图题3.1.12(c)和图题3.1.12(d)所示的CMOS电路,它们分别为高电平使能三态缓冲器和低电平使能三态非门,其标示符号分别如图题解3.1.12(c)和图题解3.1.12(d )所示。

3.1.13 试分析图题3.1.13所示传输门的电路,写出其逻辑表达式,说明它是说明逻辑电路。

解:对于图题3.1.13所示的电路,输入信号A 作为传输门的控制信号,输入信号B 通过传输门与输出L 相连。

当A=0时,传输门TG 1导通,TG 2断开,L=B ;当A=1时,传输门TG 1断开,TG 2导通,L B =;其真值表如表题解3.1.13所示,该电路实现异或功能,L A B =⊕。

3.1.14 由CMOS 传输门构成的电路如图题3.1.14所示,试列出其真值表,说明该电路的逻辑功能。

解:当CS=1时,4个传输门均为断开状态,输出处于高阻状态。

当CS=0时,4个传输门的工作状态由A 和B 决定,A=B=0时,TG 1和TG 2导通,TG 3和TG 4截止,L=1。

依此分析电路可以列出真值表如表题解3.1.14所示,根据真值表可得L A B =+。

该电路实现三态输出的2输入的或非功能。

3.2 TTL逻辑门电路3.2.2为什么说TTL与非门的输入端在以下四种接法下,都属于逻辑1:(1)输入端悬空;(2)输入端接高于2V的电源;(3)输入端接同类与非门的输出高电压3.6V;(4)输入端接10kΩ电阻到地。