二级运算放大器

- 格式:docx

- 大小:3.00 MB

- 文档页数:8

目录1. 设计指标 (1)2. 运算放大器主体结构的选择 (1)3. 共模反馈电路(CMFB)的选择 (1)4. 运算放大器设计策略 (2)5. 手工设计过程 (2)5.1 运算放大器参数的确定 (2)5.1.1 补偿电容Cc和调零电阻的确定 (2)5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3)5.1.3 确定M1和M2的宽长比 (3)5.1.4确定M5、M6的宽长比 (3)5.1.5 确定M7、M8、M9和M10宽长比 (3)5.1.6 确定M3和M4宽长比 (3)5.1.7 确定M11、M12、M13和M14的宽长比 (4)5.1.8 确定偏置电压 (4)5.2 CMFB参数的确定 (4)6. HSPICE仿真 (5)6.1 直流参数仿真 (5)6.1.1共模输入电压范围(ICMR) (5)6.1.2 输出电压范围测试 (6)6.2 交流参数仿真 (6)6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6)6.2.2 共模抑制比(CMRR)的仿真 (7)6.2.3电源抑制比(PSRR)的仿真 (8)6.2.4输出阻抗仿真 (9)6.3瞬态参数仿真 (10)6.3.1 转换速率(SR) (10)6.3.2 输入正弦信号的仿真 (11)7. 设计总结 (11)附录(整体电路的网表文件) (12)采用折叠式结构的两级全差分运算放大器的设计1. 设计指标5000/ 2.5 2.551010/21~22v DD SS L out dias A V VV V V VGB MHz C pF SR V s V V ICMR V P mWµ>==−==>=±=−≤的范围2. 运算放大器主体结构的选择图1 折叠式共源共栅两级运算放大器运算放大器有很多种结构,按照不同的标准有不同的分类。

从电路结构来看, 有套筒式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。

二级运算放大器哈尔滨理工大学软件学院模拟IC课程设计报告课程模拟IC设计题目二级运算放大器专业集成电路设计与集成班级集成10-2班学生唐贝贝学号1014020227指导老师陆学斌2013年6月14日目录1.课程设计目的…………………………………………………2.课程设计题目描述和要求……………………………………3.课程设计具体内容……………………………………………3.1 设计过程分析……………………………………………3.2使用软件…………………………………………………3.3 原理图……………………………………………………3.4 仿真网表…………………………………………………3.5波形分析…………………………………………………4.心得体会………………………………………………………一、课程设计目的1.熟悉并掌握Hspice与cosmosScope软件的使用。

2.熟练应用Hspice仿真网表并修改分析网表,学会用comosScope查看分析波形。

3.锻炼学生独立完成二级运算放大器的能力。

4. 在扎实的基础上强化实践能力,把模拟IC理论实践化。

二、课程设计题目描述和要求设计指标:静态功耗:小于5mw开环增益:大于70dB单位增益带宽大于5MHz相位裕量:大于60度转换速率(SR)大于20V/us共模抑制比:大于60dB电源抑制比:大于70dB输入失调:小于1mV负载电容:2-4pF要求:1、手工计算出每个晶体管的宽长比。

通过仿真验证设计是否正确,保证每个晶体管的正常工作状态。

2、使用Hspice工具得到电路相关参数仿真结果,包括:幅频和相频特性(低频增益,相位裕度,单位增益带宽)、CMRR、PSRR、共模输入输出范围、SR 等。

3、每个学生应该独立完成电路设计,设计指标比较开放,如果出现雷同按不及格处理。

4、完成课程设计报告的同时需要提交仿真文件,包括所有仿真电路的网表,仿真结果。

5、相关问题参考教材第六章,仿真问题请查看HSPICE手册。

两级运放的自激现象微波eda摘要:1.两级运放的自激现象简介2.微波EDA技术在电路设计中的应用3.两级运放自激现象与微波EDA技术的关联4.利用微波EDA技术解决两级运放自激现象的方法5.实例分析与实践正文:众所周知,两级运放的自激现象是电子电路设计中的一大挑战。

在微波电路设计中,这种现象可能导致信号失真、噪声增加、频率响应恶化等问题。

因此,研究如何解决两级运放自激现象具有重要意义。

本文将介绍两级运放的自激现象及其解决方法,并探讨微波EDA技术在其中的应用。

首先,我们来了解一下两级运放的自激现象。

运算放大器是一种模拟电路,具有很高的增益和带宽。

当两级运放级联时,如果本级输出信号被本级或下级放大,就可能产生自激振荡。

这种振荡会导致电路性能的下降,因此在设计过程中必须加以解决。

微波EDA(Electronic Design Automation)技术是现代电子电路设计的重要工具,它可以在计算机上进行电路仿真、分析和优化。

在两级运放自激现象的解决中,微波EDA技术发挥着重要作用。

通过微波EDA技术,设计人员可以在短时间内对电路进行修改、仿真和分析,从而找到合适的解决方案。

接下来,我们来看一下如何利用微波EDA技术解决两级运放自激现象。

1.利用微波EDA技术进行电路仿真,找到可能导致自激现象的关键环节。

2.对关键环节进行分析,了解其对电路性能的影响。

3.针对分析结果,对电路进行优化。

这可能包括调整元件参数、增加滤波器等措施。

4.重新进行仿真和分析,验证优化方案的有效性。

5.如果必要,重复步骤3和4,直到电路性能满足设计要求。

以下是一个实例分析:假设我们设计一个两级放大器,第一级为放大器A,第二级为放大器B。

在仿真过程中发现,两级放大器存在自激现象。

我们可以通过以下步骤解决:1.利用微波EDA技术,找到放大器A的输出信号被放大器B放大后,重新输入到放大器A的反馈环路,从而产生自激振荡。

2.分析放大器A的输入和输出信号,发现输入信号的幅度和相位变化较小,而输出信号存在较大的幅度和相位波动。

在探讨op07+lm358二级运放差分放大电路计算推导这一主题时,我们首先需要了解什么是op07和lm358,它们分别有怎样的特性和用途。

op07是一款精密运算放大器,具有高增益、低偏移电压和低噪声等特点,适用于精密测量和控制系统。

而lm358是一款双运放芯片,常用于对低功耗和成本敏感的应用中。

接下来,我们可以通过差分放大电路的基本原理来推导op07+lm358二级运放差分放大电路的计算方法。

差分放大电路是一种常见的运放电路,其主要作用是将两个输入信号进行差分放大,从而得到输出信号。

在推导过程中,我们需要考虑输入偏置电流、输入偏置电压、增益等因素,并根据实际电路特性进行适当的近似和假设,最终得到该电路的计算公式和推导过程。

在文章中,不仅要提及op07+lm358二级运放差分放大电路的具体特性和示意图,还需要详细介绍计算推导的步骤和公式。

还可以适当举例说明其在实际应用中的价值和意义,以及对电路参数变化的敏感度与稳定性等方面的深入分析。

总结部分,应该对文章的主要内容进行概括和回顾,强调op07+lm358二级运放差分放大电路的设计和计算方法,以及其在实际工程中的应用前景和发展趋势。

对于个人观点和理解,可以加入对差分放大电路及相关运放电路设计的思考和体会,同时共享对新技术和新趋势的看法和预测。

我将根据以上要求撰写一篇有关op07+lm358二级运放差分放大电路计算推导的文章,并确保在内容中多次提及指定的主题文字。

文章将以非Markdown格式的普通文本撰写,遵循知识文章格式,总字数大于3000字。

希望这篇文章能够帮助您更深入地理解这一主题,并对相关内容有所启发。

op07和lm358分别作为精密运算放大器和双运放芯片,它们在电子工程领域拥有着广泛的应用。

op07因其高增益、低偏移电压和低噪声等特点,常被用于需要精准测量和控制的系统中,例如测量仪器、传感器信号处理、精密计量等领域。

而lm358则是一款低功耗、成本敏感的双运放芯片,常见于电源管理、信号调理、仪表驱动和传感器信号调理等领域。

二级运算放大器设计

二级运算放大器是一种具有高增益和稳定性的放大器,在滤波器模拟电路和数据转换电路中有广泛应用。

在设计二级运算放大器时,需要选择合适的电路参数和优质元器件,以实现高增益和稳定性的输出信号。

失调电压可以通过调整电路参数和选择优质元器件得到降低。

在实际应用中,需要根据具体需求选择合适的二级运算放大器,并根据实际情况进行电路调整和参数优化,以实现最佳性能。

二级运算放大器的设计需要综合考虑各种因素,包括输入信号范围、输出信号要求、电源电压、功耗等。

选择合适的元器件和电路参数,并进行相应的仿真和测试,可以获得高质量的运算放大器设计。

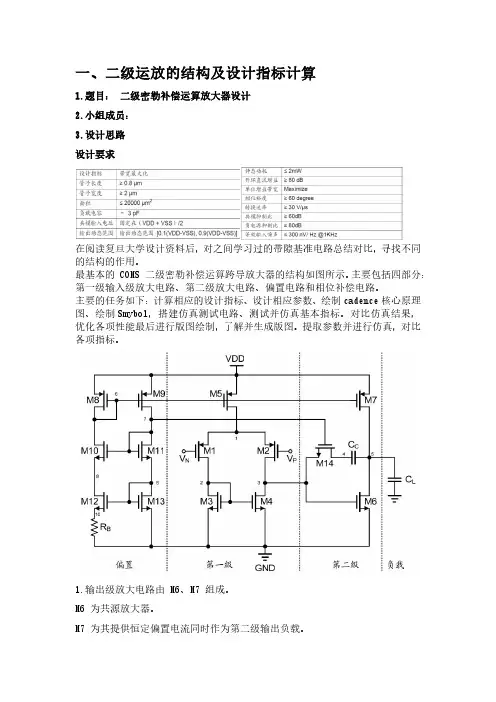

一、二级运放的结构及设计指标计算1.题目:二级密勒补偿运算放大器设计2.小组成员:3.设计思路设计要求在阅读复旦大学设计资料后,对之间学习过的带隙基准电路总结对比,寻找不同的结构的作用。

最基本的COMS二级密勒补偿运算跨导放大器的结构如图所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

主要的任务如下:计算相应的设计指标、设计相应参数、绘制cadence核心原理图、绘制Smybol,搭建仿真测试电路、测试并仿真基本指标。

对比仿真结果,优化各项性能最后进行版图绘制,了解并生成版图。

提取参数并进行仿真,对比各项指标。

1.输出级放大电路由M6、M7组成。

M6为共源放大器。

M7为其提供恒定偏置电流同时作为第二级输出负载。

M14和Cc构成相位补偿电路。

因为M14工作在线性区,通过m14的直流电流为0,所以M14可等效为一个电阻,m14与电容Cc构成RC密勒补偿2.输出级放大电路由M6、M7组成。

M6为共源放大器。

M7为其提供恒定偏置电流同时作为第二级输出负载。

M14和Cc构成相位补偿电路。

因为M14工作在线性区,通过m14的直流电流为0,所以M14可等效为一个电阻,m14与电容Cc构成RC密勒补偿3.偏置电路由M8~M13和RB组成。

M8和M9宽长比相同。

M12与M13相比,源极加入了电阻RB,组成微电流源,产生电流IB。

对称的M11和M12构成共源共栅结构,减小沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

M1和M2为第一级差分输入跨导级,将差分输入电压转换为差分电流;M3和M4为第一级负载,将差模电流恢复为差模电压;M6为第二级跨导级,将差分电压信号转换为电流;M7再将此电流信号转换为电压输出。

4.等效电路图5.静态功耗一旦电源电压确定,静态功耗取决于各支路静态电流总和。

考察各路电路,可以知道,此运放的静态功耗为6.单位增益带宽单位增益带宽是运放最重要的指标之一,它定义为当运放增益为1时,所加输入信号的频率,7.共模抑制比共模抑制比的定义为其中Adm是差模增益,Acm是共模增益。

课程设计报告设计课题: CMOS二级密勒补偿运算放大器的设计姓名: XXX专业: 集成电路设计与集成系统学号: 1115103004 日期 2015年1月17日指导教师: XXX 国立华侨大学信息科学与工程学院一:CMOS二级密勒补偿运算放大器的设计1:电路结构最基本的CMOS二级密勒补偿运算跨导放大器的结构如下图,主要包括四部分:第一级PMOS输入对管差分放大电路,第二级共源放大电路,偏置电路和相位补偿电路。

2:电路描述:输入级放大电路由M1~M5组成。

M1和M2组成PMOS差分输入对管,差分输入与单端输入相比可以有效抑制共模信号干扰;M3和M4为电流镜有源负载;M5为第一级放大电路提供恒定偏置电流。

输出级放大电路由M6和M7组成,M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

偏置电路由M8~M13和Rb组成,这是一个共源共栅电流源,M8和M9宽长比相同。

M12和M13相比,源级加入了电阻Rb,组成微电流源,产生电流Ib。

对称的M11和M12构成共源共栅结构,减少了沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

相位补偿电路由M14和Cc组成,M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3:两级运放主体电路设计由于第一级差分输入对管M1与M2相同,有R1表示第一级输出电阻,其值为则第一级的电压增益对第二级,有第二级的电压增益故总的直流开环电压增益为所以4:偏置电路设计偏置电路由 M8~M13 构成,其中包括两个故意失配的晶体管M12 和M13,电阻RB 串联在M12 的源极,它决定着偏置电流和gm12,所以一般为片外电阻以保证其精确稳定。

为了最大程度的降低M12 的沟道长度调制效应,采用了Cascode 连接的M10以及用与其匹配的二极管连接的M11 来提供M10 的偏置电压。

最后,由匹配的PMOS器件M8 和M9 构成的镜像电流源将电流IB 复制到M11 和M13,同时也为M5 和M7提供偏置。

CMOS二级运算放大器设计编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(CMOS二级运算放大器设计)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为CMOS二级运算放大器设计的全部内容。

CMOS二级运算放大器设计(东南大学集成电路学院)一.运算放大器概述运算放大器是一个能将两个输入电压之差放大并输出的集成电路.运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标1.电路结构最基本的COMS二级密勒补偿运算跨导放大器的结构如图1。

1所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路.图1.1 两级运放电路图2。

电路描述电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。

M6、M7管构成共源放大电路,作为运放的输出级。

M6 提供给 M7 的工作电流.M8~M13组成的偏置电路,提供整个放大器的工作电流。

相位补偿电路由M14和Cc 构成.M14工作在线性区,可等效为一个电阻,与电容Cc 一起跨接在第二级输入输出之间,构成RC 密勒补偿。

3。

设计指标两级运放的相关设计指标如表1。

三.电路设计第一级的电压增益:(3.1) 第二级电压增益:(3.2) 所以直流开环电压增益:(3.3) 单位增益带宽:(3。

二级运算放大电路

二级运算放大电路是一种由两个运算放大器组成的放大电路。

这种电路可以放大输入信号的电压或电流。

在二级运算放大电路中,第一个运算放大器(通常称为输入级或前置级)将输入信号放大,并将放大后的信号传递给第二个运算放大器(通常称为输出级或功率级)。

输出级进一步放大信号,并提供所需的输出电压或电流。

这种电路通常具有很高的增益和很低的输出阻抗。

它可以用作电压跟随器、缓冲器、放大器或缓冲放大器等。

在二级运算放大电路中,输入级和输出级通常采用差分放大器或单端放大器。

差分放大器具有很高的共模抑制比和很高的输入阻抗,因此可以有效地抑制共模干扰并减小失调电压的影响。

输出级通常采用双端放大器或互补输出级。

互补输出级具有很低的输出阻抗和很高的带宽增益积,因此可以提供快速的响应速度和很高的增益带宽。

二级运算放大电路通常需要外接电源和适当的反馈网络来稳定其增益和减小噪声。

在设计和应用中,需要注意一些问题,如电源电压的稳定性、信号源内阻的影响、电路的频率响应等。

套筒式共源共栅二级运算仿真

套筒式共源共栅二级运算放大器是一种常见的电路结构,用于放大直流和交流信号。

它由两级放大器组成,第一级为共源放大器,第二级为共栅放大器。

为了进行仿真,需要使用电路仿真软件,如LTspice、CircuitLab等。

以下是套筒式共源共栅二级运算放大器的仿真步骤:

1. 画出电路图:根据套筒式共源共栅电路结构,使用电路设计软件画出该电路的拓扑结构。

确保包括所有的元件和相互连接。

2. 设置元件参数:根据实际使用的元件类型和规格,设置各个元件的参数,包括电阻、电容、晶体管的大小等。

3. 设置电源:设定电路的供电电压和接地。

4. 添加信号源:为电路添加输入信号源,可以是直流偏置电压和交流信号,也可以是脉冲信号等。

5. 添加被测电路点:添加需要测量的电路节点,以便后续进行电压和电流的测量。

6. 运行仿真:设置仿真参数,如仿真时间、步长等,并运行仿真。

7. 分析仿真结果:仿真完成后,分析仿真结果,包括输入输出电压波形,电流波形,增益等。

通过以上步骤进行仿真可以得到套筒式共源共栅二级运算放大器的电压增益、频率响应、非线性失真等性能参数。

根据仿真结果可以优化电路参数和结构设计,以达到所需的放大性能和稳定性。

目录1前言12二级运算放大器电路 1电路结构 1设计指标 23 Cadence仿真软件 3schematic原理图绘制 3#生成测试电路3电路的仿真与分析4直流仿真 4交流仿真 4版图绘制5差分对版图设计6电流源版图设计 7负载MOS管版图设计 7.DRC & LVS版图验证 8DRC验证 8LVS验证 8 4结论 95参考文献 9摘要本文利用cadence软件简述了二级运算放大器的电路仿真和版图设计。

以传统的二级运算放大器为例,在ADE电路仿真中实现工艺,输入直流电源为5v,直流电流源范围27~50uA,根据电路知识,设置各个MOS管合适的宽长比,调节弥勒电容的大小,进入stectre仿真使运放增益达到40db,截止带宽达到80MHz和相位裕度至少为60。

版图设计要求DRC验证0错误,LVS验证使电路图与提取的版图相匹配,观看输出报告,要求验证比对结果一一对应。

关键词:cadence仿真,设计指标,版图验证。

AbstractIn this paper, the circuit simulation and layout design of two stage operational amplifier are briefly described by using cadence software. In the traditional two stage operational amplifier as an example, the realization of technology in ADE circuit simulation, the input DC power supply 5V DC current source 27~50uA, according to the circuit knowledge, set up each MOS tube suitable ratio of width and length, the size of the capacitor into the regulation of Maitreya, the simulation of stectre amplifier gain reaches 40dB, the cut-off bandwidth reaches 80MHz and the phase margin of at least 60.. The layout design requires DRC to verify 0 errors, and LVS validation makes the circuit map matching the extracted layout, viewing the output report, and requiring verification to verify the comparison results one by one.Key words: cadence simulation, design index, layout verification.1前言近几年来,人们已投入很大力量研究版图设计自动化,计算机辅助设计方法学在给定所需功能行为描述的数字系统设计自动化方面已经非常成功。

两级放大器的设计摘要:两级放大器在实际生活中有着非常重要的作用,它可以把我们生活中需要的信号进行放大来便利人们的生活。

在生活中有着非常广泛的应用。

该设计是两级放大器的设计,首先是对设计方案的选择和设计,详细分析了两级放大器的所需数据,然后在multisim中选择所需的元器件来进行电路的设计。

通过改变电路的电压来进行动态的分析。

仿真结果表明:在电路中输入的电压在第二级放大器的输出端可以准确的看到放大了1000倍,实现了题目的要求。

关键词:两级放大器;电路仿真;设计目录1.设计任务与要求2.方案设计与论证3.单元电路的设计与仿真3.1第一级放大器的设计3.2第二级放大器的3.3桥式整流电源的设计4.总电路设计及其仿真调试过程4.1总体电路的设计4.2仿真结果及其分析5.结论和心得6.参考文献1.设计任务与要求(1)中频带电压的放大增益1000(2)通频带30HZ—30KHZ(3)输出电阻10(4)输入电阻20K(5)负载电阻20K(6)最大不失真输出电压5V(7)用桥式整流电容滤波集成稳压块电路设计所需的正负直流电源2.方案的设计与论证两级放大器的设计具有组装简单,调试方便,工作稳定的实验电路。

设计中包括电源输入电路,一级同相放大电路,二级反相放大电路三部分。

电路原理图如下图2.1所示:图2.1 两级放大器电路原理由设计与要求可以知道,两级放大器设计的实验主要分为三部分,即对于电源输入信号和第一级放大电路,第二级放大电路的设计。

进过分析,电源输入信号电路是桥式整流滤波集成稳压块所设计出来的正负直流电源。

第一级放大电路可以是由同相放大电路的组成,第二级放大电路是由反相放大电路所组成。

由于所需要的电压放大倍数是1000,而同相放大器的电压放大倍数在1—100之间,反相放大器的电压放大倍数在0.1—100之间,因此放大1000倍的设计就可以使用这两个放大器来实现。

因为设计初稿有很多东西都是借鉴书上或者网站上的东西,Multisim 则是第一次接触的仿真软件,因此有的某些电器元件只能够使用Multisim 中所有的。

课程设计报告设计课题: CMOS二级密勒补偿运算放大器的设计姓名: XXX专业: 集成电路设计与集成系统学号: 1115103004 日期 2015年1月17日指导教师: XXX 国立华侨大学信息科学与工程学院一:CMOS二级密勒补偿运算放大器的设计1:电路结构最基本的CMOS二级密勒补偿运算跨导放大器的结构如下图,主要包括四部分:第一级PMOS输入对管差分放大电路,第二级共源放大电路,偏置电路和相位补偿电路。

2:电路描述:输入级放大电路由M1~M5组成。

M1和M2组成PMOS差分输入对管,差分输入与单端输入相比可以有效抑制共模信号干扰;M3和M4为电流镜有源负载;M5为第一级放大电路提供恒定偏置电流。

输出级放大电路由M6和M7组成,M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

偏置电路由M8~M13和Rb组成,这是一个共源共栅电流源,M8和M9宽长比相同。

M12和M13相比,源级加入了电阻Rb,组成微电流源,产生电流Ib。

对称的M11和M12构成共源共栅结构,减少了沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

相位补偿电路由M14和Cc组成,M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3:两级运放主体电路设计由于第一级差分输入对管M1与M2相同,有R1表示第一级输出电阻,其值为则第一级的电压增益对第二级,有第二级的电压增益故总的直流开环电压增益为所以4:偏置电路设计偏置电路由 M8~M13 构成,其中包括两个故意失配的晶体管M12 和M13,电阻RB 串联在M12 的源极,它决定着偏置电流和gm12,所以一般为片外电阻以保证其精确稳定。

为了最大程度的降低M12 的沟道长度调制效应,采用了Cascode 连接的M10以及用与其匹配的二极管连接的M11 来提供M10 的偏置电压。

最后,由匹配的PMOS器件M8 和M9 构成的镜像电流源将电流IB 复制到M11 和M13,同时也为M5 和M7提供偏置。

哈尔滨理工大学软件学院模拟IC课程设计报告课程模拟IC设计题目二级运算放大器专业集成电路设计与集成班级集成10-2班学生唐贝贝学号1014020227指导老师陆学斌2013年6月14日目录1.课程设计目的…………………………………………………2.课程设计题目描述和要求……………………………………3.课程设计具体内容……………………………………………3.1 设计过程分析……………………………………………3.2使用软件…………………………………………………3.3 原理图……………………………………………………3.4 仿真网表…………………………………………………3.5波形分析…………………………………………………4.心得体会………………………………………………………一、课程设计目的1.熟悉并掌握Hspice与cosmosScope软件的使用。

2.熟练应用Hspice仿真网表并修改分析网表,学会用comosScope查看分析波形。

3.锻炼学生独立完成二级运算放大器的能力。

4. 在扎实的基础上强化实践能力,把模拟IC理论实践化。

二、课程设计题目描述和要求设计指标:静态功耗:小于5mw开环增益:大于70dB单位增益带宽大于5MHz相位裕量:大于60度转换速率(SR)大于20V/us共模抑制比:大于60dB电源抑制比:大于70dB输入失调:小于1mV负载电容:2-4pF要求:1、手工计算出每个晶体管的宽长比。

通过仿真验证设计是否正确,保证每个晶体管的正常工作状态。

2、使用Hspice工具得到电路相关参数仿真结果,包括:幅频和相频特性(低频增益,相位裕度,单位增益带宽)、CMRR、PSRR、共模输入输出范围、SR等。

3、每个学生应该独立完成电路设计,设计指标比较开放,如果出现雷同按不及格处理。

4、完成课程设计报告的同时需要提交仿真文件,包括所有仿真电路的网表,仿真结果。

5、相关问题参考教材第六章,仿真问题请查看HSPICE手册。

两级全差动运算放大器的设计班级:自动化0905姓名:余陆洋学号:U200914361同组人姓名:刘洁、戴伟、王睿祺题目要求根据性能指标的要求,选择合适的放大器类型,采用0.18um CMOS 工艺,设计一个两级运算放大器性能指标如下:电源电压: 1.8V 第一级增益: ≥20dB 第一级GBW: ≥500MHz 两级增益: ≥80dB 相位裕度: ≥60º差分压摆率: ≥200V/us等效输入参考噪声:200nV/Hz @1MHz 负载电容: ≤1pF静态功耗: 尽可能小,不做具体要求人员分工余路洋:运放整体仿真 刘洁:网表的编写戴伟:第一级运放与第二级运放的仿真 王睿祺:电路参数的设计整体设计1) 基本参数设定mV V V TH G S 200=- V V TN 5.0=V V TP 4.0-= 4106.4-⨯=ox n C u4103.2-⨯=ox p C u2) 基本公式Lmip c g GBW π2=tn ds Dm v v I g -=2 2)(21TH GS ox D V V L WuC I -=3) 第一级运放设计:inn由题目可知,要满足设计要求最主要的是确定MOS 管的宽长比以及偏置电流。

我们取负载电容为L c =0.4Pf ,由此可确定ID 的大小,又由于mV V V TH G S 200=-所以由图可知,增益:30db,GBW>500W.4) 第二级运放设计增益>50db5)整体设计a)增益>80dbb)由下图可以看出相位裕度>60o,满足要求差分压摆率>0.4v/2ns=200V/us,所以满足要求c)等效输入参考噪声在1MHz时<200nV/Hz.d)静态功耗:网表程序*two_stage_amp.option post=2 numdgt=7 tnom=27.lib 'C:\rf018.l' tt.global VDD! GND!.PARAM************************************************************************ * Library Name: Mixer_Down* Cell Name: amp_stage_two* View Name: schematic************************************************************************.SUBCKT amp_stage_two Iref2 Vb2 Vb3 Vb4 Vcm Vin Vip Voutn Voutp*.PININFO Iref2:I Vb2:I Vb3:I Vb4:I Vcm:I Vin:I Vip:I Voutn:O Voutp:OMM7 net087 Vb2 vdd! vdd! pch l=300n w=805n m=1MM6 Voutp Vb3 net087 vdd! pch l=300n w=5.39u m=1MM5 net33 Vb2 vdd! vdd! pch l=300n w=805n m=1MM4 Voutn Vb3 net33 vdd! pch l=300n w=5.39u m=1MM12 net33 Vip net30 gnd! nch l=300n w=2u m=1MM13 net087 Vin net30 gnd! nch l=300n w=2u m=1MM11 Iref2 Iref2 gnd! gnd! nch l=280.0n w=2u m=1MM10 net30 Iref2 gnd! gnd! nch l=280.0n w=3u m=1MM3 Voutp Vb4 net42 gnd! nch l=400n w=805n m=1MM2 net42 Vcm gnd! gnd! nch l=1u w=405n m=1MM1 Voutn Vb4 net46 gnd! nch l=400n w=805n m=1MM0 net46 Vcm gnd! gnd! nch l=1u w=405n m=1.ENDS************************************************************************ * Library Name: Mixer_Down* Cell Name: amp_stage_one* View Name: schematic************************************************************************.SUBCKT amp_stage_one Iref1 Vcm Vin Vip Voutn Voutp*.PININFO Iref1:I Vcm:I Vin:I Vip:I Voutn:O Voutp:OMM5 Iref1 Iref1 vdd! vdd! pch l=1u w=105.0000u m=1MM4 net23 Iref1 vdd! vdd! pch l=1u w=900.0000u m=1MM3 Voutp Vin net23 vdd! pch l=180.0n w=705.0000u m=1MM2 Voutn Vip net23 vdd! pch l=180.0n w=705.0000u m=1MM1 Voutn Vcm gnd! gnd! nch l=180.0n w=5.645u m=1MM0 Voutp Vcm gnd! gnd! nch l=180.0n w=5.645u m=1.ENDS************************************************************************ * Library Name: Mixer_Down* Cell Name: two_stage_amp* View Name: schematic************************************************************************ *.PININFO Vb2:I Vb3:I Vb4:I Vcm:I Vin:I Vip:I Voutn:O Voutp:OCC2 Voutp gnd! 1.0000p $[CP]CC5 net048 Voutp 20f $[CP]CC3 Voutn gnd! 1.0000p $[CP]CC4 net049 Voutn 20f $[CP]XI22 net044 Vb2 Vb3 Vb4 Vcm Vin Vip net049 net048 / amp_stage_two *.SUBCKT amp_stage_two Iref2 Vb2 Vb3 Vb4 Vcm Vin Vip Voutn VoutpXI21 net076 Vcm net049 net048 Voutn Voutp / amp_stage_one*.SUBCKT amp_stage_one Iref1 Vcm Vin Vip Voutn Voutp*.SUBCKT two_stage_amp Vb2 Vb3 Vb4 Vcm Vin Vip Voutn VoutpVVin Vin 0 DC 0.9 AC 1.0VVip Vip 0 DC 0.9 AC 1.0 180VVb2 Vb2 0 0.8VVb3 Vb3 0 0.5VVb4 Vb4 0 1.3VVcm Vcm 0 0.9VVdd vdd! gnd! 1.8Iref1 net076 0 180uIref2 vdd! net044 10u*VVin Vin 0 0 PULSE 0 1.0 0.1N .1N .1N 100N 100N*RVip Vip 0 1k*.TRAN 0.1N 100N*.PRINT TRAN V(Vin) V(Voutn).AC DEC 10 1 3G.PRINT AC VDB(Voutp) VP(Voutp).noise V(Voutp) VVip 10.END。

设计二级跨导放大器

要求Ad>80dB,电源电压2.7倍,GB〉5M,Cl=10pF,SR>10V/us,输出电压摆幅>2V,ICMR:1~2V,CMRR>70dB

1.新建工程,绘制电路图

2.因为Cc>0.22Cl,且Cl=10pF

所以取Cc=3pF

所以IdN3>=SR*Cc=25uA,我们取30uA

3.因为ICMR:1~2V

所以Vin=(1V+2V)/2=1.5V

扫描Vth与Vbs的关系,结果为

所以VdsatN3=0.6628mV

4. 设VA=0.6628V,扫描MN3的宽长比,使IdN3=30uA,扫描结果为

所以w=23.95u

5.设定MP1的VonP1=0.2V,Vcc=3V,所以MP1的Vg=Vcc-(Von+VthP1)=3V-(0.2V+0.67V)=2.13V。

扫描MP1的宽长比,使IdP1=30uA/2=15uA,扫描结果为

所以W=22.08u

7. MN1的s端设定为VA=0.6228V,扫描MN1的宽长比,使d端的电压为开始设定的2.13V,扫描结果为

所以W=10.95u

8.因为Itot<1/2.7=370uA,所以IdN4<370uA-30uA=340uA

又因为gmP3>10gmN2,查表可知,gm/IdN≈14.5,gm/IdP≈12,所以IdP3〉10*14.5*15uA/12=181.25uA,所以选择IdP3=200uA。

因为输出摆幅>2,最大输出电压3-0.2V=2.8V和最小输出电压0.2V满足条

件,所以设静态输出电压为(2.8V+0.2V)/2=1.5V扫描MN4的宽长比,使IdP3=200uA,扫描结果为

此时W=134.38u

9.扫描MP3的宽长比使输出电压为1.5V,扫描结果为

此时W=224.25u

10.各偏置和宽长比设置完后,进行Bias Point,结果为

符合要求

11.进行AC sweep扫描电路的放大倍数,结果为

Ad=77.618dB<80dB,不符合条件,需要进行修改

12.因为Ad=gm*r0,所以尝试使MN4、MP3的L=2u,查表得此时的gm/IdP=10.3 所以IdP3>10*14.5*15uA/10.3=211.165uA,又因为IdN4<340uA

所以取IdP3=250uA

静态输出电压不变,扫描MN4、MP3的宽长比,得到的结果为

MN4的宽w=233.65u

MP3的宽w=463.55u

Bias Point 的结果为

符合要求

13.进行AC sweep扫描电路的放大倍数,结果为

Ad=80.023dB 刚好达到要求

同时扫描放大倍数和相位图,结果为

GB=9.3935M满足条件,PM=53.485不满足条件PM>60 所以修改Cl=4pF,此时Bias Point 仿真结果为

AC sweep仿真结果为

Ad=80.023dB,GB=7.4989M,PM=61.5满足条件14.将输入电压变为共模输入电压

进行AC Sweep 扫描结果为

所以Ac=-5.147dB

所以CMRR=Ad/Ac=80.023dB-(-5.147dB)=85.17dB 15.改变输入电压

进行DC Sweep,扫描输出电压摆幅,结果为

输出摆幅大于2V。