EDA第六章作业-中国地质大学

- 格式:docx

- 大小:231.37 KB

- 文档页数:4

作业3-6module Mux3_1(a1,a2,a3,s0,s1,outy); input a1,a2,a3,s0,s1;output outy;reg outy;reg temp;always @(a2,a3,s0)beginif(s0 == 1'b0)temp = a2;elsetemp = a3;endalways @(a1, temp,s1)beginif(s1 == 1'b0)outy = a1;elseouty = temp;endendmodule作业3-7 半减器module H_suber(x,y,diff,s_out);input x,y;output diff,s_out;reg s_out;wire diff;assign diff = x ^ y;always @(x,y)beginif(x < y)s_out = 1'b1;elses_out = 1'b0;endendmodule全减器module F_suber(x,y,sub_in,diffr,sub_out); input x,y,sub_in;output diffr,sub_out;wire diffr,sub_out;wire H_diff,H_sout,s_out;assign sub_out = s_out || H_sout;H_suber U1 (.x(x),.y(y),.diff(H_diff),.s_out(H_sout));H_suber U2 (.x(H_diff),.y(sub_in),.diff(diffr),.s_out(s_out));Endmodule8位全减器module Bit8_suber(X,Y,Sub_in,Diff,Sub_out);input[7:0] X,Y;input Sub_in;output[7:0] Diff;output Sub_out;wire[7:0] Diff;wire Sub_out;wire[6:0] sub_out;F_suber U1(.x(X[0]),.y(Y[0]),.sub_in(Sub_in),.diffr(Diff[0]),.sub_out(sub_out[0]));F_suber U2(.x(X[1]),.y(Y[1]),.sub_in(sub_out[0]),.diffr(Diff[1]),.sub_out(sub_out[1])); F_suber U3(.x(X[2]),.y(Y[2]),.sub_in(sub_out[1]),.diffr(Diff[2]),.sub_out(sub_out[2])); F_suber U4(.x(X[3]),.y(Y[3]),.sub_in(sub_out[2]),.diffr(Diff[3]),.sub_out(sub_out[3])); F_suber U5(.x(X[4]),.y(Y[4]),.sub_in(sub_out[3]),.diffr(Diff[4]),.sub_out(sub_out[4])); F_suber U6(.x(X[5]),.y(Y[5]),.sub_in(sub_out[4]),.diffr(Diff[5]),.sub_out(sub_out[5])); F_suber U7(.x(X[6]),.y(Y[6]),.sub_in(sub_out[5]),.diffr(Diff[6]),.sub_out(sub_out[6])); F_suber U8(.x(X[7]),.y(Y[7]),.sub_in(sub_out[6]),.diffr(Diff[7]),.sub_out(Sub_out)); Endmodule作业3-13Amodule DFF_A(D,EN,CLK,RST,Q,Q1);input D,EN,CLK,RST;output Q,Q1;reg Q;wire Q1;wire D_temp;assign D_temp = D && EN;assign Q1 = (~D_temp)||RST;always @(negedge RST or posedge CLK)beginif(!RST)Q <= 1'b0;elseif(EN)Q <= D;elseQ <= Q;endmoduleBmodule DFF_B (A,B,C,D,Y);input A,B,C,D;output Y;reg Y;wire temp1,temp2,temp3;assign temp1 = A || B;assign temp2 = C && D;assign temp3 = temp1 ^ temp2; always @(A,temp1,temp3)beginif(temp1)Y = temp3;elseY = A;endendmoduleCmodule DFF_C(RST,D,CLK,Q,DOUT); input RST,D,CLK;output Q,DOUT;reg Q,DOUT;reg D_temp1;wire D_temp2;assign D_temp2 = D ^ D_temp1; always @(RST,D)beginif(RST)D_temp1 = 1'b0;elseD_temp1 = D;endalways @(posedge CLK)beginQ <= D_temp1;DOUT <= D_temp2;endmoduleDmodule DFF_D(SET,D,CLK,EN,RESET,Q);input SET,D,CLK,EN,RESET;output Q;reg Q;wire SET_temp;assign SET_temp = (~RESET) && SET;always @(posedge CLK or posedge RESET or posedge SET_temp) beginif(RESET)Q <= 1'b0;elseif(SET_temp)Q <= 1'b1;elseif(EN)Q <= D;elseQ <= Q;endendmodule8-2.用Mealy机类型,写出控制ADC0809采样的状态机。

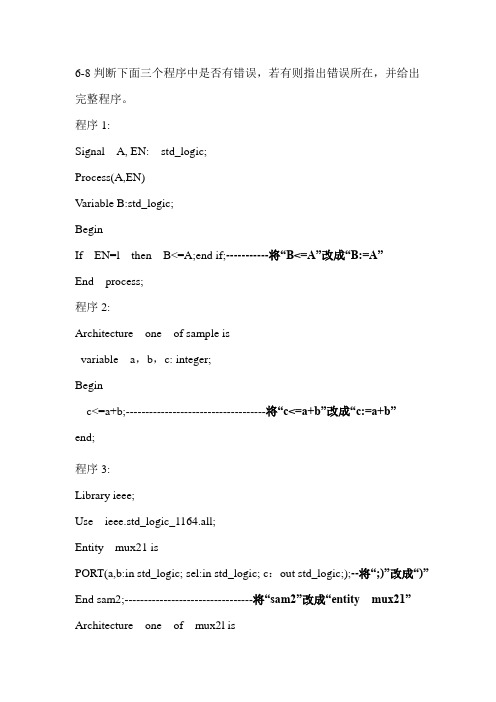

6-8判断下面三个程序中是否有错误,若有则指出错误所在,并给出完整程序。

程序1:Signal A, EN: std_logic;Process(A,EN)Variable B:std_logic;BeginIf EN=l then B<=A;end if;-----------将“B<=A”改成“B:=A”End process;程序2:Architecture one of sample isvariable a,b,c: integer;Beginc<=a+b;------------------------------------将“c<=a+b”改成“c:=a+b”end;程序3:Library ieee;Use ieee.std_logic_1164.all;Entity mux21 isPORT(a,b:in std_logic; sel:in std_logic; c:out std_logic;);--将“;)”改成“)”End sam2;---------------------------------将“sam2”改成“e ntity mux21”Architecture one of mux2l isbegin--增加“process(a,b,sel)begin”If sel='0' then c:=a; else c:=b;end if;---------应改成“if sel='0'then c<=a;else c<=b;end if;”---------增加“end process;”End two;---------------将“two”改成“architecture one6-9根据例4-23设计8位左移移位寄存器,给出时序仿真波形。

library ieee;use ieee.std_logic_1164.all;entity shfrt isport(clk,load: in std_logic;din:in std_logic_vector (7 downto 0);qb: out std_logic);end shfrt;architecture behav of shfrt isbeginprocess (clk,load)variable reg8 :std_logic_vector (7 downto 0);beginif clk'event and clk='1' thenif load ='1' then reg8 :=din;else reg8 (7 downto 1) :=reg8 (6 downto 0);end if;end if;qb <= reg8(7);end process;end architecture behav;RTL时序仿真。

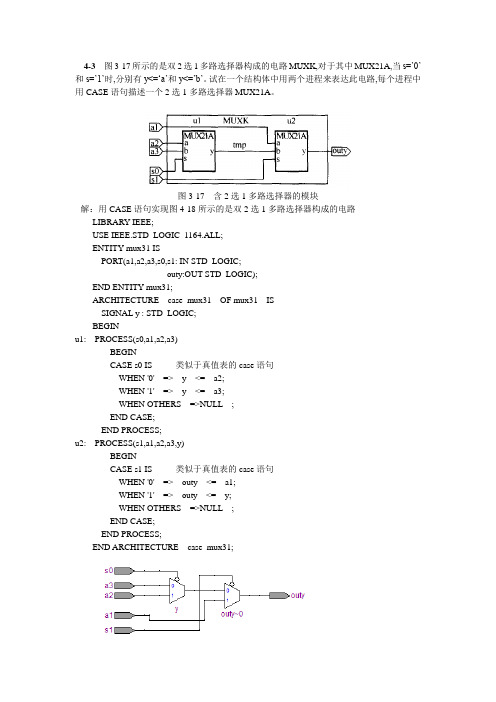

4-3 图3-17所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s=’0’和s=’1’时,分别有y<=‘a’和y<=’b’。

试在一个结构体中用两个进程来表达此电路,每个进程中用CASE语句描述一个2选1多路选择器MUX21A。

图3-17 含2选1多路选择器的模块--解:用CASE语句实现图4-18所示的是双2选1多路选择器构成的电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux31 ISPORT(a1,a2,a3,s0,s1: IN STD_LOGIC;outy:OUT STD_LOGIC);END ENTITY mux31;ARCHITECTURE case_mux31 OF mux31 ISSIGNAL y : STD_LOGIC;BEGINu1: PROCESS(s0,a1,a2,a3)BEGINCASE s0 IS --类似于真值表的case语句WHEN '0' => y <= a2;WHEN '1' => y <= a3;WHEN OTHERS =>NULL ;END CASE;END PROCESS;u2: PROCESS(s1,a1,a2,a3,y)BEGINCASE s1 IS --类似于真值表的case语句WHEN '0' => outy <= a1;WHEN '1' => outy <= y;WHEN OTHERS =>NULL ;END CASE;END PROCESS;END ARCHITECTURE case_mux31;3-6 图3-18是一个含有上升沿触发的D 触发器的时序电路(sxdl),试写出此电路的VHDL设计文件。

图3-18 时序电路--解:实现图4-19电路的VHDL 程序t4_19.vhd LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY t4_19 ISPORT (CL,CLK0: IN STD_LOGIC; OUT1: OUT STD_LOGIC); END ENTITY t4_19;ARCHITECTURE sxdl OF t4_19 IS ----时序电路sxdl SIGNAL Q : STD_LOGIC; BEGINPROCESS(CLK0) BEGINIF CLK0'EVENT AND CLK0='1' THEN --检测时钟上升沿 Q <= NOT(Q OR CL); END IF;OUT1 <= NOT Q; END PROCESS;END ARCHITECTUREsxdl;3-7 给出1位全减器的VHDL 描述;最终实现8位全减器。

5-14library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity div is port(clk,RESET: in std_logic;outl,out2:out std_logic);end div;architecture div_16 of div issignal ent: std_logic_vector(3 downto 0);beginprocess(clk)beginif reset=T thencnt<=u OOOO n;elsif (clk'event and clk=T) then cnt<=cnt+T;end if;end process;outl<=T when cnt=15 else 'O';--不等out2<=cnt(3); -正负脉宽相等end div_16;5-11library ieee;use ieee.std_logic_l 164.all;entity s_machine is port(clk:in std_logic;din:in std_logic_vector( 1 downto 0); dout:out std_logic_vector( 1 downto 0));end s_machine;architecture a of s_machine istype state is (s0,sl,s2);signal current_state,next_state:state;beginprocess(din,curret_state) -次态译码器与输出译码器描述begincase current_state iswhen sO =>讦(din = "00") then next_state <= sO; doutv="00'';elsif (din = "01") then next_state <= s2; dout<=,,10,?;elsif (din = TO") then next_state <= s2; dout<=,,lF,;end if;when si =>if (din = “00") then next_state <= si; doutv="00''; elsif(din = "01") then next_state <= sO; doutv=''00"; elsif(din = TO") then next_state <= s2; dout<=,,10,?; end if;when s2 =>讦(din = "00") then next_state <= s2; doutv="00''; elsif(din = "01") then next_state <= si; doutv="00''; elsif(din = TO") then next_state <= sO; doutv=''00"; end if;end case;End process;process(clk) -状态寄存器描述beginif (clk?event and clk== '1') then current_state<=next_state;end if;End process;End a;5-10(1)entity h_sub isport (x, y: in BIT ;diff, sub_out: out bit);end h_sub; Architecture A of h_sub isbegindiff <= x xor y; sub_out <= not X and Y;end A;ENTITY F_SUB ISPORT(X, Y, SUB_IN: IN BIT;DIFF, SUB_OUT: OUT BIT);ENDF_SUB;ARCHITECTURE ART OF F_SUB ISCOMPONENT H_SUBPORT(X, Y: IN BIT;DIFF, SUB_OUT: OUT BIT);END COMPONENT;SIGNAL SI, S2, S3: BIT;BEGINUl: H_SUB PORT MAP (X=>X, Y=>Y, DIFF=>S1, SUB_OUT=>S2);U2 : H_SUB PORT MAP (X=>S1 , Y=>SUB_IN ,DIFF=>DIFF, SUB_OUT=>S3);SUB_OUT<=S2 OR S3;END ARCHITECTURE ART;⑵.entity f^sub isport ( x, y, sub_in: in bit;diff, sub_out: out bit);end f_sub;architecture func of 匚sub isbeginprocess(x, y, sub_in)variable con: bit_vector(l downto 0);variable com: bit_vector(2 downto 0);begincom:= x & y & sub_in;if (com = “000") then con := “00";elsif (com = "Oil") then con := "01";elsif (com 二"100") then con :二"10";elsif (com 二"101") then con := "00";elsif (com = T10") then con := “00";else con := T1";end if;diff <= con(l); sub_out <= con(0);end process;end func;⑶entity subtracter isport ( a, b : in bit_vector(7 dowto 0);sub_in : in bit;diff: out bit_vector(7 dowto 0); sub_out: out bit); end subtracter;architecture stru of subtracter iscomponent H_subport ( x, y, sub_in: in bit; diff, sub_out: out bit);end component; signal sub: bit_vector(8 downto 0); begingO: for I in 0 to 7 generateu_inst: H_subbport map(a(i), b(i),sub(i),diff(i), sub(i+l));end generate;sub(0) <= sub_in;sub_out <=sub(8);end stru;5-8library IEEE:use IEEE. Std _logic_ 1164.all:use IEEE. STD_LOGIC _UNSIGNED.all:entity seq_gen isport(CIK, RESET: in STD_LOGIC:Y0: out STD_LOGIC_vector(9 downto 0)):End seq_gen;Architecture rtl of seq_gen isSignal CNT: STD_LOGIC_VECTOR(3 downto 0);beginprocess(CLK, RESET)begin〜 ifRESET=,l,thenCNT v=''0000";Elsif CLK'event and CLK=T thenIfcnt="1001''thenCNTv=”000";elseCNT<=CNT +T;End if;End if;End process ;With CNT SelectY0<=,,000000000F, when ” 0000”,“0000000010” when " 0001”,“0000000100” when ” 0010”,“0000001000” when ” 0011”,“0000010000” when ” 0100”,^^0000100000^^ when ” 0101”,“0001000000” when ” 0110”,“0010000000” when ” 0111”,4<010*******,? when ” 1000”,T 000000000’' when others ;end rtl;5-7library IEEE;use IEEE.Std _logic_ 1164.all;use IEEE.std_logic_unsigned.al 1; entity counter isport(clk,rst,ml,m0:in std_logic;y:out std_logic_vector (4 downto 0));End counter;Architecture rtl of counter isSignal sei: std_logic_vector (1 downto 0);Signal per,ent: std_logic_vector (4 downto 0);beginsel<=ml&mO;With sei Selectperv=”1001(F when “0(F,"OOOll" when “01",,,0100r, when TO","00101" when others;process(reset,clk)beginif reset=T thencnt<=n00000n;elsif (clk'event and clk=r)thenif ent = pre thencnt<=H00000u;elsecnt<=cnt+T;end if;end if;end process;y<=cnt;end rtl;2-1判断下列标示符是否合法,如果有误指出原因:16#OFA#, 10#12F#, 8#7989#, 8#356#, 2#0101010#, 74HC245,\74HC574\, CLR/RESET, \IN, 4/SCLKX, DI00% 16#OFA#10#12F# 8#7989# 8#356# 2#0101010# 以上不合法,不能以数字开头和存在#符号。

中国地质大学(北京)本科课程报告《虚拟仪器技术》学生姓名衡星院(系)地球物理与信息技术学院专业测控技术与仪器学号10101522132017年10月19日中国地质大学(北京)目录第一章绪论 (1)1.1概述 (1)1.2设计要求 (1)1.2.1下位机端-利用虚拟串口软件来模拟发送一串数据 (1)1.2.2上位机端—LabVIEW程序 (1)1.2.3读取文件 (2)第二章设计思路及步骤 (3)2.1上位机-下位机的串口匹配 (3)2.2整体框架设计 (4)2.3存取文件方面 (4)2.3.1VISA串口设计 (5)2.3.2存取数据显示设计 (5)2.3.3报警设计 (6)2.3.4存取文件设计 (7)2.4读取文件方面 (8)2.4.1读取文件设计 (8)2.4.2读取数据显示设计 (8)第三章调试及运行结果 (9)3.1调试步骤 (9)3.1.1调试准备工作 (9)3.1.2存取文件步骤 (11)3.1.3读取文件步骤 (11)3.2运行结果 (11)3.2.1全部缓存区运行结果 (11)3.2.2存取文件运行结果 (12)3.2.3读取文件运行结果 (13)第四章结论与展望 (14)4.1总结 (14)4.1.1性能分析总结 (14)4.1.2尚存在的问题 (14)4.2展望 (14)致谢 (15)参考文献 (16)第一章绪论1.1概述所谓虚拟仪器(Virtual Instrument,简称VI),即是将现有的计算机主流技术与革新的灵活易用的软件和高性能模块化硬件结合在一起,建立起功能强大又灵活易变的基于计算机的测试测量与控制系统。

虚拟仪器是计算机技术和仪器技术深层次结合的产物,是计算机辅助测试(CAT)领域的一项重要技术,是计算机硬件资源、仪器与测控系统硬件资源和虚拟仪器软件资源三者有效的结合。

本课题目的在于熟悉LabVIEW开发环境,掌握基于LabVIEW的虚拟仪器原理、设计方法和实现技巧,运用专业课程中的基本理论和实践知识,采用LabVIEW开发工具,实现《虚拟仪器技术》课程作业要求。

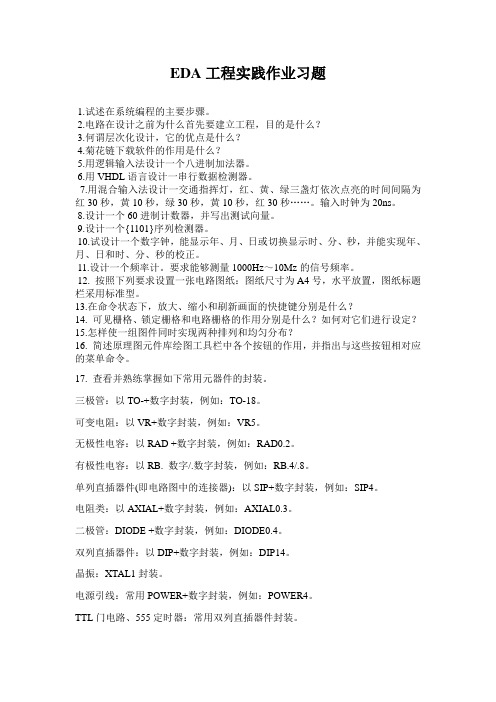

EDA工程实践作业习题1.试述在系统编程的主要步骤。

2.电路在设计之前为什么首先要建立工程,目的是什么?3.何谓层次化设计,它的优点是什么?4.菊花链下载软件的作用是什么?5.用逻辑输入法设计一个八进制加法器。

6.用VHDL语言设计一串行数据检测器。

7.用混合输入法设计一交通指挥灯,红、黄、绿三盏灯依次点亮的时间间隔为红30秒,黄10秒,绿30秒,黄10秒,红30秒……。

输入时钟为20ns。

8.设计一个60进制计数器,并写出测试向量。

9.设计一个{1101}序列检测器。

10.试设计一个数字钟,能显示年、月、日或切换显示时、分、秒,并能实现年、月、日和时、分、秒的校正。

11.设计一个频率计。

要求能够测量1000Hz~10Mz的信号频率。

12. 按照下列要求设置一张电路图纸:图纸尺寸为A4号,水平放置,图纸标题栏采用标准型。

13.在命令状态下,放大、缩小和刷新画面的快捷键分别是什么?14. 可见栅格、锁定栅格和电路栅格的作用分别是什么?如何对它们进行设定?15.怎样使一组图件同时实现两种排列和均匀分布?16. 简述原理图元件库绘图工具栏中各个按钮的作用,并指出与这些按钮相对应的菜单命令。

17. 查看并熟练掌握如下常用元器件的封装。

三极管:以TO-+数字封装,例如:TO-18。

可变电阻:以VR+数字封装,例如:VR5。

无极性电容:以RAD +数字封装,例如:RAD0.2。

有极性电容:以RB. 数字/.数字封装,例如:RB.4/.8。

单列直插器件(即电路图中的连接器):以SIP+数字封装,例如:SIP4。

电阻类:以AXIAL+数字封装,例如:AXIAL0.3。

二极管:DIODE +数字封装,例如:DIODE0.4。

双列直插器件:以DIP+数字封装,例如:DIP14。

晶振:XTAL1封装。

电源引线:常用POWER+数字封装,例如:POWER4。

TTL门电路、555定时器:常用双列直插器件封装。

无极性电容:以RAD +数字表示有极性电容:以RB.2/.4等等表示单列直插器件(即电路图中的连接器):以SIP +数字表示电阻类:以AXIAL +数字表示二极管:DIODE +数字表示双列直插器件:以DIP +数字晶振:XTAL1电源引线常用POWER+数字表示TTL门电路、555定时器,常用双列直插器件封装存储器实验与实践1、FPGA中LPM_ROM配置与读出实验一.实验目的1、掌握FPGA中lpm_ROM的设置,作为只读存储器ROM的工作特性和配置方法。

第一章 EDA概述一、填空题1.2000年推出的Pentium 4微处理器芯片的集成度达——万只晶体管。

2.一般把EDA技术的发展分为——、——和——三个阶段。

3.在EDA发展的——阶段,人们只能借助计算机对电路进行模拟、预测,以及辅助进行集成电路版图编辑、印刷电路板(PcB)布局布线等工作。

4.在EDA发展的——阶段,人们可以将计算机作为单点设计工具,并建立各种单元库,开始用计算机将许多单点工具集成在一起使用。

5.EDA设计流程包括——、——、——和——四个步骤。

6.EDA的设计验证包括——、——和——三个过程。

7.EDA的设计输入主要包括——、——和———。

8.文本输入是指采用——进行电路设计的方式。

9.功能仿真是在设计输入完成之后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为——。

10.时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为——或——。

11.当前最流行的并成为1EEE标准的硬件描述语言包括————和——。

12.采用PLD进行的数字系统设计,是基于芯片的设计或称之为——的设计。

13.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为——的设计法。

14.EDA工具大致可以分为——、——、———、———和——等五个模块。

15.将硬件描述语吉转化为硬件电路的重要工具软件称为——————。

二、单项选择题1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( )。

①设计输入②设计输出③仿真④综合2.一般把EDA技术的发展分为( )几个阶段。

①2 ②3 ③4 ④53.AHDL属于( )描述语言。

①普通硬件②行为③高级④低级4.vHDL属于( )描述语言。

①普通硬件②行为③高级④低级5.包括设计编译和检查、逻辑优化和综合、适配和分割、布局和布线,生成编程数据文件等操作的过程称为( )。

数字系统设计与EDA技术课后练习题含答案一、十进制和二进制数转换练习题1:将十进制数87转换为二进制数。

答案1:87的二进制表示为1010111。

练习题2:将二进制数1110101转换为十进制数。

答案2:1110101的十进制表示为117。

练习题3:将十进制数170转换为八进制数。

答案3:170的八进制表示为252。

练习题4:将八进制数243转换为十进制数。

答案4:243的十进制表示为163。

练习题5:将十进制数189转换为十六进制数。

答案5:189的十六进制表示为0xBD。

练习题6:将十六进制数0x3F转换为十进制数。

答案6:0x3F的十进制表示为63。

二、布尔代数和逻辑门电路练习题1:使用逻辑门实现以下布尔代数:Y = (A and B and C) or D答案1:这个布尔代数可以用以下逻辑门实现: +----+A -------| ||AND +--------+B -------| | |+----+ +----v----+C --------------| || OR +----- YD --------------| |+----------+练习题2:设计一个电子逻辑门电路,将两个单字节二进制数相加。

输入是两个二进制数,输出是相加的结果。

假设不会有溢出。

答案2:这个电子逻辑门电路可以用以下连线和逻辑门实现:输入1 --> +-----+--> | |+-----+| | | ADD +--> C3 --------+ +-----+--> || |输入2 --> +-----+--> | | | | | | | ADD |+-----+--> C2 --------+-->| |--> | +--+--+| | ||| | ||+-----+--> ||||||+-----+--> C1 --------+--> 输出其中ADD代表一个加法器电路,C1-C3代表进位。

1、FPGA与CPLD的区别?(1)结构不同:CPLD 复杂可编程逻辑器件,CPLD 器件至少包括以下 3 个部分:可编程逻辑功能块(FB) ;可编程I/ O 单元;可编程内部连线。

在结构上以乘积项结构方式构成逻辑行为。

FPGA 现场可编程门阵列,通常包含三类可编程资源:可编程逻辑功能块、可编程I/O块和可编程互连资源。

在结构上以查表法结构方式构成逻辑行为。

(2)功能不同①CPLD更适合完成各种算法和组合逻辑,FP GA更适合于完成时序逻辑。

换句话说,FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限乘积项丰富的结构。

②CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性。

③在编程上FPGA比CPLD具有更大的灵活性。

CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FP GA 可在逻辑门下编程,而CPLD是在逻辑块下编程。

④FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。

⑤CPLD比FPGA使用起来更方便。

CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单。

而FPGA的编程信息需存放在外部存储器上,使用方法复杂。

⑥CPLD的速度比FPGA快,并且具有较大的时间可预测性。

这是由于FPGA 是门级编程,并且CLB之间采用分布式互联,而CPLD是逻辑块级编程,并且其逻辑块之间的互联是集总式的。

⑦CPLD保密性好,FPGA保密性差。

⑧一般情况下,CPLD的功耗要比FPGA大2、第八章课后习题8-15方法一:LIBRARY ieee;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;Entity method1 isPort(a,b: in std_logic_vector(7 downto 0);d,e,f: out std_logic);End entity;ARCHITECTURE arth1 OF method1 ISBegind<=‘1’ when a=b else ‘0’;e<=‘1’ when a>b else ‘0’;f<=‘1’ when a<b else ‘0’;end architecture arth1;方法二:LIBRARY ieee;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;Entity method2 isPort(a,b: in std_logic_vector(7 downto 0);d,e,f: out std_logic);End entity;ARCHITECTURE arth2 OF method2 ISSignal tmp: std_logic_vector(8 downto 0);Signal t: std_logic;BeginTmp<=('0’&a)-(’0’& b);T<=‘1’ when tmp=”000000000” else‘0’;D<=t;E<=(not tmp(8)) and (not t);F<=tmp(8) and (not t);End architecture arth2;3、第七章习题7-7next1 <= "1101" when a= '0' AND b='1' elsed when a='0' elsec when b='1' else"1011";4、第三章3-5LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MULTI ISPORT(CL:IN STD_LOGIC; --输入选择信号CLK0:IN STD_LOGIC; --输入信号OUT1:OUT STD_LOGIC);--输出端END ENTITY;SIGNAL Q : STD_LOGIC;SIGNAL Q2 : STD_LOGIC;BEGINQ2<= Q NOR CL;PROCESS(CLK0)BEGINIF CLK0’EVENT AND CLK=’1’THEN Q<=Q2;END IF;END PROCESS;OUT1<=NOT Q;END ARCHITECTURE ONE;第三章3-6LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MX3256 ISPort(INA : IN STD_LOGIC;INB : IN STD_LOGIC;INCK : IN STD_LOGIC;INC : IN STD_LOGIC;E : OUT STD_LOGIC;OUT1 : OUT STD_LOGIC);END MX3256ARCHITECTURE ar1 OF MX3256 ISCOMPONENT LK35PORT(A1 : IN STD_LOGIC;A2 : IN STD_LOGIC;CLK : IN STD_LOGIC;Q1 : IN STD_LOGIC;Q2 : IN STD_LOGIC); END COMPONENTSIGNAL t1: STD_LOGIC;SIGNAL t2: STD_LOGIC;SIGNAL t3: STD_LOGIC;SIGNAL t4: STD_LOGIC;BeginInst1: lk35 Port map(A1=>INA, A2=>INB,CLK=>INCK,Q1=>t3,Q2=>t2); Inst2: lk35 Port map(A1=>t2, A2=>t1,CLK=>INCK,Q1=>t4,Q2=>OUT1); Process (INCK,INC)BeginIf (INC=’0’) thent1<=’0’;elseif (rise_edge(inck)) thent1<=t2;end if;end process;e<=t4 when t2=’0’ elset3;END ARCHITECTURE ar1; t4t2t3t1第三章3-7方法一:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT16 ISPORT(CLK,RST,EN:IN STD_LOGIC;CHOOSE:IN BIT;COUT: OUT STD_LOGIC_VECTOR(15 downto 0));END ENTITY CNT16;ARCHITECTURE ONE OF CNT16 ISBEGINPROCESS(CLK,RST)VARIABLE QI: STD_LOGIC_VECTOR(15 downto 0);BEGINIF RST='1' THEN --计数器异步复位QI:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN=’1’ THEN –-检测是否允许计数IF CHOOSE=’1’ THEN --选择加法计数QI:=QI+1; --计数器加一ELSE QI=QI-1; --计数器加一END IF;END IF;END IF;COUT<=QI;--将计数值向端口输出END PROCESS;END ARCHITECTURE ONE;方法二:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT16 ISPORT(CLK,RST,EN,SET:IN STD_LOGIC;――用于置位,由于题目没有要求可以删掉CHOOSE:IN BIT; --用于控制加减SETDATA:BUFFER INTEGER RANCE 65535 DOWNTO 0; ――用于置位,由于题目没有要求可以删掉 COUT: BUFFER INTEGER RANGE 65535 DOWNTO 0);――为什么数的范围是65535 DOWNTO 0,原因是题目要求16二进制数的范围是65535 DOWNTO 0,同时BUFFER端口模式可以定义为OUT,数据类型定义为STD_LOGIC_VECTOR(65535 DOWNTO 0)(为什么?)END ENTITY CNT16;ARCHITECTURE ONE OF CNT16 ISBEGINPROCESS(CLK,RST,SDATA)VARIABLE QI: INTEGER RANGE 65535 DOWNTO 0; ――为什么整数的范围是65535 DOWNTO 0,原因是题目要求16二进制数的范围是65535 DOWNTO 0,同时数据类型定义为STD_LOGIC_VECTOR(65535 DOWNTO 0)(为什么?)BEGINIF RST='1' THEN --计数器异步复位QI:=0;ELSIF SET=’1’ THEN--计数器一步置位QI:=SETDATA;ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN=’1’ THEN –检测是否允许计数IF CHOOSE=’1’ THEN --选择加法计数QI:=QI+1; --计数器加一ELSE QI:=QI-1; --计数器加一END IF;END IF;END IF;COUT<=QI;--将计数值向端口输出END PROCESS;END ARCHITECTURE ONE ;。

E D A技术课程大作业-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII安阳工学院电子信息与电气工程学院课程大作业:EDA技术题目:组数:第 11 组班级:(电子信息工程10-1)教师成绩由以下评分标准累计得出1、电路设计和仿真结果正确清晰合理‘ 25%2、设计和仿真结果分析正确合理。

25%3、大作业报告重点突出、阐述清晰。

25%4、小组能很好的组织、合作,过程顺利,按时完成大作业。

15%5、陈述清晰正确、有说服力,能够正确回答问题。

10%总分学生自评分值大作业总成绩总成绩=J*60%+(J+J*(X-25%))*40% J 为教师成绩,X 为学生自评分值数字时钟1. 设计任务和设计方案1.1设计任务1、依据预先设定的数字数字时钟的功能,完成对数字钟的设计。

2、通过数字时钟的设计,学习Quartus II 中基于VHDL 设计的流程。

3、通过这次的设计,掌握简单时序逻辑电路的设计方法与功能仿真技巧。

1.2 设计方案在方案中要实现的功能是:(1)设置复位、清零等功能(2)有时、分、秒计数显示功能,小时为24进制,分钟和秒为60进制以24小时循环计时(3)有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间 (4)时钟通过数码管显示且时钟计数显示时有LED 灯显示; 总体方框图2. 方案实施根据系统设计要求,系统由时钟分频部分、计时部分、按键部分调时部分和显示部分五个部分组成。

这些模块都放在一个顶层文件中。

1)时钟计数:思路:时计时器为一个24进制计数器,分、秒计时器均为60进制计数器。

当秒计时器接受到一个秒脉冲时,秒计数器开始从1计数到60,此时秒显示器将显示00、01、02、...、59、00;每当秒计数器数到00时,就会产生一个脉冲输出送至分计时器,此时分计数器数值在原有基础上加1,其显示器将显示00、01、02、 (59)00;每当分计数器数到00时,就会产生一个脉冲输出送至时计时器,此时时计数器数值在原有基础上加1,其显示器将显示00、01、02、...、23、00。

EDA作业

072105班

第一题:加粗下划线部分为改正之后,括号部分为改正之前的原程序

改错1:

Signal A,EN : std_logic;

Process(A, EN)

Variable B: std_log ic;

Begin

if EN=l then B:=A; end if;(原程序为B<=A)

end process;

改错2:

Architecture one of sample is

variable a,b,c:integer;

begin

c:=a+b; (原程序为c<=a+b)

end;

改错3:

library ieee;

use ieee.std_logic_1164.all;

entity mux21 is

port(a,b:in std_logic;

sel:in std_loglc;

c:out std_logle);(将括号内的;去掉)

end entity mux21; (原程序为sam2)

architecture one of mux2l is

begin

process(a,b,sel)

begin(此句为增加)

if sel= '0' then c<=a; else c<=b; end if; (原程序为c:=a c:=b) end process; (此句为增加)

end architecture one;(原程序为two)

第二题:

程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SHFRT IS

PORT(CLK,LOAD:IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

QB:OUT STD_LOGIC);

END SHFRT;

ARCHITECTURE BEHAV OF SHFRT IS

BEGIN

PROCESS(CLK,LOAD)

VARIABLE REG8:STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF LOAD='1'THEN REG8:=DIN;

ELSE REG8(7 DOWNTO 1):=REG8(6 DOWNTO 0);

END IF;

END IF;

QB<=REG8(7);

END PROCESS;

END BEHAV;

电路图:

时序仿真:(见下页)。