图像DVI输出的FPGA实现

- 格式:pdf

- 大小:281.81 KB

- 文档页数:3

一种基于FPGA控制全彩大屏幕显示的设计随着数字技术的飞快进展,各种数字显示屏也随即涌现出来有、、DLP 等,各种数字大屏幕的控制系统多种多样,实用+脱机控制系统,也实用PC+DVI接口解码芯片+FPGA芯片联机控制系统,在这里我们叙述一种不仅可以用于控制全彩LED大屏幕的显示,而且还可以作为发送端输出高清图像数据。

采纳的联机控制系统对全彩LED大屏幕举行控制。

即PC+DVI接口解码芯片+FPGA芯片+输出接口模式的联机控制系统。

一、DVI接口概述DVI全称为Digital Visual Interface,它是基于TMDS(Transition Minimized Differential Signaling,最小化传输差分信号)协议作为基本电气衔接。

TMDS是一种微分信号机制,可以将像素数据编码,并通过串行衔接传递。

显卡产生的数字信号由发送器根据TMDS协议编码后通过TMDS通道发送给接收器,经过解码送给数字显示设备。

目前的DVI接口分为两种,一个是DVI-D接口,只能接收数字信号,接口上惟独3排8列共24个针脚,其中右上角的一个针脚为空,不兼容模拟信号。

另外一种则是DVI-I接口,可同时兼容模拟和数字信号。

兼容模拟幸好并不意味着模拟信号的D-Sub接口可以衔接在DVI-I接口上,而是必需通过一个转换接头才干用法,普通采纳这种接口的显卡都会带有相关的转换接头。

本文讲述中用到的接口是DVI-D全数据接口。

二、FPGA控制全彩LED大屏幕系统原理1 DVI解码芯片控制原理图3输入部分显示了FPGA芯片控制解码芯片控制原理图,所选的FPGA 芯片是公司的Spantan_3系列的X3C1400A-5,该芯片可以实现对DDR_SDRAM最大时钟为200MHz的控制。

在该系统中用到的DVI解码芯片是TI公司生产的芯片型号为tfp401的解码芯片,该芯片通过接收由计算机DVI接口传输来的编码图像数据,输出到DVI解码芯片,该第1页共4页。

基于DVI和FPGA的视频叠加器设计关键字:视频叠加器飞机研发过程中,需要对包含目标信息和地图信息的机载视频信号进行调试。

但是机载显示终端普遍存在价格昂贵、使用寿命短等缺点,如果使用它不断地调试机载视频信号,则机载显示终端的消耗会增大,研发成本将大幅提高。

本文介绍了一种DVI视频信号叠加器的设计方案,可以对两组相同分辨率和刷新频率的DVI 视频信号转化、合成并输出。

通过该系统,从路图像的非黑像素能够覆盖主路图像相同坐标的像素,从而完成对机载显示终端的模拟。

该方案主要以1024×768@60Hz的视频源为研究对象,可根据实际需要调节,并可支持多种分辨率和刷新频率(640×480@60Hz,800×600@60Hz,1024×768@60Hz)。

由于设计了这种模拟装置,因此不必用机载显示终端调试机载视频信号,从而减少对机载显示终端的消耗。

DVI视频信号叠加器的使用,节约了开发成本。

1 DVI接口数字视频接口(DVI)是一种适应数字显示器飞速发展而产生的显示接口。

DVI 标准由DDWG (Digital Display Working Group)于1999年4月正式推出,该组织包括了Intel、IBM、HP、Silicon Image、NEC等众多芯片及整机的生产厂家,因而DVI 标准具有广泛的业界支持[1]。

DVI 的接口主要有两种类型:DVI-Digital(DVI-D),只支持数字式显示器,共24 个引脚;DVI-Integrated(DVI-I),兼容模拟和数字的连接,共29个引脚。

计算机显卡一般有DVI-I和VGA 两个接口。

本设计选用的是DVI-I 接口,相对于VGA(Video Graphics Array)接口,其优势突出,DVI传输的是数字信号,数字图像信息不需经过数字→模拟→数字繁琐的转换过程,就会直接被传送到显示设备上,大大节省了时间,因此它的速度更快,能有效消除拖影现象。

基于FPGA的视频转换系统设计任勇峰;王大伟;石永亮;于丽娜【摘要】为解决不同视频系统之间显示时序、色彩空间、帧频、分辨率等不一致的问题,设计了一种以FPGA为控制核心, DDR2 SDRAM为高速缓存的视频转换系统,该系统从图形工作站采集到DVI视频,先进入高速缓存模块,然后通过视频转换算法在FPGA内部完成RGB至YCbCr的色彩空间转换,最后控制硬件实现PAL视频输出,实现了由DVI视频向PAL视频的转换。

经长期测试证明:该系统稳定可靠,达到设计要求。

%In order to solve the display between different video systems in consistencies timing,color space,framerate,resolution,etc,a video conversion system was designed,which regards FPGA as the control core,DDR2 SDRAM for cache. the device system collected DVI video from workstation graphics,firstly enters the cache mod⁃ule,and then completes the color space conversion and frame rate conversion via video conversion algorithm within the FPGA,and finally controls hardware PAL video output,completed by the DVI video conversion to PAL video. The long-term test proves:the system is stable and reliable,and meet the design requirements.【期刊名称】《电子器件》【年(卷),期】2016(039)003【总页数】7页(P655-661)【关键词】视频转换;DVI;PAL;高速缓存;转换算法【作者】任勇峰;王大伟;石永亮;于丽娜【作者单位】中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学仪器科学与动态测试教育部重点实验室;中北大学电子测试技术重点实验室,太原030051【正文语种】中文【中图分类】TP274.2随着多媒体信息技术的高速发展,视频技术多元化发展成为趋势,而同时也激化了视频系统之间互联的矛盾。

基于 FPGA 的硬件加速的图像处理方案随着科技的快速发展,图像处理技术在各行各业中的应用越来越广泛。

随之而来的挑战是如何在处理数量众多的图像时提高处理速度和效率。

这就需要一种高效的图像处理方案,基于 FPGA 的硬件加速技术是其中的一个解决方案。

FPGA 的意思是现场可编程逻辑门阵列,是一种基于可编程电路的硬件加速器。

它与传统的 CPU 和 GPU 不同,可以根据项目需求进行编程,可以实现高速计算,节省大量的时间和成本。

因此,FPGA 成为了许多高性能应用程序的首选硬件加速器,例如高速网络包处理、高速数据加密和解密以及高速图像处理。

FPGA 可以实现高效的图像处理,是因为它在硬件级别上实现了并行性。

FPGA 的架构可以方便地将大量的图像处理任务分割成多个小任务,由多个处理模块并行处理。

由于这种并行性可以在硬件中实现,所以 FPGA 可以在处理图像上实现比 CPU 和 GPU 更高的效率和速度。

FPGA 的图像处理通常可以分为三个步骤:图像输入、图像处理和图像输出。

其中,图像输入可以通过图像传感器、摄像头或者文件系统进行读取。

读取后的图像必须经过预处理才能用于后续处理。

预处理包括图像格式转换、调整图像大小和对比度等。

在图像处理阶段中,硬件处理单元通常使用 SIMD(单指令多数据)架构,采用流水线处理方式,以便同时处理多个像素点。

常见的图像处理算法包括边缘检测、直方图均衡化和滤波等。

这些算法在 CPU 或 GPU 上的计算效率很低,但在 FPGA 上可以通过硬件并行性快速计算。

最后,处理完的图像必须进行输出。

输出可以采用显示器、视频输出或者文件输出方式。

同样需要对输出图像进行格式转换。

以边缘检测算法为例,FPGA 的实现非常高效。

该算法采用锐化、梯度计算和非极大值抑制三个步骤来检测图像中的边缘。

在 FPGA 中,这些步骤可以使用多个处理模块并行处理。

这种处理方式的优势在于,可以通过添加硬件模块来增加处理性能,从而达到处理大量图像的目的。

基于FPGA的LVDS视频图像采集与预处理系统的设计实现作者:黄国鹏刘卫东乔明胜陈兴锋来源:《现代显示》2009年第02期文章编号:1006-6268(2009)02-0032-04摘要:以LED背光源液晶电视为应用背景,在FPGA硬件平台上实现了LVDS视频图像采集和直方图预处理系统的设计。

关键词:现可编程门阵列;低压差分信号;直方图;约束中图分类号:TN911.73文献标识码:ADesign and Implement of FPGA-based LVDS Video Acquisition and Preprocessing SystemHUANG Guo-peng1,LIU Wei-dong1,2,QIAO Ming-sheng2,CHEN Xing-feng1(1.Dept. of Electrical Engineering ,Ocean University of China,Qingdao 266100;2. Hisense Electric Co.,Ltd, Qingdao 266071)Abstract:This paper ,taking LED backlight for LCD TV as application background, has researched to achieve LVDS video acquisition and preprocessing system based on FPGA .Keywords: FPGA;LVDS;histogram;constraints引言FPGA在信号实时处理领域得到越来越广泛的应用。

相比ASIC和DSP,FPGA有更高的吞吐量、位级的可编程能力、开发周期短和风险大大降低等优点。

随着65nm甚至45nm工艺技术的面世,FPGA在逻辑门集成数量和工作的频率上取得了很大的提高。

在大数量数据处理领域,其并行处理数据的优势可以得到充分体现,特别是在在图像帧速率和分辨率要求比较高的场合使用高速大容量FPGA可以得到令人满意的结果。

图像D V I 输出的FPGA 实现陈沛文,邓 彬(电子科技大学电子工程学院 四川成都 610054)摘 要:提出了一种专用图像处理卡中的图像输出子系统的设计方法,详细描述了设计流程和思考方式。

他采用双握手机制、精度计数器,多频率锁相环等技术在FPGA (EP 1S 10)中实现了通用DV I 控制模块,并通过DV I 转换芯片S II 164实现多格式DV I 图像输出,其输出符合DV I 协议和V ESA 通用时间公式。

通过对参数的调整该子系统能很好地完成非标准图像处理领域中对特殊格式输出的需要。

同时从V ESA 通用时间公式出发,讨论了参数的计算公式,给出了标准的计算方法。

关键词:DV I ;S II 164;verilog ;GT F中图分类号:T P 391141 文献标识码:B 文章编号:1004373X (2005)0806303I m plem en ta tion of D V I I mage Output Ba sed on FPGACH EN Pei w en ,D EN G B in(Schoo l of E lectronic Engineering ,U niversity of E lectronic Science &T echno l ogy of Ch ina ,Chengdu ,610054,Ch ina )Abs tra c t :T h is paper puts fo r w ard the design and realizati on of the subsystem in a special i m age transfer card ,and describes thedesign flow and reasons in detail 1It designs a general block w ith double shake hand m echanis m ,h igh p recisi on counter and m ulti p ly frequency output PLL to contro l the general DV I transfo r m ch i p S II 164on FPGA 1F itting the concep ti on of DV I and V ESA general ti m e fo r m ula 1T h rough adjustes param eters ,it can accomp lish the DV I output of special i m age fo r m at in the field of nonstandard i m age p rocess 1A t the sam e ti m e ,begin w ith V ESA general ti m e fo r m ula ,the paper discusses the fo r m ula of param eters calculati on ,and gives a standard w ay to calculate 1Ke yw o rds :DV I ;S II 164;verilog ;GT F收稿日期:20050111 目前常见的计算机图像DV I 输出设备多使用A T I 等国外厂商的标准显卡核心芯片,加少量外围设备完成图像的处理和输出工作,其输出多是标准的图像格式,由于技术保密,其具体实现的方法还未能完全公开。

但在某些非标准的图像处理应用领域中,目前还没有很好的解决办法。

本图像输出子系统为完全自主研制,在他的设计中,该系统完成根据控制模块给出的输出格式,将计算后的图像从图像缓冲区中取出,加上各种控制信号输出给S II 164,通过S II 164转变成标准的DV I 图像输出。

缓冲数据的读取及控制,多频率时钟的输出、控制信号的产生和同步都在FPGA 中实现,本文用V erilog 语言完成上述功能。

1 系统结构图像输出部分有以下3个流程,由S II 164和FPGA 共同完成:(1)FPGA 从输出图像缓冲区中取出象素数据。

(2)FPGA 调整时间参数,加各种同步信号,如象素时钟、象素数据、同步信号、控制信号,输入S II 164。

(3)S II 164接受象素数据和各种同步信号和控制信号,将24b 的数字信号转换成TM D S 输出。

连接原理图如图1所示。

图1 连接原理图FPGA 中的控制程序,必须很好地完成以下工作:给S II 164提供不间断的稳定的数据流 由于数据缓冲区选取了单端口SDRAM ,故数据的写入和读出不可能同时完成,必须采用比输出时钟快2倍以上的读时钟将少量数据取出,放入自定义的F IFO 中,调整速率后输出。

为保证读写不冲突和从FPGA 输出的数据流稳定,本设计采取双握手机制。

通过握手控制单元实现这一任务。

握手控制单元读取F IFO 中的数据深度指标,经过计算将其转变《现代电子技术》2005年第8期总第199期 嵌入式与单片机为2个标志信号:Fdatastop (输入数据停止),Fneeddata (请求数据输入),供SDRAM 控制模块根据当前的存储器操作情况决定是否提供数据。

根据输出格式的不同产生不同频率的象素时钟 本设计中由一个参数化的锁相环实现。

产生符合时间标准各种同步信号和控制信号,并在时钟稳定期提供输出象素数据 本设计中由数据使能、场同步、行同步,数据输出单元完成。

图2为FPGA 内部控制模块的R TL 图。

图2 FPGA 内部控制模块的R TL 图2 SII 164图3是S II 164的结构图,其中P lanl L ink D igital co re 将图像信息编码成3对TM D S 差分信号和差分时钟。

D ata Cap ture L ogic B lock捕捉图像数据和相关信号。

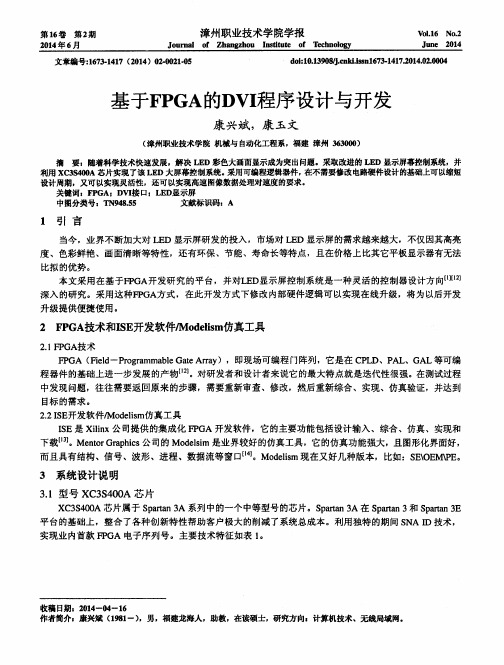

图3 S II 164结构图在FPGA 控制DV I 输出中,最关键的工作就是如何生成符合V ESA 时间标准的行同步场同步并准确地将图像数据输出。

3 VESA 时间通用规则V ESA (V ideo E lectronics Standards A ssociati on )[2]定义了标准的视频输出时间格式的通用计算公式(GT F ),任何图像输出或监视器中的时间参数都可以通过此系列公式计算得到,其中包括场频、行频、时间宽度和前后沿的计算及行场消隐期(blank )。

在计算机图像输出中有多种同步信号,他们的脉冲宽度和与视频的相对位置都是至关重要的,如图4所示通常同步脉冲都存在于场消隐期(blank peri od )。

图4 同步信号中脉冲宽度和视频水平同步信号一般占整个一行时间周期的8%,下降沿标志着整个行消隐期的一半。

垂直同步信号的宽度是3个行周期,他的前沿(the front po rch peri od )一般占1个行周期,隔行扫描的占半个行周期。

为了区别是何种同步信号,GT F 规定水平同步信号是负脉冲,垂直同步信号是正脉冲,混合同步信号是负脉冲。

由于目前的显示机制,一幅图像的开始和一场的开始之间总有时间上的间隔,于是GFT 定义了场消隐期:(Nvs+N bp )=round (T s -bp 3F h )其中:Nvs指vs 中的行周期数(一般是3);Nbp指vs 后沿的行周期数;T s -bp指通常情况下的后沿加同步脉冲宽度(一般定义550Λs )F h 为行频,单位kH z 。

同场消隐机理,可通过如下公式计算行消隐:B =C ′--M ′F h- 其中:C ′基础补偿常数,通常为30;M ′基础梯度常数,通常为300;F h 为行频。

B =-b lank ing peri od 3100(%)ho rizontal peri od根据上述公式,可以计算出各种格式的图像输出参数,同步信号的脉宽和时间关系。

表1为几种常用输出格式参数。

其中场前沿、后沿以行数为单位,行前沿、后沿以象素时钟数表示。

表1 常用输出格式参数屏幕区域刷新频率 H z 象素时钟频率 M H z 场前沿场后沿场同步脉宽行前沿行后沿10243768606532962416075781751183161768594151363482081280310246010813834824885157151443482404 控制模块设计中的关键点411 时钟时钟与同步是DV I 信号处理过程中至关重要的一环,不同的输出方式都需要提供不同频率的时钟。

在本设计中使用的是A ltera 公司的Stratix 系列的芯片EP 1S 10,多媒体技术陈沛文等:图像DV I 输出的FPGA 实现在此芯片中提供了6个锁相环,使用其中的任一快速PLL,经过参数化倍频分频常数,就可以产生多种象素时钟。

参数化的V erilog的具体实现如下:module p ll(inclk0,c0,param eters);input inclk0;output c0;Input[2:0]param enter;altp ll altp ll_component( 1inclk(sub_w ire3), 1clk(sub_w ire0,…(省略atp ll其他信号调用部分){clk0_duty_cycl,"altp ll",clk0_m ulti p ly_by,inclk0_input_ frequency,clk0_divide_by,"FA ST",clk0_ti m e_delay,"Stratix","NORM AL","CL K0",clk0_phase_sh ift});参数化过程case(param enter) 3′b000: clk0_duty_cycle=50; clk0_m ulti p ly_by=2; inclk0_input_=30303; clk0_divide_by=1; clk0_ti m e_delay="0"; altp ll_component1clk0_phase_sh ift="0"; 3′b001: …(省略其他频率时钟)412 输出数据与控制命令同步在FPGA内程序的设计中,为了保证器件的通用性,往往将电路设计为时序电路,这就不可避免地要加入若干个D触发器,使得第一次给出输出命令到数据输出有几个时钟周期的延时。

只有提前发出第一个读写指令才能保证输出数据与象素时钟控制命令的同步。