74HC573(八进制3 态非反转透明锁存器)

- 格式:pdf

- 大小:134.84 KB

- 文档页数:6

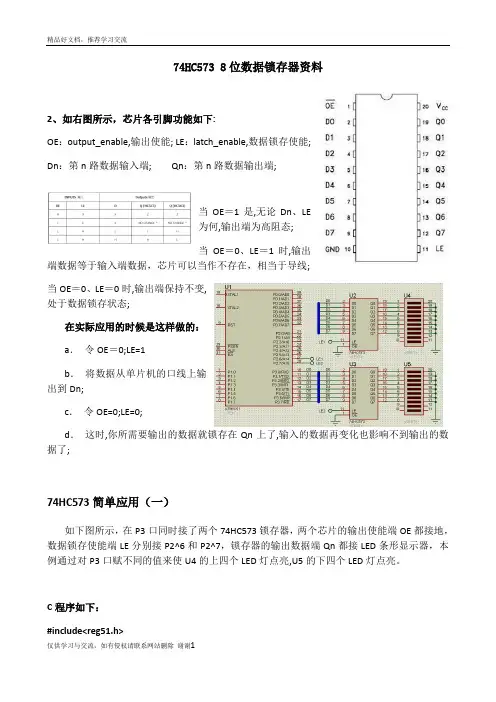

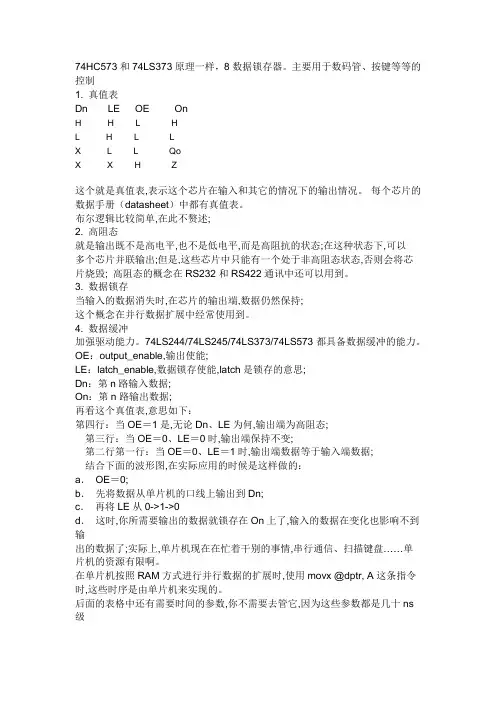

74HC573 8位数据锁存器资料2、如右图所示,芯片各引脚功能如下:OE:output_enable,输出使能; LE:latch_enable,数据锁存使能;Dn:第n路数据输入端; Qn:第n路数据输出端;当OE=1是,无论Dn、LE为何,输出端为高阻态;当OE=0、LE=1时,输出端数据等于输入端数据,芯片可以当作不存在,相当于导线;当OE=0、LE=0时,输出端保持不变,处于数据锁存状态;在实际应用的时候是这样做的:a.令OE=0;LE=1b.将数据从单片机的口线上输出到Dn;c.令OE=0;LE=0;d.这时,你所需要输出的数据就锁存在Qn上了,输入的数据再变化也影响不到输出的数据了;74HC573简单应用(一)如下图所示,在P3口同时接了两个74HC573锁存器,两个芯片的输出使能端OE都接地,数据锁存使能端LE分别接P2^6和P2^7,锁存器的输出数据端Qn都接LED条形显示器,本例通过对P3口赋不同的值来使U4的上四个LED灯点亮,U5的下四个LED灯点亮。

C程序如下:#include<reg51.h>sbit LE1=P2^6;sbit LE2=P2^7;void main(){LE1=1;P3=0X0F;LE1=0; //开启锁存功能,使U2输出端锁存数据0X0FLE2=1;P3=0XF0;LE2=0; //开启锁存功能,使U3输出端锁存数据0XF0while(1);}74HC573简单应用(二)两片74HC573的数据输入端同时接到P0口,输出使能端OE都接地,数据锁存端LE分别接到P2^6和P2^7,U2的数据输出端接六个数码管的段码,U3的数据输出端接六个数码管的位码。

本例使六个数码管同时循环点亮0到9十个数字。

C程序如下:#include<reg51.h>#define uchar unsignedc har#define uint unsigned int//延时函数void delay(uint x){uchar i;while(x--)for(i=0;i<120;i++);}//0到9的共阴显示代码uchar code dis[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; sbit LE1=P2^6;sbit LE2=P2^7;uchar i;void main(){ LE2=1;P0=0XC0;LE2=0;while(1){LE1=1;P0=dis[i];LE1=0;delay(400);//延时1s左右i=(i+1)%10;//i取值为0到9}}木兰诗北朝民歌唧(jī)唧复唧唧,木兰当户织。

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁; 高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

74hc573在应用电路作用解析74hc573驱动数码管动态扫描74HC573D是8位三态锁存器,一般在实际应用电路中用于地址或数据的锁存。

本文主要探讨了74HC573D在实际应用电路中的作用以及如何驱动数码管动态显示,下面就来一一介绍74HC573D。

大家都知道74HC573D是一种锁存器,那么锁存器是干嘛用的呢?锁存器辨析所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。

典型的锁存器逻辑电路是D 触发器电路。

PS:锁存信号(即对LE赋高电平时Data端的输入信号)。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用1:缓存、2:完成高速的控制其与慢速的外设的不同步问题、3:是解决驱动的问题(提供的电流比51IO口输出电流大)4:拓展I/O口(可以很猥琐的用锁存器幂叠加方法,即锁存器的Q再接锁存器~ 实现IO 口的无限拓展···)锁存器应用实例:I/O口复用:当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。

假设,MCU 端口其中的8 路的I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

(具体操作:先送地址信息,由ALE使能锁存器将地址信息锁存在外设的地址端,然后送数据信息和读写使能信号,在指定的地址进行读写操作)如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用到锁存器。

例如:一个I/O口要控制两个LED,对第一个LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个LED 上的数据不变。

对第二个LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个LED 上的数据不变。

如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。

就。

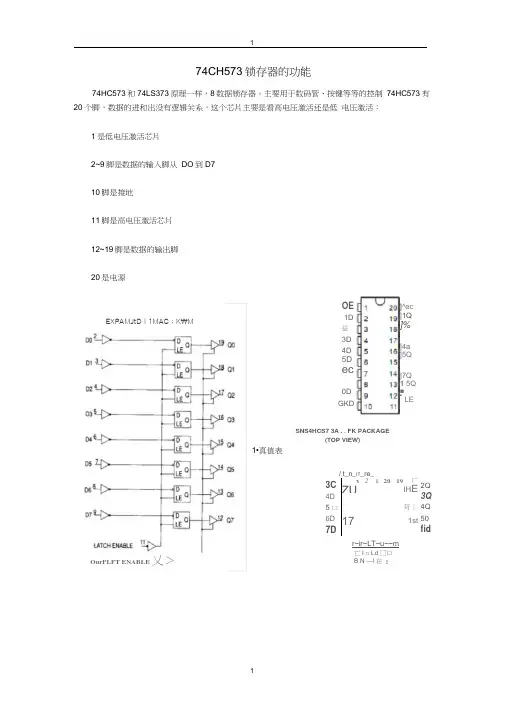

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

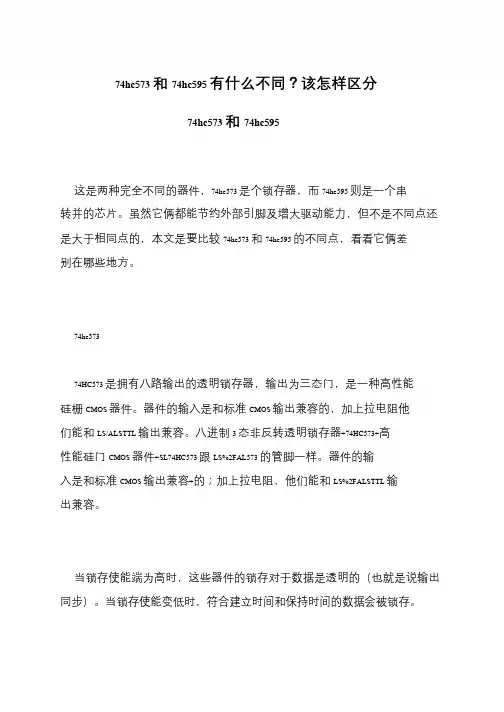

主要用于数码管、按键等等的控制 74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低 电压激活:1是低电压激活芯片2~9脚是数据的输入脚从 DO 到D710脚是接地11脚是高电压激活芯片12~19脚是数据的输出脚20是电源SNS4HCS7 3A . . FK PACKAGE(TOP VIEW)1•真值表3 2 1 20 19 厂ZUIH E苛[ 171stOE1D益3D 4D5Dec0D GKD]^ec ]1Q]%]4a ]5Q ]7Q 1 5Q ■ ■ILEOurPLFT ENABLE乂>EXPAMJtD I 1MAC ;K\M3C4D 5 口 6D7D/ t_n_IT _re_r~ir~LT~u~~m2Q 3Q4Q50fid亡I □ Ld □口 B N —l 在 g功能範高阻抗74HC573真值表,意思如下:第一行/第二行:当0E = 0、LE = 1时,输出端数据等于输入端数据;第三行:当0E = 0、LE = 0时,输出端保持不变;第四行:当0E = 1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573 都具备数据缓冲的能力。

0E : output_enable,输出使能;LE : latch_enable,数据锁存使能,atch是锁存的意思;Dn :第n路输入数据;On :第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:OE = 0;先将数据从单片机的口线上输出到 出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘 片机的资源有限啊。

74hc573原理74HC573是一种常用的集成电路芯片,属于高速CMOS逻辑系列。

它是一种8位透明锁存器,可以实现数据的存储和传输功能。

本文将介绍74HC573的原理和应用。

我们来了解一下74HC573的基本结构。

它由8个锁存器单元组成,每个单元都具有一个数据输入端(D)、一个时钟输入端(CK)和一个数据输出端(Q)。

这些单元可以独立地将数据存储在内部存储器中,并在时钟脉冲到达时将数据传输到输出端。

除此之外,74HC573还具有一个输出使能端( OE ),通过控制该端口的高低电平,可以使输出端的数据有效或者无效。

接下来,我们来看一下74HC573的工作原理。

当时钟输入端接收到一个信号时,数据输入端的数据会被存储在内部存储器中。

存储的数据可以通过数据输出端输出。

当输出使能端为高电平时,数据输出端的数据有效;当输出使能端为低电平时,数据输出端的数据无效。

通过控制输出使能端的状态,我们可以实现数据的读取和屏蔽操作。

那么,74HC573的应用有哪些呢?它广泛应用于数字电路中,特别是在数据存储和传输方面。

例如,在微处理器系统中,我们可以使用74HC573将数据从外部设备传输到微处理器中,或者将数据从微处理器传输到外部设备中。

它还可以用于存储数据,以便在需要时进行读取。

除了数据存储和传输外,74HC573还可以用于地址译码。

通过将地址线连接到74HC573的数据输入端,我们可以根据地址信号的不同将数据传输到不同的输出端。

这在存储器和外设的选择和控制中起着重要作用。

74HC573还可以用于时序控制。

通过控制时钟输入端和输出使能端的状态,我们可以实现对数据传输的控制。

例如,可以根据特定的时序要求将数据传输到其他模块,并在需要时将其输出。

总结一下,74HC573是一种功能强大的集成电路芯片,可以实现数据的存储和传输功能。

它广泛应用于数字电路中,特别是在数据存储、传输、地址译码和时序控制等方面。

通过灵活的控制和应用,我们可以实现不同的功能需求。

74hc573 和74hc595 有什么不同?该怎样区分

74hc573 和74hc595

这是两种完全不同的器件,74hc573 是个锁存器,而74hc595 则是一个串转并的芯片。

虽然它俩都能节约外部引脚及增大驱动能力,但不是不同点还是大于相同点的,本文是要比较74hc573 和74hc595 的不同点,看看它俩差别在哪些地方。

74hc573

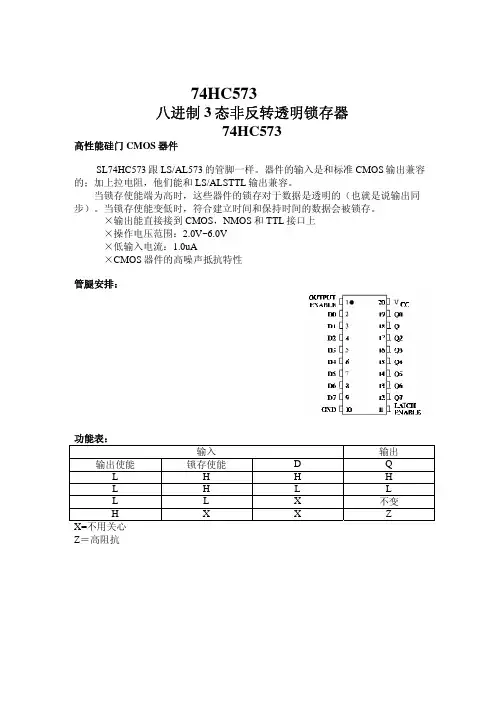

74HC573 是拥有八路输出的透明锁存器,输出为三态门,是一种高性能硅栅CMOS 器件。

器件的输入是和标准CMOS 输出兼容的,加上拉电阻他们能和LS/ALSTTL 输出兼容。

八进制3 态非反转透明锁存器+74HC573+高性能硅门CMOS 器件+SL74HC573 跟LS%2FAL573 的管脚一样。

器件的输入是和标准CMOS 输出兼容+的;加上拉电阻,他们能和LS%2FALSTTL 输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

![[2017年整理]74HC573功能说明](https://uimg.taocdn.com/c674141a854769eae009581b6bd97f192279bfef.webp)

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制。

74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低电压激活:1是低电压激活芯片2~9脚是数据的输入脚从D0到D710脚是接地11脚是高电压激活芯片12~19脚是数据的输出脚74HC573真值表,意思如下:第一行/第二行:当OE=0、LE=1时,输出端数据等于输入端数据;第三行:当OE=0、LE=0时,输出端保持不变;第四行:当OE=1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

◆OE:output_enable,输出使能;◆LE:latch_enable,数据锁存使能,atch是锁存的意思;◆Dn:第n路输入数据;◆On:第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0 ;d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A ; //将数据输出到并行数据端口CLR LESETB LECLR LE ; //上面三条指令完成LE的波形从0->1->0的变化74LS573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端.测量学试卷 第 4 页(共 7 页)《测量学》模拟试卷1.经纬仪测量水平角时,正倒镜瞄准同一方向所读的水平方向值理论上应相差(A )。

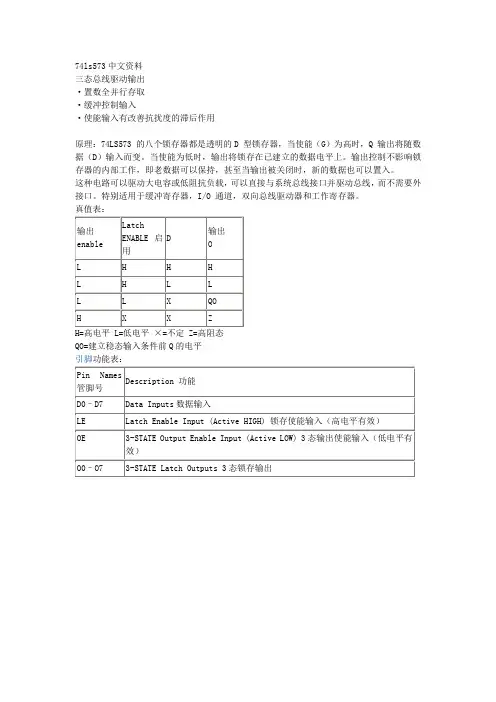

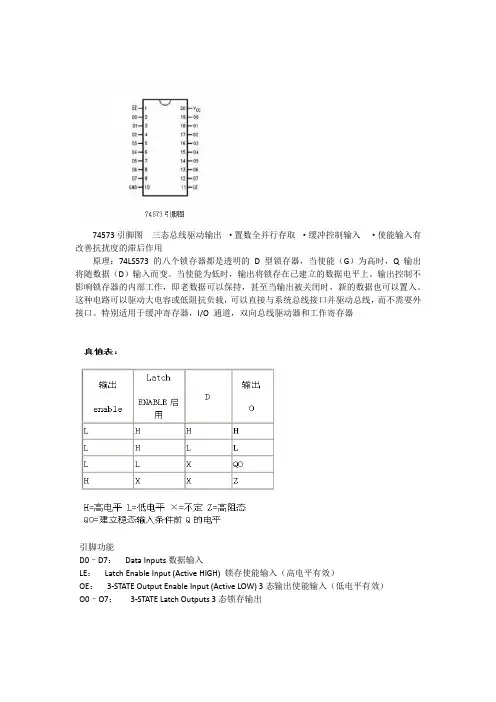

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

74573引脚图三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的 D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器引脚功能D0–D7:Data Inputs数据输入LE:Latch Enable Input (Active HIGH) 锁存使能输入(高电平有效)OE:3-STATE Output Enable Input (Active LOW) 3态输出使能输入(低电平有效)O0–O7:3-STATE Latch Outputs 3态锁存输出Operating Conditions 操作条件VCC :Supply Voltage 电源电压最小4.75V最大5.25VVIH :High Level Input Voltage输入高电平电压最小2VVIL:LOW Level Input Voltage 输入低电平电压最大0.8VIOH:HIGH Level Input Current输入高电平电流最大-2.6mAIOL:LOW Level Output Current低电平输出电流最大24mATA :Free Air Operating Temperature工作温度最大70摄氏度直流电气特性VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5 VVOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大 2.7 3.4 - VVOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5 - VIH = 最小- - - VIOL=4 mA, VCC=最小- - - -II Input Current @ 最大Input Voltage输入电压VCC=最大, VI=7V - - 1 mAIIH HIGH Level Input Current输入高电平电流VCC=最大, VI=2.7V - - 20 μAIIL LOW Level Input Current低电平输入电流VCC=最大, VI=0.4V - - −0.4 mAIOS Short CircuitOutput Current输出短路电流VCC=最大(Note 3) −30 - −130 mA -ICC Supply Current电源电流VCC=最大- - 50 mAIOZH 3-STATE Outputoff Current High 3态输出高阻态时高电平电流IOZL 3-STATE Outputoff Current Low 3态输出高阻态时低电平电流tPLH tPHL Propagation Delay传播延迟tPLH tPHL Propagation Delay传播延迟LE to Q - 36 25 ns tPZH tPZL 3-STATE Enable Time3态启用时间OE to Q - 20 25 nstPHZ tPLZ 3-STATE Enable Time3态启用时间OE to Q - 20 25 nsts(H)ts(L) Setup Time (High/Low) 设置时间(高/低)Data to LE 3 7 - nsth(H)th(L) Hold Time (High/Low)保持时间(高/低)Le Data to LE 10 10 - ns tw(H) - Pulse Width (High) 脉冲宽度(高)LeData to LE 15 - - ns看一下STC12C5A60S2系列1T单片机的功能就明白较89C51的优势了: 1.增强型8051 CPU,1T,单时钟/ 机器周期,指令代码完全兼容传统8051 2.工作电压:STC12C5A60S2 系列工作电压:5.5V - 3.3V STC12LE5A60S2 系列工作电压:3.6V - 2.2V 3. 工作频率范围:0 - 35MHz,相当于普通8051 的0~420MHz 4. 用户应用程序空间8K /16K / 20K / 32K / 40K / 48K / 52K / 60K / 62K 字节...... 5. 片上集成1280 字节RAM 6. 通用I/O 口(36/40/44 个),复位后为:准双向口/ 弱上拉(普通8051 传统I/O 口)可设置成四种模式:准双向口/ 弱上拉,推挽/ 强上拉,仅为输入/ 高阻,开漏每个I/O 口驱动能力均可达到20mA,但整个芯片最大不要超过120mA 7. I S P(在系统可编程)/IAP (在应用可编程),无需专用编程器,无需专用仿真器可通过串口(P3.0/P3.1)直接下载用户程序,数秒即可完成一片8. 有EEPROM 功能(STC12C5A62S2/AD/PWM 无内部EEPROM) 9. 看门狗10.内部集成MAX810 专用复位电路(外部晶体12M 以下时,复位脚可直接1K 电阻到地)11. 外部掉电检测电路: 在P4.6 口有一个低压门槛比较器5V 单片机为1.32V,误差为+/-5%,3.3V 单片机为1.30V,误差为+/-3% 12. 时钟源:外部高精度晶体/ 时钟,内部R/C 振荡器(温漂为+/-5% 到+/-10% 以内) 用户在下载用户程序时,可选择是使用内部R/C 振荡器还是外部晶体/ 时钟常温下内部R/C 振荡器频率为:5.0V 单片机为:11MHz ~15.5MHz 3.3V 单片机为:8MHz ~12MHz 精度要求不高时,可选择使用内部时钟,但因为有制造误差和温漂,以实际测试为准13. 共4 个16 位定时器:两个与传统8051 兼容的定时器/ 计数器,16 位定时器T0 和T1,没有定时器2,但有独立波特率发生器,做串行通讯的波特率发生器,再加上2 路PCA 模块可再实现2 个16 位定时器14. 2 个时钟输出口,可由T0 的溢出在P3.4/T0 输出时钟,可由T1 的溢出在P3.5/T1 输出时钟15. 外部中断I/O 口7 路,传统的下降沿中断或低电平触发中断,并新增支持上升沿中断的PCA 模块,Power Down 模式可由外部中断唤醒,INT0/P3.2, INT1/P3.3, T0/P3.4, T1/P3.5, RxD/P3.0, CCP0/P1.3(也可通过寄存器设置到P4.2 ), CCP1/P1.4 (也可通过寄存器设置到P4.3) 16. PWM(2 路)/PCA(可编程计数器阵列,2 路)--- 也可用来当2 路D/A 使用--- 也可用来再实现2 个定时器--- 也可用来再实现2 个外部中断(上升沿中断/ 下降沿中断均可分别或同时支持) 17. A/D 转换, 10 位精度ADC,共8 路,转换速度可达250K/S(每秒钟25 万次) 18. 通用全双工异步串行口(UART),由于STC12 系列是高速的8051,可再用定时器或PCA 软件实现多串口19. STC12C5A60S2 系列有双串口,后缀有S2 标志的才有双串口,RxD2/P1.2(可通过寄存器设置到P4.2),TxD2/P1.3(可通过寄存器设置到P4.3) 20. 工作温度范围:-40 - +85℃(工业级) / 0 - 75℃(商业级) 21. 封装:PDIP-40,LQFP-44,LQFP-48 I/O 口不够时,可用 2 到 3 根普通I/O 口线外接74HC164/165/595(均可级联)来扩展I/O 口,还可用A/D 做按键扫描来节省I/O 口,或用双CPU,三线通信,还多了串口。

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

74HC573锁存器与74HC37374HC573锁存器编程时,先将使能端置1,此时输出数据和输入数据一致;为了将输出的数据锁定,防止误操作,可将使能端清0,此时,输出端保持原有值,不再变化。

(1,使能置1; 2,数据输入到锁存器输入端(输出=输入); 3,使能置0(输出恒定=先前输入);(达到锁存功能))74HC系列的数字集成电路,当5V供电时,输出高电平接近5V,带负载后,能输出4.95V左右。

从你图上看,这里需要573输出高电平段码,138输出位码,进行动态显示。

但是图上有错,为了LED安全使用,在573的输出端与7LED连接之间,应串联300Ω电阻。

附加: 锁存器的作用锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制其与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。

74HC37374HC37374hc373中文资料:373为三态输出的八 D 透明锁存器,共有 54/74S373 和54/74LS373 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号 tPd PD54S373/74S373 7ns 525mW54LS373/74LS373 17ns 120mW373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。

当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端 LE 为高电平时,O 随数据 D 而变。

当 LE 为低电平时,O 被锁存在已建立的数据电平。

当 LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

74hc573锁存器作用

在LED和数码管显示方面,要维持一个数据的显示,往往要持续的快速的刷新。

尤其是在四段八位数码管等这些要选通的显示设备上。

在人类能够接受的刷新频率之内,大概每三十毫秒就要刷新一次。

这就大大占用了处理器的处理时间,消耗了处理器的处理能力,还浪费了处理器的功耗。

锁存器的使用可以大大的缓解处理器在这方面的压力。

当处理器把数据传输到锁存器并将其锁存后,锁存器的输出引脚便会一直保持数据状态直到下一次锁存新的数据为止。

这样在数码管的显示内容不变之前,处理器的处理时间和IO 引脚便可以释放。

可以看出,处理器处理的时间仅限于显示内容发生变化的时候,这在整个显示时间上只是非常少的一个部分。

而处理器在处理完后可以有更多的时间来执行其他的任务。

这就是锁存器在LED和数码管显示方面的作用:节省了宝贵的MCU时间。

锁存器和缓冲器的作用和区别

锁存器就是把当前的状态锁存起来,使CPU送出的数据在接口电路的输出端保持一段时间锁存后状态不再发生变化,直到解除锁定。

还有些芯片具有锁存器,比如芯片74LS244就具有锁存的功能,它可以通过把一个引脚置高后,输出就会保持现有的状态,直到把该引脚清0后才能继续变化。

缓冲寄存器又称缓冲器,它分输入缓冲器和输出缓冲器两种。

前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。

有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。

由于缓冲器接在数据总线上,故必须具有三态输出功能。

74LS373与74HC573对比驱动共阴极数码管哪个更好?虽说74LS573和74HC573都是八D锁存器(三态),并且在逻辑上完全一样,但是它俩管脚定义不一样。

74LS373是TTL电路,电源电压是5V。

上拉弱而下拉强。

输入内部有上拉,输入开路时为高电平。

74HC573是CMOS电路,电源电压工作范围是2V ~ 6V。

上拉下拉能力相同。

输入电阻很高,输入开路时电平不定。

74LS573和74HC573的不同点还是有很多的,不管是从它俩的引脚图还是参数或者是应用上,不过虽说不同点很多,但在某种层面上它俩是一样的。

本文主要比较74LS573和74HC573的异同点,详解它俩的工作特性及性能参数,比较在驱动共阴数码管上它俩谁更合适。

74ls37374LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。

在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。

本文将介绍74LS373的工作原理,内容涵盖引脚图、内部结构、主要参数以及在单片机扩展系统中的典型应用电路。

74HC57374HC573包含八路3态输出的非反转透明锁存器,是一种高性能硅栅CMOS器件。

SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的,加上拉电阻他们能和LS/ALSTTL输出兼容。

74LS573和74HC573在工作原理上的不同74ls373工作原理(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2)。

当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、。

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制 .74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低电压激活:✧1是低电压激活芯片✧2~9脚是数据的输入脚从D0到D7✧10脚是接地✧11脚是高电压激活芯片✧12~19脚是数据的输出脚✧20是电源1.真值表74HC573真值表,意思如下:➢第一行/第二行:当OE=0、LE=1时,输出端数据等于输入端数据;➢第三行:当OE=0、LE=0时,输出端保持不变;➢第四行:当OE=1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3。

数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

◆OE:output_enable,输出使能;◆LE:latch_enable,数据锁存使能,atch是锁存的意思;◆Dn:第n路输入数据;◆On:第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1-〉0 ;d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr,A这条指令时,这些时序是由单片机来实现的.后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A ; //将数据输出到并行数据端口CLR LESETB LECLR LE ;//上面三条指令完成LE的波形从0—〉1->0的变化74LS573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端.。