电子技术——几种常用的时序逻辑电路参考答案

- 格式:doc

- 大小:5.75 MB

- 文档页数:18

(完整版)电子技术基础习题答案三、选择题:(每小题2分,共20分)1、单极型半导体器件是(C)。

A、二极管;B、双极型三极管;C、场效应管;D、稳压管。

2、P型半导体是在本征半导体中加入微量的(A)元素构成的。

A、三价;B、四价;C、五价;D、六价。

3、稳压二极管的正常工作状态是( C)。

A、导通状态;B、截止状态;C、反向击穿状态;D、任意状态。

4、用万用表检测某二极管时,发现其正、反电阻均约等于1KΩ,说明该二极管(C)。

A、已经击穿;B、完好状态;C、内部老化不通;D、无法判断。

5、PN结两端加正向电压时,其正向电流是(A)而成。

A、多子扩散;B、少子扩散;C、少子漂移;D、多子漂移。

6、测得NPN型三极管上各电极对地电位分别为V E=2.1V,V B=2.8V,V C=4.4V,说明此三极管处在(A)。

A、放大区;B、饱和区;C、截止区;D、反向击穿区。

7、绝缘栅型场效应管的输入电流(C)。

A、较大;B、较小;C、为零;D、无法判断。

8、正弦电流经过二极管整流后的波形为(C)。

A、矩形方波;B、等腰三角波;C、正弦半波;D、仍为正弦波。

9、三极管超过(C)所示极限参数时,必定被损坏。

A、集电极最大允许电流I CM;B、集—射极间反向击穿电压U(BR)CEO;C、集电极最大允许耗散功率P CM;D、管子的电流放大倍数。

10、若使三极管具有电流放大能力,必须满足的外部条件是(C)A、发射结正偏、集电结正偏;B、发射结反偏、集电结反偏;C、发射结正偏、集电结反偏;D、发射结反偏、集电结正偏。

三、选择题:(每小题2分,共20分)1、基本放大电路中,经过晶体管的信号有(C)。

A、直流成分;B、交流成分;C、交直流成分均有。

2、基本放大电路中的主要放大对象是(B)。

A、直流信号;B、交流信号;C、交直流信号均有。

3、分压式偏置的共发射极放大电路中,若V B点电位过高,电路易出现(B)。

A、截止失真;B、饱和失真;C、晶体管被烧损。

电子技术_北京科技大学中国大学mooc课后章节答案期末考试题库2023年1.电路中引入交流负反馈,可以改善哪些方面的性能?参考答案:稳定输出电压_增大输入电阻_稳定输出电流2.经过变压、整流、滤波后得到的直流电源波动已经很小了,为什么还要稳压,以下哪个说法不正确?参考答案:提供更大的功率3.优先编码器只允许任意时刻只有一个输入,如果输入端同时有多个输入信号,输出会出现错误。

参考答案:错误4.如果想把一个正弦波信号,转变为一个周期方波信号,可以使用(_____)电路。

参考答案:电压比较器电路5.某8为A/D转换电路,当输入电压为0.125V时对应的数字量为“00000001”的时候,当输入为21.75时,输出数字量为参考答案:101011106.放大电路中,主要的性能指标有(_____)。

参考答案:输入电阻_输出电阻_电压放大倍数7.如果要把一个周期方波信号转换为周期锯齿波信号,可以使用(_____)电路。

参考答案:积分电路8.电路如图所示,设晶体管的β=80,试分析当开关K分别接通A、B、C三位置时,判断三极管工作在输出特性曲线的哪个区域。

【图片】参考答案:当开关K置B,三极管工作在放大区_当开关K置C,三极管工作在截止状态_当开关K置A,三极管工作在饱和区9.两片74LS151八选一构成()选一数据选择器;参考答案:十六10.已知十进制计数器芯片74LS160为同步置数,异步清零,下图为()进制计数器【图片】参考答案:24进制11.单运放构成的差分放大电路属于特殊的加减运算电路()。

参考答案:正确12.基本反相比例运算电路,输入信号接在()输入端。

参考答案:反相13.直流稳压电源包含下列哪些部分?参考答案:滤波部分_变压部分_整流部分_稳压部分14.一个10进制计数器最少需要参考答案:4个触发器15.正弦波振荡电路中只有正反馈环节,而没有负反馈环节。

参考答案:错误16.3线-8线译码器74LS138,低电平有效,译码状态时,当输入A2A1A0=001时,确定输出【图片】参考答案:1111110117.一个四位二进制计数器最大可能的进制是参考答案:1618.在二进制译码器中,若输入有5位代码,确定最大的输出信号的个数。

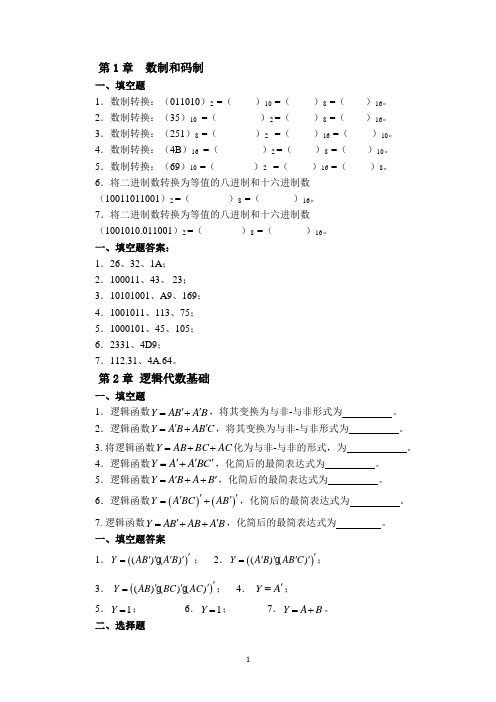

第1章 数制和码制一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数(10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数(1001010.011001)2 =( )8 =( )16。

一、填空题答案:1.26、32、1A ;2.100011、43、 23;3.10101001、A9、169;4.1001011、113、75;5.1000101、45、105;6.2331、4D9;7.112.31、4A.64。

第2章 逻辑代数基础一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=;3. ()()()()Y AB BC AC ''''=; 4. Y A '=;5.1Y =; 6.1Y =; 7.Y A B =+。

中南大学网络教育课程考试复习题及参考答案电子技术基础(专科)一、单项选择题:1.在杂质半导体中,少子浓度主要取决于[]A.掺入杂质的浓度B.材料C.温度2.测得某PNP型三极管各极点位为:UB=-3VUE=-4V UC=-6V,则该管工作于[ ]A.放大状态B.饱和状态C.截止状态3.在基本共射放大电路中,若更换晶体管使8值由50变为100,则电路的放大倍数[]A.约为原来的1/2倍B.约为原来的2倍C.基本不变4.在0CL电路中,引起交越失真的原因是[]A.输入信号过大B.晶体管输入特性的非线性C.电路中有电容5.差动放大器中,用恒流源代替长尾Re是为了[]A.提高差模电压增益B.提高共模输入电压范围C.提高共模抑制比6.若A+B=A+C,则[ ]A.B=CB.B=CC.在A=0的条件下,B=C7.同步计数器中的同步是指]] ] ] ]13.将代码(10000011)8421BCD转换成二进制数为A.(01000011)2B.(01010011)2C.(10000011)214.N个变量的逻辑函数应该有最小项A.2n个B.n2个C.2n个[] D.(000100110001)2[]D.(2nT)个15.函数F=AB+AB转换成或非一或非式为A.各触发器同时输入信号B.各触发器状态同时改变C.各触发器受同一时钟脉冲的控制8.由NPN管组成的单管基本共射放大电路,输入信号为正弦波,输出电压出现顶部被削平的失真,这种失真是[A.饱和失真B.截止失真C.频率失真9.对PN结施加反向电压时,参与导电的是[A.多数载流子B.少数载流子C.既有多数载流子又有少数载流子10.当温度增加时,本征半导体中的自由电子和空穴的数量[A.增加B.减少C.不变11.通用型集成运放的输入级采用差动放大电路,这是因为它的[A.输入电阻高B.输出电阻低 c.共模抑制比大 D.电压放大倍数大12.对于桥式整流电路,正确的接法是[16.图示触发器电路的特征方程Qn+1二—n —A. TQ+TQ nB. TQ +TQn一nc.Q D.TB.一个稳定状态,一个暂稳态 D.记忆二进制数的功能)空穴浓度,N 型半导体的电子浓度(浓度()空穴浓度A.等于、大于、小于B.小于、等于、大于C.等于、小于、大于 19 .稳压管构成的稳压电路,其接法是 A.稳压二极管与负载电阻串联B.稳压二极管与负载电阻并联。

第9章时序逻辑电路习题解答9.1 d R端和d S端的输入信号如题9.1图所示,设基本RS触发器的初始状态分别为1和0两种情况,试画出Q端的输出波形。

题9.1图解:9.2 同步RS触发器的CP、R、S端的状态波形如题9.2图所示。

设初始状态为0和1两种情况,试画出Q端的状态波形。

题9.2图解:9.3 设主从型JK触发器的初始状态为0,J、K、CP端的输入波形如题9.3图所示。

试画出Q端的输出波形(下降沿触发翻转)。

解:如题9.3图所示红色为其输出波形。

第9章时序逻辑电路225题9.3图9.4 设主从型JK触发器的初始状态为0,J、K、CP端输入波形如题9.4图所示。

试画出Q端的输出波形(下降沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:如题9.4图所示红色为其输出波形。

题9.4图9.5 设维持阻塞型D触发器的初始状态为0,D端和CP端的输入波形如题9.5图所示,试画出Q端的输出波形(上升沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:如题9.5图所示红色为其输出波形。

第9章时序逻辑电路226题9.5图9.6 根据CP时钟脉冲,画出题9.6图所示各触发器Q端的波形。

(1)设初始状态为0;(2)设初始状态为1。

(各输入端悬空时相当于“1”)题9.6图解:第9章时序逻辑电路2279.7 题9.7图所示的逻辑电路中,有J和K两个输入端,试分析其逻辑功能,并说明它是何种触发器。

题9.7图=⋅⋅⋅=⋅+⋅解:由图得D Q F J Q Q F J QJ K Q n D Q n+10 0 0 0 00 0 1 1 10 1 0 0 00 1 1 0 01 0 0 1 11 0 1 1 11 1 0 1 11 1 1 0 0此电路为D触发器和与非门组成的上升沿触发的JK触发器。

9.8 根据题9.8图所示的逻辑图和相应的CP、d R、D的波形,试画出Q1和Q2端的输出波形。

设初始状态Q1=Q2=0。

题9.8图解:第9章时序逻辑电路2289.9 试用4个D触发器组成一个四位右移移位寄存器。

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

第8章 触发器和时序逻辑电路及其应用习题解答8.1 已知基本RS 触发器的两输入端D S 和D R 的波形如图8-33所示,试画出当基本RS 触发器初始状态分别为0和1两种情况下,输出端Q的波形图。

图8-33 习题8.1图解:根据基本RS 触发器的真值表可得:初始状态为0和1两种情况下,Q的输出波形分别如下图所示:习题8.1输出端Q的波形图8.2 已知同步RS 触发器的初态为0,当S 、R 和CP 的波形如图8-34所示时,试画出输出端Q的波形图。

图8-34 题8.2图解:根据同步RS 触发器的真值表可得:初始状态为0时,Q的输出波形分别如下图所示:习题8.2输出端Q的波形图8.3 已知主从JK触发器的输入端CP、J和K的波形如图8-35所示,试画出触发器初始状态分别为0时,输出端Q的波形图。

图8-35 习题8.3图解:根据主从JK触发器的真值表可得:初始状态为0情况下,Q的输出波形分别如下图所示:习题8.3输出端Q的波形图8.4 已知各触发器和它的输入脉冲CP的波形如图8-36所示,当各触发器初始状态均为1时,试画出各触发器输出Q端和Q端的波形。

图8-36 习题8.4图解:根据逻辑图及触发器的真值表或特性方程,且将驱动方程代入特性方程可得状态方程。

即:(a )J =K =1;Qn +1=n Q,上升沿触发 (b)J =K =1;Qn +1=n Q, 下降沿触发 (c)K =0,J =1;Qn +1=J n Q+K Qn =1,上升沿触发 (d)K =1,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0·Qn =n Q,上升沿触发 (e)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,上升沿触发 (f)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,下降沿触发, 再根据边沿触发器的触发翻转时刻,可得当初始状态为1时,各个电路输出端Q的波形分别如图(a )、(b )、(c )、(d )、(e )和(f )所示,其中具有计数功能的是:(a )、(b )、(d )、(e )和(f )。

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

电子技术考题大全及答案(完整版)1. 时序逻辑电路的分析方法有()。

A、列写状态方程B、列写驱动方程C、列写状态表D、以上都是2. 用毫伏表测出电子电路的信号为( )A、平均值B、有效值C、直流值D、交流值3. 当74LS138的控制信号为01时,该集成移位寄存器处于( )态。

A、左侈B、右移C、保持D、并行置数4. 集成译码器7LS138的3个使能端,只要有一个不满足要求,其八个输出为( )。

A、高电平B、低电平C、高阻D、低阻5. 集成计数器741S192是( )计数器。

A、异步十进制加法B、同步十进制加法C、异步十进制减法D、同步十进制可逆6. 集成运放电路引脚如插反,会( ),会损坏运放。

A、将电源极性接反B、输人接反C、输山接反D、接地接反7. 集成译码器的( )状态不对时。

译码器无法工作。

A、输入端B、输出端C、清零端D、使能端8. 由与非门组成的基本RS触发器,当RS为( )时,触发器处于不定状态。

A、00B、01C、10D、ll9. 时序逻辑电路的输出端取数如有问题会产生( )。

A、时钟脉冲混乱B、SW无效C、清零端规D、计数模错误10. 晶闸管触发电路所产生的触发脉冲信号必须要( )。

A、有一定的电位B、有一定的电抗C、有一定的频率D、有一定的功率11. 锯齿波触发电路中的锯齿波是由( )对电容器充电以及快速放电产生的。

A、矩形波电源B、正弦波电源C、恒压源D、恒流源12. 下列不属于常用稳压电源电子单元电路的功能有( )。

A、输出电压稳定B、抗干扰能力强C、具有一定过载能力D、波形失真小13. 微分集成运放电路反馈元件采用的是( )元件。

A、电感B、电阻C、电容D、三极管14. 过零比较器可将输入正弦波变换为( )。

A、三角波B、锯齿波C、尖顶脉冲波D、方波15. 组合逻辑电路常采用的分析方法有( )。

A、逻辑代数化简B、真值表C、逻辑表达式D、以上都是16. 组合逻辑电路的译码器功能有( )。

第七章几种常用的时序逻辑电路参考答案一、选择题1.当时的输入信号,电路原来状态,a2.a3.b4.b5.JK6.基本RS,1R S+=(RS=0)7.T8.1,1n nQ Q+=9.J=K=T;J=K=T=1;J=D,K=D10.n nD TQ TQ=+;nD Q=11.并行,串行;并行输出,串行输出12.数码,移位13.清零14.同步计数器,异步计数器。

15.a,清零,置数,保持16.b17.异步,同步。

18.a,M*N19.2,双稳态触发器20.双向移位二、判断题1. B2. C3. C4. D5. B6. A7. C8. C9. A10. B11. C12. D13. D14. B15. D16. D17. A18. C19. C20. D三、判断题1.错2.对3.对4.错5.对6.错7.对8.对9.错10.错11.对12.对13.对14.错15.对四、简答题1.(9-1易)图示是用与非门组成的基本RS触发器试根据其特性表,并写出特性方程和约束条件。

R SnQ1n Q+功能0 0 0 0 01不定不定不允许0 1 0 1 01置010 1 0 011置11 1 1 1 011保持参考答案:特征方程:1n nQ S RQ+=+,约束条件:1R S+=2.(9-1中) 用JK 触发器(特性方程1n n n Q JQ KQ +=+)可以转换成其他逻辑功能触发器,适当连接给出的JK 触发器的输入端分别将其转换成: 1).T 触发器(1n n n Q TQ TQ +=+) 2).T ’触发器(1n n Q Q +=) 3).D 触发器(1n Q D +=)参考答案:3.(9-1中)写出JK 触发器,T 触发器,T ’触发器,D 触发器的特性方程。

参考答案:JK 触发器特性方程:1n n n Q JQ KQ +=+T 触发器特性方程:1n n n Q TQ TQ +=+ T ’触发器特性方程:1n n Q Q += D 触发器特性方程:1n QD +=4.(9-3中)同步计数器的同步是指什么? 参考答案:所谓同步指组成计数器的所有触发器共用一个时钟脉冲,使应该翻转的触发器在时钟脉冲作用下同时翻转,并且该时钟脉冲即输入的计数脉冲。

5.(9-3易)将两个二输入与非门的输出接回到对方的输入之一,则可组成什么触发器?试列出其特性表 参考答案: 基本RS 触发器。

6.(9-1中)基本RS 触发器如图所示,试画出Q 对应R 和S 的波形(设Q 的初态为0)。

参考答案:7.(9-1难)同步RS触发器(CP=1时R和S信号有效且等同与基本RS触发器)如图所示,试画出Q对应R和S的波形(设Q的初态为0)。

参考答案:8.(9-1中)用2个或非门也可以组成基本RS触发器。

1).试画出逻辑电路。

2).试列出其特性表。

参考答案:1).逻辑电路:2).特性表:R S 1nQ0 0 nQ0 1 11 0 01 1 不定9.(9-1中)已知CP、D的波形如图题5-6,试画出高电平有效和上升沿有效D触发器Q的波形(设Q的初态为0)。

参考答案:10.(9-1难*)设图中的触发器的初态均为0,试画出Q端的波形。

参考答案:11.(9-1难)设图中的触发器的初态均为0,试画出对应A、B的X、Y的波形。

参考答案: 根据1n QD +=,可画出电路波形:12.(9-1中)基本RS 触发器的特性方程是:1n n QS RQ +=+,D 触发器的特性方程是1n Q D +=,比较这两个方程,试将基本RS 触发器转换为D 触发器。

参考答案:D=1时,等同于S=1,R=0; D=0时,等同于S=0,R=1; 可见,让S=D,R=D ,即可。

13.(9-1中)由或非门组成的基本RS 触发器输入波形如图所试,试画出输出Q 和Q 端的波形。

设触发器的初始状态为Q=0。

参考答案:输出Q 和Q 端的波形如图,当输入R 、S 都为高电平时,输出Q 和Q 都为低平。

工作时,这种情况不允许存在。

图中斜线部分为输出不定状态。

14.(9-1难)同步D 触发器(1n QD +=,CP 上升沿有效,CP=1时有效)的输入波形如图所示,试画出输出Q 和Q 的波形。

设触发器的初始状态为Q=0。

参考答案:输出Q 和Q 端的波形如图所示。

15.(9-1难) TTL 边沿JK 触发器如图(a)所示,输入CP 、J 、K 端的波形如图(b)所示,试对应画出输出Q 和Q 端的波形。

设触发器的初始状态为Q=0。

参考答案:该题为下降沿触发有效的边沿JK触发器,根据CP下降沿到来前一瞬间的J、K输入状态,决定输出状态。

输出Q和Q端的波形如图所示。

16.(9-1难)电路如图(a)所示,输入CP、A、B的波形如图(b)所示,试画出Q和Q端的输出波形。

设触发器的初始状态为Q=0。

参考答案:图 (a),为上升沿触发有效的D触发器,由于D=AB,因此A、B中有0时,D=1,A、B全1时,D=0。

根据CP上升沿到来前一瞬间D的输入状态确定输出状态,Q和Q端的输出波形如图所示。

17.(9-1难*)如图所示各边沿D触发的初始状态都为0,试对应输入CP波形画出Q端的输出波形。

参考答案:根据D端的输入信号和时钟脉冲CP的出发边沿画各D触发器输出Q端的波形,如图所示。

18.(9-1难*)如图所示各边沿JK 触发器的初始状态都为1,试对应CP 波形画出Q 端的输出波形(1n n n Q JQ KQ +=+)。

参考答案:根据JK 触发器J 、K 端的输入信号和时钟脉冲CP 的触发边沿画出各个JK 触发器输出Q 端的波形,如图所示。

19.(9-1难)下降沿触发的边沿JK 触发器的输入CP 、J 、K 和R D 端的波形如图所示(1n n n Q JQ KQ +=+),D R 为异步置0端,低电平有效。

试画出输出Q 端的波形。

设触发器的初始状态Q=0,且1=D S 。

参考答案:边沿JK 触发器输出Q 端的波形如图所示。

20.(9-3中)我们经常要对计数器电路进行分析。

当给你一个逻辑电路的实例时,大体分析步骤如何? 参考答案:1).写出时钟方程、驱动方程、输出方程。

2).求状态方程。

3).进行状态计算,列状态表。

4).画出状态转换图。

21.(9-1难)电路如图(a)所示,输入时钟脉冲CP 如图(b)所示,试画出输出Q 0和Q 1端的波形。

设触发器的初始状态Q 0=Q 1=0。

参考答案:由图可写出D 触发器FF 0和FF 1的特性方程n n Q Q 11=+ (CP 上升沿到时刻有效)n n Q Q 011=+ (CP 上升沿到时刻有效)根据FF 0和FF 1的状态和两个特性方程画出输出Q 0和Q 1的波形,如图所示。

22.(9-2易)移位寄存器有哪几种? 参考答案:1).右移寄存器;2).左移寄存器;3).双向移位寄存器。

23.(9-1难)在图(a)所示的边沿触发器中,输入CP 、D 端的波形如图(b)所示,试画出Q 0和Q 1端的输出波形。

设触发器的初始状态为Q 0=Q 1=0。

参考答案:由图可写出两个D 触发器的特性方程D Q n =+10 (CP 上升沿到达时刻有效)nn n n n Q Q Q Q Q 101011+=+=nQ 0 (CP 下降沿到达时刻有效)由上述两个特性方程可知,这两个触发器都为D 触发器,根据边沿D 触发器的功能可画出图所示的输出Q 0和Q 1端的波形图。

24.(9-3难)图示是用反馈同步置数法构成的N 进制计数器,是多少进制?参考答案:置入的数是0011,一直计数到1001,然后反馈到置数端,从0011重新计数,0011,0100,0101,0110,0111,1000,1001,一共7种状态,故为七进制。

25. (9-3难)图示是用反馈同步置数法构成的N 进制计数器,是多少进制?参考答案:置入的数是0011,一直计数到1010,然后反馈到置数端,从0011重新计数,0011,0100,0101,0110,0111,1000,1001,1010,一共8种状态,故为八进制。

26.(9-3中)写出T 触发器的特征方程,并列出其特性表。

参考答案:特性方程:1n n n Q TQ TQ +=+ 特性表:T 1n Q +功能 0 Qn保持 1nQ翻转27.(9-1中)试用D 触发器转换成T 触发器,并画出电路图。

参考答案:D 触发器特性方程为1n QD +=,T 触发器特性方程为1n n n Q TQ TQ +=+,比较两式,令n n D TQ TQ =+,可将D 触发器转换成T 触发器。

电路图为:五.计算题1.(9-1难)试分析图所示的时序电路 1).写出驱动方程 2).写出状态方程 3).列出状态转换表 4).画出状态转换图 5).说明其逻辑功能参考答案: 1).驱动方程:J 0=n1Q ,K 0=1; 2).状态方程:Q 0n+1=n1Q n0QJ 1=Q 0n ,K 1=1; Q 1n+1=n1Q Q 0n3).状态转换表:Q 1n Q 0n Q 1n+1 Q 0n+1 0 0 0 1 0 1 1 0 1 0 0 0 114).状态转换图:5).逻辑功能:能自启动的同步三进制加法计数器2.(9-3难)74LS163是4位二进制同步计数器(同步清零),试分析图示电路是几进制计数器。

参考答案:DCBA=0101,开始计数后,0101,0110,0111,1000,1001,1010,1011,1100,此时反馈置数,回到0101,8种状态,故为8进制。

3.(9-3难)74LS163是4位二进制同步计数器(同步清零),试分析图示电路是几进制计数器。

参考答案:DCBA=1011,开始计数后,1011,1100,1101,1110,1111,此时反馈置数,回到1011,5种状态,故为5进制。

4.(9-3中)74LS161是同步二进制计数器,异步反馈清零。

试回答下面的计数器构成了几进制?1).2).参考答案:1).DCBA=0000,开始计数后,一直计数到1100,反馈异步清零回到0000,12种状态,故为12进制。

2). DCBA=0000,开始计数后,一直计数到0110,反馈异步清零回到0000,6种状态,故为6进制。