用波形图法分析时序逻辑电路

- 格式:docx

- 大小:38.37 KB

- 文档页数:6

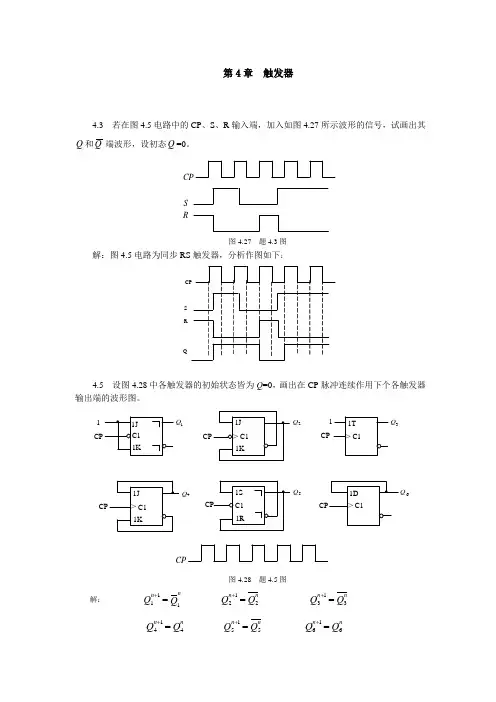

第4章 触发器4.3 若在图4.5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其Q 和Q 端波形,设初态Q =0。

SRCP图4.27 题4.3图解:图4.5电路为同步RS 触发器,分析作图如下:S RQ4.5 设图4.28中各触发器的初始状态皆为Q =0,画出在CP 脉冲连续作用下个各触发器输出端的波形图。

Q 11CPQ 3CPCPQ 2Q 6Q 4Q 5CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+ Q Q n n 515=+ Q Q nn 616=+Q 1CP Q 2Q 3Q 4Q 5Q64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1A BCP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

Y(b )(c )CPQ 1Q 2(a )图4.30 题4.7图解: (a )Q Q nn 211=+ QQ nn 112=+ Q F 1CP ⊕= R 2 = Q 1 低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y nn43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

描述时序逻辑电路的方法时序逻辑电路是数字电路中的一种重要类型,它能够根据输入信号的时序关系产生特定的输出序列。

本文将介绍描述时序逻辑电路的方法。

一、引言时序逻辑电路是由时钟信号驱动的,它对输入信号的变化时间进行检测,并根据时钟信号的边沿触发产生相应的输出。

这种电路常用于计数器、状态机等应用中,可以实现各种复杂的功能。

二、状态图描述法状态图是描述时序逻辑电路工作过程的一种图形化表示方法。

它由状态和状态之间的转移组成,每个状态表示电路的某种特定状态,而状态之间的转移表示电路在不同状态之间的切换。

三、状态表描述法状态表是描述时序逻辑电路工作过程的一种表格形式。

它列出了电路的所有状态及其对应的输入和输出情况,可以清晰地表示电路的功能逻辑。

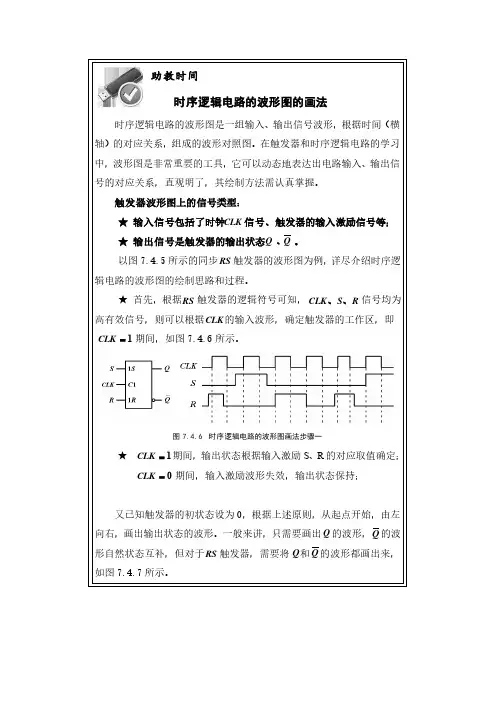

四、波形图描述法波形图是描述时序逻辑电路输入输出信号随时间变化的图形表示方法。

通过绘制输入输出信号的波形图,可以直观地观察和分析电路的工作过程。

五、RTL描述法RTL(Register Transfer Level)是一种描述时序逻辑电路的硬件描述语言。

它通过使用寄存器之间的数据传输来描述电路的功能和逻辑,可以方便地进行电路的仿真和综合。

六、Verilog描述法Verilog是一种用于描述数字系统的硬件描述语言,也可以用来描述时序逻辑电路。

通过使用Verilog语言,可以方便地进行电路的设计、仿真和验证。

七、状态方程描述法状态方程是描述时序逻辑电路状态转移关系的一种数学表达式。

它由当前状态、输入和下一个状态之间的逻辑关系组成,可以通过布尔代数等方法进行分析和求解。

八、流程图描述法流程图是描述时序逻辑电路工作过程的一种图形化表示方法。

它由各个状态和状态之间的转移组成,可以清晰地表示电路的运行流程。

九、状态机描述法状态机是描述时序逻辑电路工作过程的一种数学模型。

它由状态、输入、输出和状态转移函数组成,可以用来描述电路的功能和逻辑。

十、总结时序逻辑电路是数字电路中一种重要类型,它能够根据输入信号的时序关系产生特定的输出序列。

时序逻辑电路的分析方法1.时序图分析时序图是描述时序逻辑电路中不同信号随时间变化的图形表示。

时序图分析方法是通过绘制输入输出信号随时间变化的波形图,来观察信号之间的时序关系。

时序图分析的步骤如下:1)根据电路的逻辑功能,确定所需的时钟信号和输入信号。

2)根据电路的逻辑关系,建立出波形图的坐标系,确定时间轴和信号轴。

3)按照时钟信号的不同变化情况(上升沿、下降沿),在波形图中绘制相应的路径。

4)观察各个信号之间的时序关系,分析电路的逻辑功能和输出结果。

时序图分析方法的优点是直观、简单,可以清楚地显示信号的时序关系。

但它对于复杂的电路设计来说,图形绘制和分析过程相对繁琐,需要一定的经验和技巧。

2.状态表分析状态表分析方法是通过定义不同输入信号下的状态转移关系,来描述时序逻辑电路的行为。

状态表可以用表格的形式表示,其中包含了输入信号、当前状态、下一个状态和输出信号等信息。

状态表分析的步骤如下:1)根据电路的逻辑功能和输入信号,列出电路的状态转移关系。

2)构建状态表,定义不同输入信号下的状态转移关系和输出信号。

3)根据状态表,逐步推导出电路的状态转移路径和输出结果。

状态表分析方法的优点是逻辑严谨、结构清晰,适用于对于复杂的状态转移关系进行分析和设计。

但它对于大规模的电路设计来说,状态表会非常庞大,而且容易出现错误,需要仔细的计算和推导。

3.状态图分析状态图分析方法是通过绘制状态转移图,来描述时序逻辑电路中状态之间的转移关系。

状态图是由状态、输入信号、输出信号和状态转移路径等构成。

状态图分析的步骤如下:1)根据电路的逻辑功能和输入信号,确定电路的状态和状态转移关系。

2)构建状态图,按照状态的转移路径和输入信号绘制状态图。

3)根据状态图,分析电路的逻辑功能和输出结果。

状态图分析方法的优点是直观、清晰,可以清楚地描述状态之间的转移关系。

它可以帮助设计者对于电路的状态转移关系进行分析和调试。

但状态图也会随着电路规模的增大而变得复杂,需要仔细分析和理解。

实验三时序逻辑电路学习目标:1、掌握时序逻辑电路的一般设计过程2、掌握时序逻辑电路的时延分析方法,了解时序电路对时钟信号相关参数的基本要求3、掌握时序逻辑电路的基本调试方法4、熟练使用示波器和逻辑分析仪观察波形图实验内容:1、广告流水灯(第9 周课内验收)用触发器、组合函数器件和门电路设计一个广告流水灯,该流水灯由8 个LED 组成,工作时始终为1 暗7 亮,且这一个暗灯循环右移。

(1) 写出设计过程,画出设计的逻辑电路图,按图搭接电路(2) 将单脉冲加到系统时钟端,静态验证实验电路(3) 将TTL 连续脉冲信号加到系统时钟端,用示波器观察并记录时钟脉冲CP、触发器的输出端Q2、Q1、Q0 和8 个LED 上的波形。

2、序列发生器(第10 周课内实物验收计数器方案)分别用MSI 计数器和移位寄存器设计一个具有自启动功能的01011 序列信号发生器(1) 写出设计过程,画出电路逻辑图(2) 搭接电路,并用单脉冲静态验证实验结果(3) 加入TTL 连续脉冲,用示波器观察观察并记录时钟脉冲CLK、序列输出端的波形。

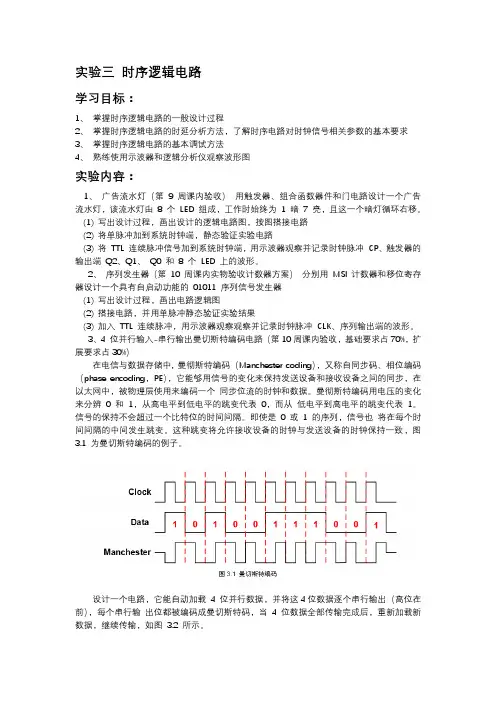

3、4 位并行输入-串行输出曼切斯特编码电路(第10周课内验收,基础要求占70%,扩展要求占30%)在电信与数据存储中, 曼彻斯特编码(Manchester coding),又称自同步码、相位编码(phase encoding,PE),它能够用信号的变化来保持发送设备和接收设备之间的同步,在以太网中,被物理层使用来编码一个同步位流的时钟和数据。

曼彻斯特编码用电压的变化来分辨0 和1,从高电平到低电平的跳变代表0,而从低电平到高电平的跳变代表1。

信号的保持不会超过一个比特位的时间间隔。

即使是0 或1 的序列,信号也将在每个时间间隔的中间发生跳变。

这种跳变将允许接收设备的时钟与发送设备的时钟保持一致,图3.1 为曼切斯特编码的例子。

设计一个电路,它能自动加载4 位并行数据,并将这4位数据逐个串行输出(高位在前),每个串行输出位都被编码成曼切斯特码,当4 位数据全部传输完成后,重新加载新数据,继续传输,如图3.2 所示。

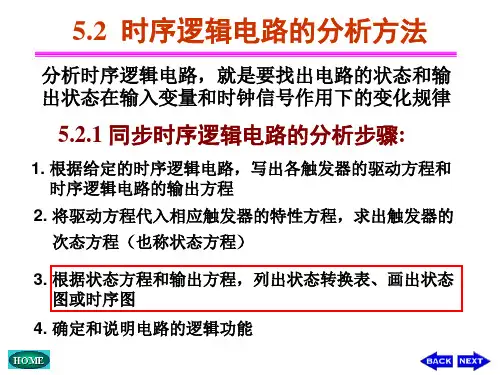

第7章 时序逻辑电路7.1 概述时序电路在任何时刻的稳定输出,不仅与该时刻的输入信号有关,而且还与电路原来的状态有关。

图7.1.1 时序逻辑电路的结构框图2、时序电路的分类 (1) 根据时钟分类同步时序电路中,各个触发器的时钟脉冲相同,即电路中有一个统一的时钟脉冲,每来一个时钟脉冲,电路的状态只改变一次。

异步时序电路中,各个触发器的时钟脉冲不同,即电路中没有统一的时钟脉冲来控制电路状态的变化,电路状态改变时,电路中要更新状态的触发器的翻转有先有后,是异步进行的。

(2)根据输出分类米利型时序电路的输出不仅与现态有关,而且还决定于电路当前的输入。

穆尔型时序电路的其输出仅决定于电路的现态,与电路当前的输入无关;或者根本就不存在独立设置的输出,而以电路的状态直接作为输出。

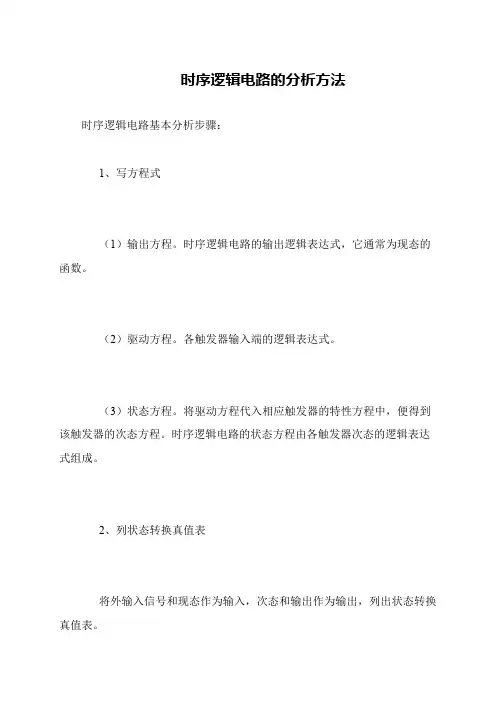

7.2 时序逻辑电路的分析方法时序电路的分析步骤:电路图 时钟方程、输出方程、驱动方程 状态方程 计算 状态表(状态图、时序图) 判断电路逻辑功能 分析电路能否自启动。

7.2.1 同步时序电路的分析方法 分析举例:[例7.2.1]7.2.2 异步时序电路的分析方法 分析举例:[例7.2.3] 7.3 计数器概念:在数字电路中,能够记忆输入脉冲CP 个数的电路称为计数器。

计数器累计输入脉冲的最大数目称为计数器的“模”,用M 表示。

计数器的“模”实际上为电路的有效状态。

计数器的应用:计数、定时、分频及进行数字运算等。

计数器的分类:(1)按计数器中触发器翻转是否同步分:异步计数器、同步计数器。

(2)按计数进制分:二进制计数器、十进制计数器、N 进制计数器。

(3)按计数增减分:加法计数器、减法计数器、加/减法计数器。

7.3.1 异步计数器X X Y 1Y m输入输出一、异步二进制计数器1、异步二进制加法计数器分析图7.3.1 由JK触发器组成的4位异步二进制加法计数器。

分析方法:由逻辑图到波形图(所有JK触发器均构成为T/触发器的形式,且后一级触发器的时钟脉冲是前一级触发器的输出Q),再由波形图到状态表,进而分析出其逻辑功能。

解:分析习题4.3图(a )所示的锁存器逻辑图,当锁存命令CP =1,输入信号D 被封锁,锁存器的输出状态保持不变;当锁存命令CP =0,锁存器输出D Q =,Q=D ;当锁存命令CP 出现上升沿,输入信号D 被封锁。

根据上述分析,画出锁存器输出Q 及Q 的波形如习题4.3图(c )所示。

习题4.4 习题图4.4是作用于某主从JK 触发器CP 、J 、K 、R D 及S D 端的信号波形图,试绘出Q 端的波形图。

解:主从JK 触发器的R D 、S D 端为异步清零和复位端,且为低有效。

只有当1==D D S R 时,在CP 下降沿的作用下,J 、K 决定输出Q 状态的变化。

Q 端的波形如习题4.4图所示。

习题4.5 习题4.5图(a )是由一个主从JK 触发器及三个非门构成的“冲息电路”, 习题4.5图(b )是时钟CP 的波形,假定触发器及各个门的平均延迟时间都是10ns ,试绘出输出F 的波形。

解:由习题4.5图(a )所示的电路连接可知:1D ===K J S ,F R =D 。

当1D =R 时,在CP 下降沿的作用下,且经过10 ns ,状态Q 发生翻转,再经过30ns ,F 发生状态的改变,Q F =。

0D =R 时,经过10ns ,状态Q =0。

根据上述对电路功能的分析,得到Q 和F 的波形如习题4.5图(c )所示。

习题4.6 习题4.6图(a )是一个1检出电路,图(b )是CP 及J 端的输入波形图,试绘出R D 端及Q 端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意CP =1时主触发器的存储作用)。

解:分析习题4.6图(a )的电路连接:Q CP R K S ⋅===D D ,0,1;分段分析习题习题4.6图(a )(b )CP J(c )CP JQR D(a )(b ) 100nsCP习题4.5图10ns100nsCPQF(c )F 10ns30ns30ns4.6图(b )所示CP 及J 端信号波形。

用波形图法分析时序逻辑电路

摘要:时序逻辑电路在现代电子工程中扮演着重要的角色,它由一组基本电子元件构成,可以存储、处理和传输信号。

本文通过波形图法来分析时序逻辑电路的工作原理和时序行为,详细介绍了时序逻辑电路设计中的一些关键问题,如时钟信号的生成、时序运算的实现、状态转移的控制等。

通过实验结果的分析,本文证明了波形图法在分析时序逻辑电路中的有效性和应用价值。

关键词:时序逻辑电路,波形图,时钟信号,状态转移,应用价值。

正文:

一、时序逻辑电路的概述

时序逻辑电路是指电子系统中的一类电路,其功能是在一定的时序条件下进行信号的存储、处理和传输,实现特定的系统任务。

时序逻辑电路主要由触发器、计数器、状态机等基本电子元件构成。

二、波形图法的原理和应用

波形图法是一种图形化的分析方法,它可以直观地表示出时序逻辑电路中信号的变化规律。

波形图法的基本原理是将时序信号波形按时间轴排列,并用线段连接各个波形点,形成一个连续的曲线。

在分析时序逻辑电路时,波形图法可以用来研究电路的工作原理、时序行为和时序参数等。

通过合理的波形图设计和分析,可以有效地发现和排除时序逻辑电路中的故障和问题,提高电路的可靠性和稳定性。

三、时序逻辑电路设计中的重点问题

在时序逻辑电路的设计和实现中,存在一些重点问题需要特别关注。

例如,时钟信号的生成和稳定性、时序运算的实现以及状态转移的控制等。

时钟信号的生成:时钟信号是时序逻辑电路中的重要信号之一,它用来同步电路各个部件的工作,保证电路的正确性和可靠性。

时钟信号的生成可以通过基本的RC振荡电路或者晶体振荡器

实现。

时序运算的实现:时序逻辑电路中的时序运算是指通过各种基本电子元件实现时序信号的比较、计数、累加、判断等运算,以完成特定的系统任务。

时序运算的实现需要进行电路的精确设计和匹配,以保证电路的正确性。

状态转移的控制:时序逻辑电路在处理信号时需要进行状态转移,状态转移可以通过各种方法实现,例如使用计数器、状态机等。

状态转移的控制需要根据电路的具体需求进行设计,以满足各种复杂的逻辑运算。

四、实验结果分析

通过实验得到的波形图数据,可以对时序逻辑电路的工作特性进行分析和评估。

根据实验结果可以发现,时序逻辑电路的波形图数据与设计预期相符,证明了时序逻辑电路的功能和可靠性。

总之,波形图法是一种有效的分析时序逻辑电路的工具,可以用来研究电路的时序行为、时序参数等问题,为时序逻辑电路的设计和实现提供重要的支持和帮助。

五、时序逻辑电路的应用场景

时序逻辑电路在现代电子工程中应用广泛,常常用于时序处理、数据存储、计数和计时等方面。

下面列举几个常见的应用场景:

1、时序控制器:时序控制器是一个用于控制复杂系统时序运

算的电路,它通常使用状态机来实现。

时序控制器通常用于控制电子设备的输入和输出、通信协议的实现等。

2、计时器:计时器是一种专门用于测量时间的电路,它可以

通过计数器、外部时钟等方式实现。

计时器广泛应用于各种心率计、秒表、定时器等计时设备中。

3、存储器:存储器是一种用于存储二进制信息的电路,包括

静态存储器和动态存储器。

存储器广泛应用于各种计算机和通信系统中。

4、序列检测器:序列检测器是一种专门用于检测序列重复性

的电路,通常使用状态机或计数器来实现。

序列检测器广泛应

用于通信系统、加密算法等领域。

5、控制器:控制器是一个用于控制系统各个部分工作的电路,包括闭环控制器和开环控制器。

控制器广泛应用于各种机械、电子系统中,例如机器人、自动化生产线等。

六、波形图法在时序逻辑电路分析中的优势

波形图法是一种直观、方便、易于理解的分析方法,具有以下优势:

1、清晰表达时序信号的变化规律,方便对电路的工作特性进

行分析和评估。

2、可以发现电路中存在的故障和问题,帮助进行及时排除和

修复。

3、减少了电路测试的时间和成本,提高了电路测试的效率和

精度。

4、波形图法可以与仿真仿真软件相结合,实现更加精确的模

拟和分析。

七、结论

时序逻辑电路是现代电子工程中不可或缺的一部分,它在各种电子系统中发挥着重要的作用。

波形图法是一种有效的分析时序逻辑电路的方法,可以用来研究电路的工作原理、时序行为

和时序参数等问题。

通过实验结果的分析,本文证明了波形图法在分析时序逻辑电路中的有效性和应用价值。

此外,时序逻辑电路的应用已经渗透到我们的日常生活中。

例如,计时器可以用于厨房的计时器、运动员的秒表等场景;存储器也被广泛应用于我们的电子产品中,例如手机、电脑等。

时序逻辑电路的应用还包括通信系统、汽车控制、航空航天、军事设备等高科技领域。

在这些领域,时序逻辑电路的性能要求通常更高,因此对时序逻辑电路的设计和测试也更为严格。

对于时序逻辑电路的设计和测试,波形图法作为一种主要的分析方法,可以帮助工程师快速发现潜在的问题,提高工程开发的效率和准确性。

除了波形图法,时序逻辑电路还可以通过时序仿真、软件模拟等方式进行分析和测试。

时序仿真是一种通过计算机模拟电路行为的方法,可以帮助工程师更加精确地分析电路的行为和特性。

软件模拟则是通过模拟软件和相关的模型来模拟电路的行为和特性,可以在更短的时间内完成电路的测试和分析,降低开发成本和风险。

总之,时序逻辑电路作为现代电子工程的重要组成部分,其应用范围广泛且日益增长。

波形图法作为一种直观、方便的分析方法,可以帮助工程师快速发现问题和优化电路性能。

随着电子技术的不断发展和创新,时序逻辑电路的设计和测试也将面临更多挑战和机遇。

时序逻辑电路是现代电子工程的重要组成部分,被广泛应用于计时器、存储器、通信系统、汽车控制、航空航天、军事设备等领域。

时序逻辑电路的设计和测试具有重要意义,波形图法是一种主要的分析方法,可帮助工程师快速发现潜在问题,提高工程开发的效率和准确性。

时序仿真和

软件模拟是另外两种常用的测试方法。

随着电子技术的不断发展和创新,时序逻辑电路的设计和测试也将面临更多挑战和机遇。