03集成电路版图基础-CMOS版图

- 格式:ppt

- 大小:8.44 MB

- 文档页数:59

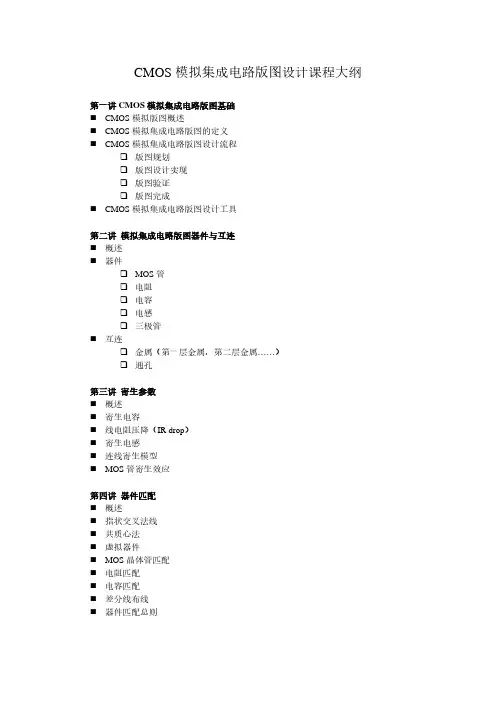

CMOS模拟集成电路版图设计课程大纲第一讲CMOS模拟集成电路版图基础⏹CMOS模拟版图概述⏹CMOS模拟集成电路版图的定义⏹CMOS模拟集成电路版图设计流程❑版图规划❑版图设计实现❑版图验证❑版图完成⏹CMOS模拟集成电路版图设计工具第二讲模拟集成电路版图器件与互连⏹概述⏹器件❑MOS管❑电阻❑电容❑电感❑三极管⏹互连❑金属(第一层金属,第二层金属……)❑通孔第三讲寄生参数⏹概述⏹寄生电容⏹线电阻压降(IR drop)⏹寄生电感⏹连线寄生模型⏹MOS管寄生效应第四讲器件匹配⏹概述⏹指状交叉法线⏹共质心法⏹虚拟器件⏹MOS晶体管匹配⏹电阻匹配⏹电容匹配⏹差分线布线⏹器件匹配总则第五讲设计规则⏹概述⏹工艺库中各类器件的层信息⏹设计规则细则⏹工业标准的基本数据格式第六讲验证⏹设计规则检查(DRC)Design Rule Check⏹版图与电路图的对照(LVS)Layout Versus Schematic⏹电气规则检查(ERC)Electrical Rule Check⏹天线规则检查(ANT)⏹静电放电检查(ESD)第七讲可靠性设计⏹天线效应⏹闩锁效应⏹静电放电保护(Electro-Static Discharge ,ESD)⏹数模混合集成电路版图设计第八讲工艺设计工具包(PDK)⏹ 1.PDK名称的涵义⏹ 2.PDK中包含的内容● 2.1 IO lib2.1.1 GDS文件的导入操作2.1.2 网表导入2.1.3 IO使用文档介绍● 2.2 SMIC_13_PDK_v2.6_20142.2.1 Smic13mmrf_1233文件夹2.2.2 model 文件夹2.2.3 Calibre 文件夹● 2.3 SMIC_13_TF_LG_LIST_2014122.3.1 Standard cell Timing lib2.3.2 Calview.cellmap2.3.3 Standard cell netlist及网表导入操作2.3.4 Ant rule (天线规则)第九讲Cadence spectre概述与操作界面⏹Cadence spectre 概述⏹Cadence spectre的特点⏹Cadence spectre的仿真设计方法⏹Cadence spectre与其他EDA软件的连接⏹Cadence spectre的基本操作第十讲Spectre窗口和库元件⏹模拟设计环境(Analog Design Environment)⏹波形显示窗口(Waveform)⏹波形计算器(Waveform Calculator)⏹Spectre库中的基本器件第十讲Cadence Virtuoso版图设计工具⏹Cadence Virtuoso概述⏹Virtuoso 界面介绍⏹Virtuoso 基本操作第十一讲Mentor Calibre版图验证工具⏹Mentor Calibre版图验证工具概述⏹Mentor Calibre版图验证工具调用⏹Mentor Calibre DRC验证⏹Mentor Calibre LVS验证⏹Mentor Calibre寄生参数提取(PEX)第十二讲版图设计与验证流程实例⏹设计环境准备⏹反相器链电路的建立和前仿真⏹反相器链版图设计⏹反相器链版图验证与参数提取⏹反相器链电路后仿真⏹输入输出单元环设计⏹主体电路版图与输入输出单元环的连接⏹导出GDSII文件。

集成电路版图与⼯艺课程设计之⽤CMOS实现Y=AB+C电路与版图1 绪论1.1 设计背景集成电路设计(Integrated circuit design, IC design),亦可称之为超⼤规模集成电路设计(VLSI design),是指以集成电路、超⼤规模集成电路为⽬标的设计流程。

集成电路设计涉及对电⼦器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的建⽴。

所有的器件和互连线都需安置在⼀块半导体衬底材料之上,这些组件通过半导体器件制造⼯艺(例如光刻等)安置在单⼀的硅衬底上,从⽽形成电路。

近些年来,集成电路技术发展迅猛,促使半导体技术不断地发展,半导体技术正在进⼊将整个系统整合在单⼀晶⽚上的时代。

故对VLSI的版图设计的要求也越来越⾼。

Tanner软件可提供完整的集成电路设计环境,帮助初学者进⼊VLSI设计领域。

本设计采⽤Tanner Tools Pro ⼯具,对逻辑为Y=AB+C进⾏电路设计与仿真、版图设计与仿真,在报告中给出电路图、版图与仿真结果。

1.2 设计⽬标设计⽬标逻辑:Y=AB+C⽤CMOS⼯艺设计逻辑为Y=AB+C的电路和版图。

因为CMOS是天然的反逻辑输出,所以需要先设计出逻辑为/Y=/(AB+C)的电路,再将输出接⼊⼀个CMOS反相器实现逻辑功能。

设计电路图(Schematic)时,N⽹络A与B串联且与C并联,P⽹络A与B并联且与C串联,在N和P⽹络的交界节点接⼊反相器后引出输出Y。

设计版图(Layout)时,在P型衬底(P-Sub)上进⾏制作,所以N-MOS管可以直接掺杂制作,⽽P-MOS管需要先制作⼀个N阱(N-Well),并在N阱⾥制作P-MOS管。

整个设计⽐较简单,仅仅使⽤单层⾦属布线(Meteal)。

导出电路和版图⽹表(spice)⽂件,⽤Tspice软件进⾏仿真波形,分析电路和版图是否设计正确性以及其性能如何。

在LVS验证中匹配电路原理图和版图逻辑和尺⼨匹配性,完成整个设计过程。