IC版图设计基础

- 格式:pdf

- 大小:158.42 KB

- 文档页数:5

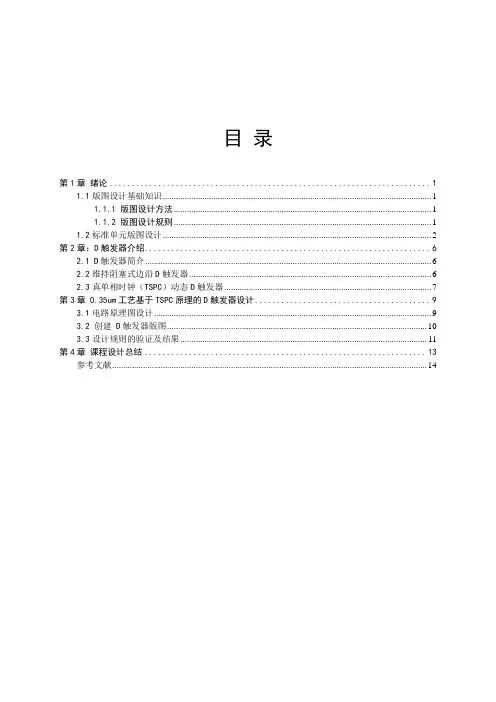

目录第1章绪论 (1)1.1版图设计基础知识 (1)1.1.1 版图设计方法 (1)1.1.2 版图设计规则 (1)1.2标准单元版图设计 (2)第2章:D触发器介绍 (6)2.1 D触发器简介 (6)2.2维持阻塞式边沿D触发器 (6)2.3真单相时钟(TSPC)动态D触发器 (7)第3章 0.35um工艺基于TSPC原理的D触发器设计 (9)3.1电路原理图设计 (9)3.2 创建 D触发器版图 (10)3.3设计规则的验证及结果 (11)第4章课程设计总结 (13)参考文献 (14)第1章绪论1.1版图设计基础知识集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。

单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。

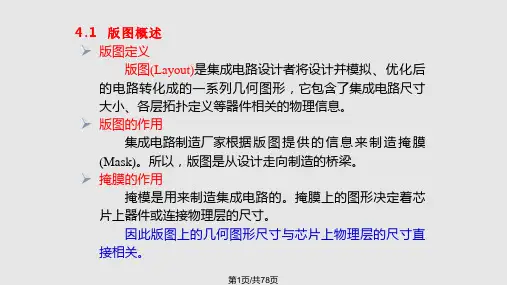

在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。

他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形。

对于复杂的版图设计,一般把版图设计分成若干个子步骤进行:划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。

版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。

布线完成模块间的互连,并进一步优化布线结果。

压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。

1.1.1 版图设计方法可以从不同角度对版图设计方法进行分类。

如果按设计自动化程度来分,可将版图设计方法分成手工设计和自动设计2大类。

如果按照对布局布线位置的限制和布局模块的限制来分,则可把设计方法分成全定制(fullcustom)和半定制(semicustom)2大类。

而对于全定制设计模式,目前有3种CAD工具服务于他:几何图形的交互图形编辑、符号法和积木块自动布图。

对于两极运算放大器版图设计的例子,采用的是Tanner公司的LEdit软件。

这是一种广泛使用在微机上的交互图形编辑器。

芯片版图设计芯片版图设计是芯片设计的核心环节,它是将芯片电路设计文件转化为实际可以被制造的芯片版图的过程。

芯片版图设计涉及到电路布局、布线规则、功耗和信号完整性等方面,对芯片性能和可靠性有重要影响。

本文将介绍芯片版图设计的主要内容和流程。

芯片版图设计的主要内容包括电路网表、物理布局、电路布局、布线规则和接口电路设计等。

电路网表是芯片设计的基础,它描述了芯片中各个元件之间的互连关系。

物理布局是将电路网表中的元件在芯片上的具体物理位置确定下来,它考虑了元件之间的相对位置和布局约束。

电路布局是在物理布局的基础上对各个元件的电路连接进行布局,它考虑了信号的传输和电路的功耗。

布线规则是指芯片上各个元件之间的电路布线时需要满足的约束条件,它包括布线层次、电源与地的布线和电路阻抗的控制等。

接口电路设计是指芯片与外部系统之间的数据传输和信号处理的设计,它包括输入输出接口、时钟和复位电路的设计。

芯片版图设计的流程一般包括以下几个步骤。

首先是电路网表的生成,可以通过芯片设计软件自动生成,也可以手动编辑。

然后是物理布局的确定,根据芯片的规格和性能目标,确定各个元件的布局和位置。

接着是电路布局的设计,包括电路连接的布局和信号线的长度控制。

布线规则的制定是在芯片布局的基础上进行的,根据芯片的制造工艺和布线层次的限制,确定布线规则的相关参数。

接口电路的设计是芯片版图设计的最后一个环节,通过设计输入输出接口、时钟和复位电路等,确保芯片与外部系统的正常通信和工作。

芯片版图设计需要充分考虑芯片规格和性能要求,同时也要考虑制造工艺和布线层次的限制。

在设计过程中,需要进行电路模拟和仿真,确保电路的正确性和可靠性。

此外,布局和布线的优化也是芯片版图设计的关键,可以通过布线层次的合理划分、电源和地的布局和导引线的优化等手段,提高芯片的性能和可靠性。

综上所述,芯片版图设计是芯片设计中不可或缺的环节,它直接影响芯片的性能和可靠性。

芯片版图设计的内容包括电路网表、物理布局、电路布局、布线规则和接口电路设计等。

IC版图设计面试知识本文将为大家介绍IC版图设计面试中常见的知识点,包括布局与布线、时序与时钟、功耗与噪声等方面的内容。

通过对这些知识点的了解,可以帮助大家在IC版图设计面试中获得更好的表现。

一、布局与布线1. 布局布局是IC设计的第一步,它决定了各个功能模块在芯片上的位置和相互之间的布局关系。

在IC版图设计面试中,常见的布局问题包括:•功能模块的划分和组织方式•布局规则的遵守(如间距、阻抗匹配等)•对电源和地线的布局2. 布线布线是将各个功能模块之间的信号线连接起来的过程。

在IC版图设计面试中,常见的布线问题包括:•信号线的走向和路径规划•时钟线的布线•路由规则的遵守(如最小线宽、最小间距等)二、时序与时钟1. 时序时序是指IC芯片中各个时钟和数据信号之间的时间关系。

在IC版图设计面试中,常见的时序问题包括:•各个时钟域之间的同步问题•时序约束的制定和满足•时序的正确性验证方法2. 时钟时钟是IC芯片中起到供给同步时序的信号源。

在IC版图设计面试中,常见的时钟问题包括:•时钟树设计与布线•时钟偏移和时钟抖动的控制•时钟功耗和噪声的优化三、功耗与噪声1. 功耗功耗是IC芯片在工作过程中所消耗的电能。

在IC版图设计面试中,常见的功耗问题包括:•功耗优化的方法和策略•功耗的估算和计算•功耗的控制和管理2. 噪声噪声是IC芯片中由于电信号传输和耦合引起的干扰信号。

在IC版图设计面试中,常见的噪声问题包括:•噪声源的定位和分析•噪声的模拟和仿真•噪声的抑制和消除结语本文对IC版图设计面试中常见的知识点进行了简要介绍,包括布局与布线、时序与时钟、功耗与噪声等方面的内容。

希望通过这些知识点的了解,可以帮助大家在IC版图设计面试中更好地展示自己的能力和水平。

IC设计基本知识IC设计(Integrated Circuit Design)是指利用半导体工艺将电子器件集成在一块硅片上,并通过设计和布局进行电路的实现和优化的过程。

IC设计是电子工程领域的关键技术之一,也是现代电子设备发展和电子产业升级的重要基础。

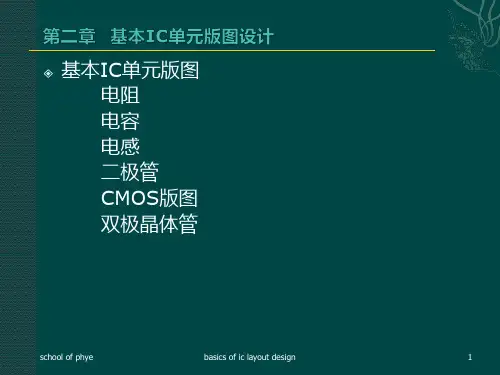

IC设计的基本知识可以分为以下几个方面:1.电子器件基础知识:了解各种电子器件的基本工作原理和特性是进行IC设计的基础。

例如,了解二极管、晶体管、场效应管等器件的结构、原理和参数。

2. 数字电路设计:数字电路设计是IC设计的重要部分。

了解数字电路的设计原理、逻辑门电路、时序电路、状态机等基本概念和设计方法是必要的。

另外,还需要熟悉可编程器件如FPGA(Field Programmable Gate Array)的原理和应用。

3.模拟电路设计:模拟电路设计是IC设计中的另一个重要部分。

了解模拟电路的设计原理、放大器、滤波器、振荡器等基本电路的设计方法是必要的。

同时,需要了解一些基本的模拟电路设计工具和方法。

4.射频电路设计:射频电路设计是IC设计中的一个特殊领域,用于实现无线通信和射频前端。

了解射频电路的基本原理、调制解调、射频放大器、滤波器等相关概念和设计方法是必要的。

5.数字信号处理:数字信号处理(DSP)是IC设计中的另一个重要方向。

了解数字信号处理的基本原理、滤波器设计、傅里叶变换等概念是必要的。

6.IC制造工艺:了解IC制造工艺是进行IC设计的基本要求之一、了解硅片制造的工艺流程、光刻技术、薄膜沉积、蚀刻等过程是必要的。

7.版图设计:版图设计是实现IC电路的物理布局和连接。

了解版图设计的基本规则、布线技巧、电路布局等是进行IC设计的必备知识。

8.仿真和验证:进行IC设计时,需要进行电路仿真和验证。

了解电路仿真软件如SPICE的基本原理和使用方法,熟悉验证电路设计的方法是必要的。

9.芯片测试和封装:了解芯片测试和封装技术也是进行IC设计的重要环节之一、了解如何进行芯片测试和封装设计,以满足产品质量和可靠性的要求是必要的。

2016年3月7日IC版图设计基础课后作业

孙一川2013141223053 我在自己的电脑上安装了虚拟机,从实验室把红帽Linux IC拷回来在寝室完成这一个课堂作业。

前面运行Linux创建file等日常步骤就不一一累述。

直接进入正题。

首先看了PDF过后,知道最终目的是完成一个nmos,根据PDF上提供尺寸,先要计算出ndiff的长宽,由于是对称结构,所以长度可以计算一边的在乘二就行,一边的长度是contact的长度加上两个它到niff的距离的是

0.6u+0.9u+0.9u=2.4u,总长度便是4.8u。

宽度是device width告诉了是

3.6u。

先按照这个尺寸画出标尺。

Linux系统必须要做完一部就要按esc来清

除掉之前的功能在去进行接下来的操作,所以要先按esc清除掉标尺操作在按rectangle选中diff-drw依照着之前画好的标尺来画出ndiff。

如图:

接下来我们要花poly,这不分要用到path,path有自动适应标尺的功

能,一句PDF给出的poly的场是0.6u宽是4.8u。

所以先依照着的poly的宽

画出标尺,在按esc后选中poly-drw,按快捷键p,从上往下拉,与之前不同

的是,这次画的是线,双击后会适应你的标尺来生成poly。

如图:

接下来是要在ndiff上画出metal,这一部分可以看做将ndiff和poly这个左右对承德结构从中间分开,它离ndiff每条边的距离都是0.5u,所以他是一个长为1.4u宽为2.6u的矩形。

所以画好标尺过后这一部分很容易就画出来了。

如图:

画金属上的contact与画金属有异曲同工之处,因为contact到金属三条边的距离都是0.4u,contact本身是一个边长为0.6u的正方形。

有了上图所示画好的标尺这一部分就非常好画了。

最后如图所示:

然后按shift+k清除掉所有标尺就是最后的结果,之前忘了说,在前面shift+看这个快捷键消除标尺我已经用过好几次了。

最后完工的图片:。