逻辑学真值表课件.pptx

- 格式:pptx

- 大小:1.23 MB

- 文档页数:6

第一章命题逻辑,第一讲命题,逻辑联结词及真值表————————————————————————————————作者:————————————————————————————————日期:第一章命题逻辑第一讲命题、联结词及真值表命题的定义:命题是一个可以判断真假的陈述句。

一个命题要么是真,要么是假,具有唯一确定的真值。

如果是真,称该命题为真命题比如:太阳从东方升起1+2=3如果是假,称该命题为假命题比如:月球上有居民1>2判断是否是命题的两步:一、是否是陈述句二、是否有唯一的真值复合命题命题通过“非”、“或”、“且”、“如果……那么”等连词组成一个复合命题。

没有连词的称为简单命题。

上面提出的四个命题都是简单命题。

比如:1>2并且3>2我是中国人或者我是美国人如果你努力工作,就能有成就联结词及真值表这里主要介绍五个逻辑运算符 : ¬∧∨→↔¬:设p为命题,复合命题¬p表示“非p”(或“p的否定”),称为p的否定式。

¬称作否定联结词。

命题p与¬p的真值正好相反。

用真值表来表示他们的关系如下(真值表是一张反映命题真假的表格,T 表示真,F表示假)p¬pT FF T∧:设p,q是两个命题,复合命题p∧q表示“p并且q”(或“p与q”),称为p与q的合取式,∧称为合取联结词。

只有当p和q都为真的时候,该复合命题p∧q为真。

真值表:p q p∧qT T TT F FF T FF F F∨:设p,q是两个命题,复合命题p∨q表示“p或q”,称为p与q的析取式,∨称为析取联结词。

只要p和q中有一个为真,该复合命题p∨q为真。

真值表:p q p∨qT T TT F TF T TF F F→:设p,q是两个命题,复合命题p→q表示“如果p,则p”,称为p与q的蕴涵式,→称为蕴涵联结词。

只有当p真q假时,该复合命题p→q为假。

p →q的逻辑关系是:p是q的充分条件,q是p的必要条件。

真值表:p q p→qT T TT F FF T TF F T↔:设p,q是两个命题,复合命题p↔q表示“p当且仅当q”,称为p与q的等值式,↔称为等价联结词。

逻辑运算真值表

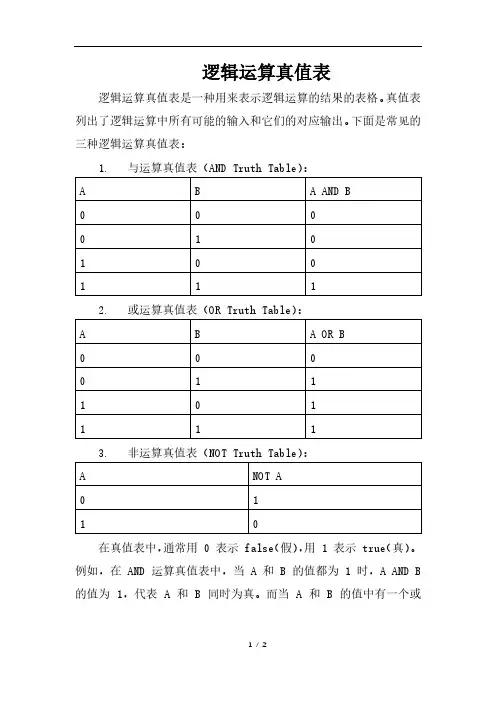

逻辑运算真值表是一种用来表示逻辑运算的结果的表格。

真值表列出了逻辑运算中所有可能的输入和它们的对应输出。

下面是常见的三种逻辑运算真值表:

1. 与运算真值表(AND Truth Table):

2. 或运算真值表(OR Truth Table):

3. 非运算真值表(NOT Truth Table):

在真值表中,通常用 0 表示 false(假),用 1 表示 true(真)。

例如,在 AND 运算真值表中,当 A 和 B 的值都为 1 时,A AND B 的值为 1,代表 A 和 B 同时为真。

而当 A 和 B 的值中有一个或

者两个都为 0 时,A AND B 的值为 0,代表 A 和 B 中有一个或两个都为假。

同样的道理,可以根据真值表来判断逻辑表达式的值。

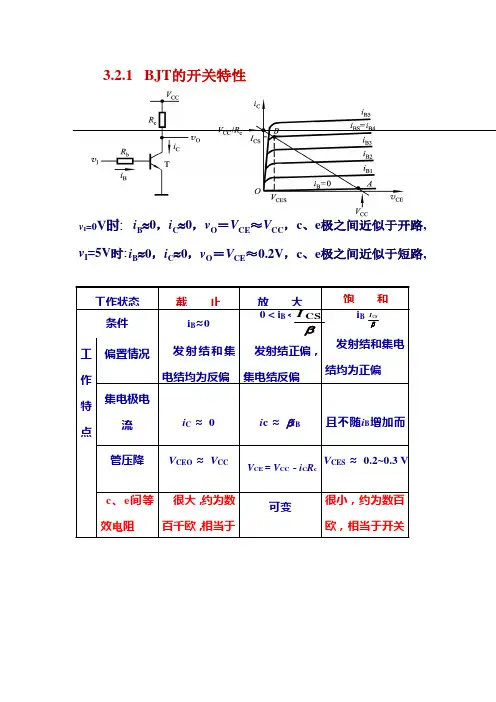

3.2.1 BJT

的开关特性

i B

≈0,i

C ≈0,v O =V CE ≈V CC ,c 、e 极之间近似于开路,

i B ≈0,i C ≈0,v O =V CE ≈0.2V ,c 、e 极之间近似于短路,

v I =5V 时:

v I =0V 时:

从截止到导通

开通 时间 t o n (= t d + t r )

从导通到截止

关闭时间 t o ff (= t s + t

f ) BJT 饱和与截止两种状态的相 互转换需要一定的时间才能完成。

C L 的充、放电过程均需经历一定

的时间,必然会增加输出电压

O

波 形的上升时间和下降时间,导致基 本的 B JT 反相器的开关速度不高。

若带电容负载

故需设计有较快开关速度的实用型 TTL 门电路。

逻辑真值表

2. 三态与非门(TSL )

当CS= 3.6V时

数据输入端

1

1

1

1

1

1

1

1

B

A

输出端L

CS 三态与非门真值表

饱和

截止

T4

低电平

截止截止

饱和

倒置工作

高电平

高电平

导通导通

截止

饱和

低电平

输出

D4

T3

T2

T1

输入

1

1

输出L

输入A

逻辑表达式

L = A。

3.2.1 BJT

的开关特性

i B

≈0,i

C ≈0,v O =V CE ≈V CC ,c 、e 极之间近似于开路,

i B ≈0,i C ≈0,v O =V CE ≈0.2V ,c 、e 极之间近似于短路,

v I =5V 时:

v I =0V 时:

从截止到导通

开通 时间 t o n (= t d + t r )

从导通到截止

关闭时间 t o ff (= t s + t

f ) BJT 饱和与截止两种状态的相 互转换需要一定的时间才能完成。

C L 的充、放电过程均需经历一定

的时间,必然会增加输出电压

O

波 形的上升时间和下降时间,导致基 本的 B JT 反相器的开关速度不高。

若带电容负载

故需设计有较快开关速度的实用型 TTL 门电路。

逻辑真值表

2. 三态与非门(TSL )

当CS= 3.6V时

数据输入端

1

1

1

1

1

1

1

1

B

A

输出端L

CS 三态与非门真值表

饱和

截止

T4

低电平

截止截止

饱和

倒置工作

高电平

高电平

导通导通

截止

饱和

低电平

输出

D4

T3

T2

T1

输入

1

1

输出L

输入A

逻辑表达式

L = A。