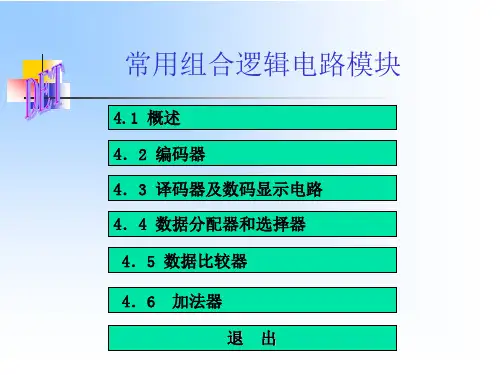

组合逻辑电路 常用组合逻辑电路

- 格式:pptx

- 大小:1.37 MB

- 文档页数:42

常用组合逻辑电路(3线—8线译码器 138)3线—8线译码器是一种常用的数字电路,用于将一个三位二进制数映射到八个输出信号上。

它通常被用作地址译码器,将CPU发出的地址信号译码成与之对应的设备的CS(片选)信号。

以下是一些常见的组合逻辑电路及其应用:1. 2进制加法器2进制加法器是一种常见的电路,它用于将两个二进制数相加。

它的输入通常为两个二进制数和一个进位信号,输出为一个二进制数和一个进位信号,其中进位信号由前一位相加的进位和当前位的两个输入信号决定。

2进制加法器通常被用于CPU中的ALU(算术逻辑单元)中,实现加法操作。

2. 4位全加器4位全加器是一种电路,用于将四位二进制数相加。

它由四个2进制加法器组成,每个加法器的进位都与前一个加法器的进位相连。

4位全加器通常也被用于ALU中,实现更高精度的加法操作。

3. 反相器反相器是一种电路,将输入信号取反输出。

它通常由一个晶体管或MOS管构成,当输入信号为高电平时,电路关闭,输出为低电平;当输入信号为低电平时,电路开启,输出为高电平。

反相器在数字电路中有广泛应用,用于信号处理、计数器、寄存器等电路。

4. 与门与门是一种电路,当所有输入信号都为高电平时,输出为高电平;否则输出为低电平。

与门通常由两个PNP晶体管或两个NPN晶体管组成,输入信号通过两个晶体管的基极输入到集电极,当所有输入信号都为高电平时,晶体管都开启,输出信号为高电平。

5. 或门或门是一种电路,当任意一个输入信号为高电平时,输出为高电平;否则输出为低电平。

与门和或门是组合逻辑电路常用的基本逻辑门,它们可以通过多次组合实现更复杂的电路功能。

![知识点二 常用的组合逻辑电路_电工电子技术基本功_[共5页]](https://uimg.taocdn.com/520f7c71f524ccbff12184eb.webp)

182 电工电子技术基本功

②圈的数目越少越好;

③同一个“1”方格可以被多次圈,但每一个圈内至少应有一个方格未被其他圈圈

过,否则该项所表示的乘积项是多余的。

知识点二 常用的组合逻辑电路

按照电路的结构和工作原理,数字电路可分为组合逻辑电路和时序逻辑电路两大类。

在任何时刻电路的稳定输出只取决于同一时刻各输入变量的取值,而与电路以前的状态

无关,就称为组合逻辑电路,简称组合电路。

1.编码器

数字电路中只有“1”和“0”两种数码,也就是只有“高电平”和“低电平”两种

工作状态,需要将若干个“0”和“1”按一定规律排列在一起,代表不同的数码和不同

的含义,这样的过程就叫做“编码”。

图9-23所示是常见的10-4 线编码器,也是8421BCD

编码器,其真值表如表9-11所示。

图9-23 10-4 线编码器

表9-11 8421BCD编码器真值表

十进制数输入变量

输出变量

Y3Y2Y1Y0

0 A00 0 0 0

1 A10 0 0 1

2 A20 0 1 0

3 A30 0 1 1

4 A40 1 0 0

5 A50 1 0 1

6 A60 1 1 0

7 A70 1 1 1

8 A8 1 0 0 0

9 A9 1 0 0 1

逻辑表达式为

Y0=A1+A3+A5+A7+A9

Y1=A2+A3+A6+A7

Y2=A4+A5+A6+A7

Y3=A8+A9

2.译码器

译码是编码的逆过程,即将代码译为一定的输出信号,常用的是将二进制数转换为。

常见的组合逻辑电路组合逻辑电路指的是由多个逻辑门组成的电路,其输出只与输入信号的组合有关,而与输入信号的时间顺序无关。

在现代电子设备中,组合逻辑电路被广泛应用于数字电子系统的设计中。

下面将介绍几种常见的组合逻辑电路及其应用。

一、与门(AND Gate)与门是最基本的逻辑门之一,它只有当所有输入信号都为高电平时,输出才为高电平。

与门在数字电路中扮演着非常重要的角色,可以用于实现多个输入信号的复合判断。

在计算机的算术逻辑单元(ALU)中,与门经常用于进行逻辑运算。

二、或门(OR Gate)或门也是一种常见的逻辑门,它只要任意一个输入信号为高电平,输出就为高电平。

与门和或门可以相互组合使用,实现更复杂的逻辑运算。

或门常用于电子开关和电路选择器等应用中。

三、非门(NOT Gate)非门是最简单的逻辑门,它只有一个输入信号,输出信号是输入信号的反向。

非门常用于信号反转的场合,例如数字信号进行取反操作。

四、与非门(NAND Gate)与非门是由与门和非门组合而成的逻辑门,其输出是与门输出信号取反。

与非门的应用非常广泛,可以用于各种数字电路的设计中,例如计算机内存、固态硬盘等。

五、或非门(NOR Gate)或非门由或门和非门组合而成,其输出是或门输出信号取反。

与与非门类似,或非门也可以用于各种数字电路的设计中,例如译码器、比较器等。

六、异或门(XOR Gate)异或门是一种特殊的逻辑门,只有当输入信号中的奇数个为高电平时,输出为高电平;偶数个为高电平时,输出为低电平。

异或门在编码器、加法器以及数据传输方面有着重要的应用。

七、多路选择器(Multiplexer)多路选择器是一种可以根据选择信号选择不同输入信号的逻辑电路。

它可以将多个输入信号中的一个或多个输出至一个输出线上。

多路选择器可以在数字信号的选择和转换中起到关键作用。

八、译码器(Decoder)译码器是一种将多位输入信号转换为多位输出信号的逻辑电路。

它可以将某个特定的输入编码成高电平,从而实现对多个输入信号的解码和处理。

常用的组合逻辑电路

加法器:实现1位二进制数之间加法运算的电路称为1位加法器。

依据加数的不同,1位加法器又分为半加器和全加器两种电路类型。

假如不考虑来自低位的进位而是只将两个1位二进制数相加,即只有加数和被加数相加,这种加法运算称为半加运算。

实现半加运算的电路叫做半加器。

串行进位加法器的优点是电路比较简洁,缺点是速度比较慢。

编码器:在数字系统中,所谓编码,就是将字母、数字、符号等信息编成一组二进制代码的过程。

编码器是数字电路中常用的集成电路之一。

最常见的计算机键盘中就含有编码器器件,当按下键盘上的按键时,编码器将按键信息转换成二进制代码,并将这组二进制代码送到计算机进行处理。

目前常常使用的编码器有一般编码器和优先编码器两类。

译码器:译码是编码的反过程。

编码是将信号转换成二进制代码,译码则是将二进制代码转换成特定的信号。

将输入的二进制代码转换成特定的高(低)电平信号输出的规律电路称为译码器。

数据选择器:数据选择器的功能是依据地址选择码从多路输入数据中选择一路送到输出。

当输入信号经过不同的路径传输到同一个门电路时,由于信号所经过的门电路的传输延时不同,或者所经过的门电路的级数不同,导致信号到达汇合点门电路的时间不同,从而可能引起该门电路的输出波

形消失尖峰脉冲(干扰信号),这一现象称为组合规律电路中的竞争-冒险现象。

产生竞争-冒险的缘由是由于一个门的两个互补的输入信号分别经过两条不同的路径传输,由于延迟时间不同,而到达的时间不同引起的。

消退竞争-冒险的方法主要有引入封锁脉冲、引入选通脉冲、接滤波电容或修改规律设计等。