低功耗多偏置新型CMOS跨导放大器的设计与仿真

- 格式:doc

- 大小:330.50 KB

- 文档页数:5

低电压低功耗伪差分两级运算跨导放大器设计肖莹慧【摘要】为了满足电池供电设备低功耗、低电压的要求,提出一种用于超低电压和低功率混合信号应用的、基于米勒补偿的两级全差分伪运算跨导放大器(OTA).该放大器电路使用标准的0.18μm数字CMOS工艺设计,利用PMOS晶体管的衬体偏置减小阈值电压,输入和输出级设计为AB类模式以增大电压摆幅.将输入级用作伪反相器增强了输入跨导,并采用正反馈技术来增强输出跨导,从而增大直流增益.在0.5V电源电压以及5pF负载下对放大器进行模拟仿真.仿真结果表明,当单位增益频率为35 kHz时,OTA的直流增益为88dB,相位裕量为62°.与现有技术相比,所提出的OTA品质因数改善了单位增益频率和转换速率,此外,其功耗仅为0.08μW,低于其他文献所提到的OTA.【期刊名称】《沈阳工业大学学报》【年(卷),期】2018(040)004【总页数】5页(P431-435)【关键词】低电压低功耗;伪差分两级OTA;0.18μmCMOS技术;AB类模式;米勒补偿;正反馈技术;单位增益频率;转换速率【作者】肖莹慧【作者单位】中南财经政法大学武汉学院, 武汉430000【正文语种】中文【中图分类】TN432对于电池供电的应用产品(如生物医学植入式设备、无线传感器网络和微系统),如何降低功耗是极其重要的[1].为了满足低功耗低电压要求,人们通常使用工作在弱反型(或亚阈值)区域中的MOS晶体管[2].随着薄氧化物技术的发展,为了避免击穿并保持器件的可靠性,人们减少了电源电压,短沟道器件的阈值电压(Vth)也相对于电源电压按比例缩小.短沟道器件倾向于短沟道效应(SCE),这种效应降低了放大器的固有增益,使单级放大器难以获得高增益[3-4].MOS晶体管配置的共射共基放大器因有限的电源电压倾向于减小摆动而不能使用.与串联晶体管相比,具有公共栅极的堆叠复合(自共栅)晶体管[5]能够提供较小的输出电压和高电阻值,通过级联多个增益级可实现高增益,但需要额外的补偿电路,且每个增益级需要额外的功率补偿[6-7].米勒补偿[8-11]是两级运算跨导放大器(OTA)较为简单和流行的补偿技术,嵌套式米勒补偿将包含两级以上放大器,其在两个高阻抗节点之间放置一个补偿电容(CC).由于从输入级到输出节点的前馈路径将产生正(右手平面)零点,这会降低相位裕量并使OTA不稳定.为了改善OTA的稳定性,可以消除零点或将零点置于较高频率处.而为了将零点置于较高频率处,第二级放大器则需要较大的偏置电流,这增加了放大器的总功耗.有两种技术可使正零点无效,一种技术是将米勒电阻(RC)与CC串联;另一种技术则是通过在CC和输出节点之间放置电压(电流)缓冲器来断开正向通路[12-13].但用于低频OTAs和电压(电流)缓冲器中的大量芯片会增加额外的功耗.近年来,众多低压电路均利用了衬底驱动晶体管,例如差分放大器、电流镜、电压基准和缓冲器等[8-9].衬体驱动晶体管能够工作在低电压条件下,但其衬底跨导、本征增益较小,而输入电容较大.在文献[5]中已实现了基于自级联的OTA,但其品质因数较小;文献[1]中使用三阱CMOS技术实现了伪两级栅极驱动和衬体驱动OTA,但三阱技术的需求和额外的制造步骤导致了成本增加.这些OTAs使用电阻共模反馈电路不仅降低了输出电阻值,且增大了芯片的面积.本文提出一种低功耗、高增益的伪全差分二级OTA,OTA的输入和输出级处于AB类模式,意味着所有晶体管将驱动输入信号,从而提高压摆性能.OTA的输入级用作伪反相器,其增强了输入跨导(gmⅠ),采用正反馈技术来增强输出跨导(gmⅡ).本文所提出的OTA工作电压为0.5 V,负载电容为5 pF.1 米勒补偿伪两级运算跨导放大器1.1 主放大器单级共源共栅电路拓扑结构中不适合设计工作在低电压下的大摆幅高增益放大器,相反,通常采用多级拓扑结构来实现期望的增益和输出摆动,可通过MOS晶体管的级联以及多个增益的级联来降低输出电导或增加MOSFET的输入跨导,以增加增益值[10].不同增益增强技术均有其优缺点,级联对于低电压电路不可用,多级需要补偿且每级会产生额外功率,电导可通过增加MOSFET的沟道而减小,但其增大了寄生电容.本文所提出的伪运算跨导放大器基于低电源电压,并且通过改善每个级的跨导而不增加分支中的电流来增强增益.此外,本文的OTA设计采用AB类模式以提高电压摆幅与增益.图1为米勒补偿二级伪运算跨导放大器的电路图.图1中,UIN和UIP为反相和同相输入端,UON和UOP为运算跨导放大器的输出节点.放大器第一级由伪差分对M1A-M1B、交叉耦合晶体管M2A与M4B以及M2B与M4A组成,所有晶体管偏置在亚阈值区域.在交叉耦合模式下,电压缓冲电路M2A-M2B,M4A-M4B将输入反馈到M3A-M3B.交叉耦合配置充当电压缓冲器,且其输出反馈到M3A-M3B的栅极,由于耦合配置,输入跨导将得到改善.输入级PMOS晶体管的衬底偏置电压低于衬底电压,以减小阈值电压.输入级的公共输出节点电压等于连接PMOS M4A-M4B晶体管的栅极电压,由于该种配置消除了共模反馈电路(CMFB),为了避免额外的制造步骤,OTA中NMOS晶体管的所有衬底连接到地.第二级放大器的交叉耦合(M6A-M6B,M8A-M8B)配置与第一级放大器的交叉耦合配置类似.M8A-M8B衬底连接为正反馈模式,作为共源放大器.总输出级跨导等于输出级PMOS M7A-M7B晶体管的跨导乘以交叉耦合共源结构的增益AVCF,这有助于增强增益,并可保持右半复平面(RHP)零点处于较高频率,以提高相位裕量.交叉耦合共源结构的增益为(1)式中,gmK、gmbK和gdsK为第K个晶体管的栅极跨导、衬底跨导及漏极电导.图1所示电路中,晶体管MKA的所有参数等于晶体管MKB.图1 米勒补偿的二级伪运算跨导放大器电路图Fig.1 Circuit diagram of two-stage pseudo-OTA with Miller compensation差分模式下伪运算跨导放大器的总增益为(2)(3)gmⅡ=gm5+(gm7+gmb7)·(4)1.2 共模放大器对于全差分放大器,其需要共模反馈将输出节点稳定到所需的值,一般等于中间电源电压.这里二极管连接MOS放置在输入和输出级,设置共模电压等于中间电容值.二极管连接的MOS栅极电压等于共模电压,施加的差分信号的输入和输出跨导是单独的MOS跨导的总和.输入有效跨导gmⅠC和输出有效跨导gmⅡC及共模增益AVCM表示为(5)gmⅡC=gm5-(gm7+gmb7)·(6)(7)1.3 频率补偿米勒补偿是一种用来补偿两级放大器的技术,使用该技术可以在分裂极点的两个高阻抗节点之间插入补偿电容.由于从输入级到节点的前馈将产生正零点,这降低了相位裕量.本文所提出的运算跨导放大器使用米勒补偿技术来使放大器稳定,这里通过使零点保持在较高频率实现期望的相位裕量.第二级放大器需要较大的跨导,其由正反馈交叉耦合配置得到增强.米勒补偿运算跨导放大器的极点和零点分别为(8)Pnd(9)(10)式中:R1、R2为输入和输出级的输出电阻;Pd、Pnd为主极点和非主极点;PZ 为RHP零点.图1中经过米勒补偿的OTA单位增益频率为(11)2 模拟结果2.1 基本特性本文所提出的OTA基于Cadence Virtuoso环境设计,使用UMC 0.18 μm数字CMOS技术进行模拟.为了观察OTA的开环增益和相位性能,设置负载电容(CL)为5 pF来对放大器电路进行模拟.放大器的频率特性模拟结果如图2所示,可以看出,OTA增益为88 dB,单位增益频率为35 kHz,相位裕量为62°.图3显示了共模和电源抑制响应特性.由图3可以得出,放大器的共模抑制比(CMRR)约为94.5 dB,因为在第二级配置中的正反馈用作共模信号的负反馈,这导致在输出节点处共模增益较小,所提出的OTA对共模和电源信号不敏感.伪差分OTA的输入参考噪声特性如图4所示,OTA的噪声特性主要取决于输入级跨导,其输入级跨导是常规差分配置放大器的两倍,噪声抑制效果较好.图5显示了负载电容(CL)为5 pF,电源电压为0.5 V时,本文所提出的伪OTA大信号脉冲响应.当误差为0.1%和0.01%时,建立时间分别为40 μs和160 μs.图2 频率特性模拟结果Fig.2 Simulation results of frequency characteristics图3 共模和电源抑制响应模拟结果Fig.3 Simulation results of common mode and power supply rejection response图4 输入噪声响应特性模拟结果Fig.4 Simulation results of input noise response characteristics图6为本文所提出的OTA在单位反馈增益模式下的共模范围特性.当输入电压为0.1~0.4 V时,其具有线性范围,完全可以满足低频应用.图5 单位增益模式下大信号脉冲响应模拟结果Fig.5 Simulation resultsof large signal impulse response under unity gain mode图6 单位增益模式下输入共模范围模拟结果Fig.6 Simulation results of input common-mode range under unity gain mode2.2 性能比较表1对几种OTA的主要参数进行了对比,FOM1表示单位增益品质因数,FOM2表示转换速率品质因数.由表1可知,本文所提出的放大器在增益、噪声、单位增益频率(UGF)和电源抑制比(PSRR)方面均显示出更优的性能,品质因数(FOM)也高于其他OTA.其中,电源电压为0.5 V,FOM1和FOM2分别为109、231,均为其他OTA的两倍以上.另外,直流增益高达88 dB,而功耗仅为0.08 μW,远远低于其他OTA功耗.3 结论本文提出了一种低电压低功耗CMOS伪差分两级运算跨导放大器(OTA),该放大器基于AB类拓扑结构,其中输入馈送到输入晶体管.为了避免低增益问题,在第二级放大器中采用正反馈技术提高了OTA的增益和稳定性,同时获得较小的电流及较大的跨导.与之前文献所提出的OTA相比,本文提出的OTA显示出更好的品质因数(FOM1和FOM2).同时,文中使用5 pF负载电容和0.5 V电源电压对OTA进行模拟,模拟结果显示,本文提出的OTA在35 kHz的单位增益频率下直流增益高达88 dB,相位裕量为62°.此外,输入参考噪声特性模拟结果显示,该OTA在低频下具有更好的闪烁噪声性能,且在1 kHz下的输入参考噪声有益于在生物医学中应用.该OTA在0.5 V电源电压下功耗为0.08 μW,远小于文献中其他OTA的功耗.表1 伪OTA与其他文献中的OTA模拟仿真结果对比Tab.1 Comparison in simulation results of pseudo-OTA and OTA in other literatures方法电源电压VCMOS技术直流开环增益dBUGFMHz相位裕量(°)压摆率(+/-)(V·μs-1)输入噪声(μV·Hz-1/2)CMRRdB本文0.50.18μm(双阱)88.0 0.035620.074/-0.0870.150(@1kHz)94.5(@1Hz)文献[9]0.550nm74.04.800493.4000.059(@1MHz)106.0(@5kHz)文献[5]1.0SOI45nm55.9656.00061500.000-63.0(@10kHz)文献[11]0.80.18μm(双阱)51.00.04065 0.1200.057(@1MHz)65.0(@1Hz)方法PSRR+dBPSRR-dB稳定时间μs负载电容pF总电流μA功耗μWFOM1FOM2本文84.5(@1Hz)110.5(@1Hz)160(0.01%)5.0 0.16 0.08109.0231.0文献[9]81.0(@5kHz)-0.53(0.1%)20.0200.00100.0048.034.0文献[5]60.0-0.07(1.0%)0.3620.00620.0031.724.2文献[11]---10.01.251.0032.096.0参考文献(References):【相关文献】[1] Ragheb A N,Kim H W.Ultra-low power OTA based on bias recycling and subthreshold operation with phase margin enhancement [J].Microelectronics Journal,2017,47(3):94-101.[2] Wang H J,Wang C H,He H Z,et al.A low-power voltage reference source based on sub threshold MOSFETs [J].Microelectronics Journal,2011,41(5):654-657.[3] Shim J,Yang T,Jeong J.Design of low power CMOS ultra wide band low noise amplifier using noise canceling technique [J].Microelectronics Journal,2013,43(9):821-826.[4] Akbari M,Hashemipour O.Enhancing transconductance of ultra-low-power two-stage folded cascode OTA [J].Electronics Letters,2014,50(21):1514-1516.[5] 徐少波.一种基于信号处理的光纤液体温度传感器 [J].沈阳工业大学学报,2005,27(1):77-79. (XU Shao-bo.An optical fiber liquid temperature sensor based on signal processing [J].Journal of Shenyang University of Technology,2005,27(1):77-79.)[6] Gomez H,Espinosa G.55 dB DC gain,robust to PVT single-stage fully differential amplifier on 45 nm SOI-CMOS technology [J].Electronics Letters,2014,50(10):737-739.[7] Garimella A,Furth P M.Frequency compensation techniques for op-amps and LDOs:a tutorial overview [J].Midwest Symposium on Circuits & Systems,2011(7):1-4.[8] 薛超耀,韩志超,欧健,等.一种恒跨导轨对轨CMOS运算放大器的设计[J].电子科技,2013,26(9):121-123.(XUE Chao-yao,HAN Zhi-chao,OU Jian,et al.A design of electronic technology,constant cross rail to rail CMOS operational amplifier [J].Electronic Science and Technology,2013,26(9):121-123.)[9] Wu D,Gao C,Liu H,et al.A low power double-sampling extended counting ADCwith class-AB OTA for sensor arrays [J].IEEE Transactions on Circuits & Systems I:Regular Papers,2015,62(1):29-38.[10]吴贵能,周玮.一种两级CMOS运算放大器电源抑制比提高技术 [J].重庆邮电大学学报(自然科学版),2010,22(2):209-213.(WU Gui-neng,ZHOU Wei.PSRR improvement technique for two-stage CMOS operational amplifier [J].Journal of Chongqing University of Posts and Telecommunications(Natural Science Edition),2010,22(2):209-213.)[11]田锦明,王松林,来新泉,等.一种新颖的OTA结构的数模转换器 [J].电子科技,2006(3):13-16.(TIAN Jin-ming,WANG Song-lin,LAI Xin-quan,et al.A novel digital to analog converter with OTA structure [J].Electronic Science and Technology,2006(3):13-16.)[12]Mirvakili A,Koomson V J.Passive frequency compensation for high gain-bandwidth and high slew-rate two-stage OTA [J].Electronics Letters,2014,50(9):657-659.[13]Valero M,Celma S,Medrano N,et al.An ultra low-power low-voltage class AB CMOS fully differential opamp [J].IEEE International Symposium on Circuits & Systems,2012,57(1):1967-1970.。

新型高增益CMOS跨导运算放大器凡东东;宋树祥;蒋品群;岑明灿【摘要】为了解决在低电压、深亚微米工艺条件下获得高增益运算放大器的问题,通过引入电流倍增和分流技术,提出了一种新型高增益可调的跨导运算放大器(OTA).在1.8 V工作电源下采用0.18 μm COMS标准工艺对其进行Spectre模拟,结果表明,该OTA的直流开环增益在61 dB至91 dB可调,最大静态功耗为434μW,最小共模抑制比为114 dB.所提出的跨导运放与传统OTA相比,具有高增益和增益可调的优点,可适用于通信、电子测量,以及自动控制等系统.【期刊名称】《广西师范大学学报(自然科学版)》【年(卷),期】2014(032)004【总页数】5页(P6-10)【关键词】CMOS;跨导运放;电流处理;高增益【作者】凡东东;宋树祥;蒋品群;岑明灿【作者单位】广西师范大学电子工程学院,广西桂林541004;广西师范大学电子工程学院,广西桂林541004;广西师范大学电子工程学院,广西桂林541004;广西师范大学电子工程学院,广西桂林541004【正文语种】中文【中图分类】TN721跨导运算放大器在电源、模数转换器、滤波器等模拟电路中已经得到广泛的应用[1-11]。

随着电源电压的下降和工艺尺寸的进一步缩小,晶体管沟道长度不断减小,致使晶体管本征增益也不断减小,在这种条件下设计高增益运放面临较大挑战[1]。

在低功耗设计中,一般采用工作在弱反型区或采用衬底驱动晶体管,这样既可以降低输入电压,又可以获得较高的输入跨导增益,但这种电路MOS管漏极电流较小,增益带宽积也小,限制了运算放大器的动态性能[2-5]。

Y.L.Li等[6-7]在SMIC 0.13μm CMOS工艺下提出一种改进的循环结构运算跨导放大器,跨导增益获得了230%的改善、增益带宽积提升13 d B。

不过该电路输入电压摆幅受限、循环结构使用过多,导致电路复杂、增益固定等问题,限制了其作为基本OTA单元的应用。

设计应用技术Telecom Power Technology g tanknk p11.92R ≈ (5)起振的判决条件公式为 mn mptank 2g g g γ+≥ (6)式中:g mn 为NMOS 的跨导值;g mp 为PMOS 的跨导值;γ为保证起振正常的起振因子,通常取3。

因此,在设计中NMOS 和PMOS 管的跨导都取g mn =g mp = 5.76 mS 。

3 测试分析与讨论文章基于SMIC 40 nm 对LC-VCO 进行设计,通过版图绘制以及后仿真的优化测试可知。

本文设计的VCO 版图如图3所示,大小约为0.089 mm 2,整体功耗为1.155 mW 。

图3 VCO 版图控制电压U ctrl 在200~900 mV 时,中心频率下的调谐曲线如图4所示。

由图4可知,传统的可变电容电路所得到的调谐增益K vco 变化较大,对于控制电压的利用率不高,而优化后的调谐曲线较为线性,避免了VCO 调谐线性度较差后产生的锁相环不稳定现象,使其在整个频带中波动较小,与设计的目标相一致。

TT 工艺角(表示NMOS 和PMOS 都是Typical 型)下,25 ℃时,后仿真的64条调谐曲线如图5所示。

相邻2条曲线有一定的交叠,避免了输出的频谱出现断点,同时让工作频率覆盖在4.08~5.62 GHz ,保证了中心频率在4.85 GHz 附近,使整个频率的调谐范围占比为31.75%。

控制电压/mV优化后的调谐曲线初始的调谐曲线200.04.714.724.734.744.754.764.774.78频率/G H z4.794.804.81250.0300.0350.0400.0450.0500.0550.0600.0650.0700.0750.0800.0850.0900.0图4 调谐曲线的比较控制电压/mV5.62 GHz4.08 GHz频率/G H z200.04.04.14.24.34.44.54.64.74.84.95.05.15.25.35.45.55.65.7300.0400.0500.0600.0700.0800.0900.0图5 64条频率调谐曲线VCO 的相位噪声PVT 测试结果如图6所示,在1 MHz 频率偏移处,在TT 工艺角下,25℃常温时,该相位噪声为-116.46 dBc/Hz ,较前仿所测得的相位噪声有所下降,主要原因是后仿带来的寄生电容的不确定性。

摘 要随着集成电路技术的发展,电流模式电路的研究设计已经成为国内外微电子、集成电路设计领域的热门前沿课题。

全差分式跨导运算放大器是电流模式电路的一种通用标准集成电路,是模拟系统和数字混合系统的基础。

跨导运放的基础应用有电压比较器和连续时间跨导-电容滤波器等。

本文主要研究设计一种新型全差分轨对轨输入的跨导器,其输入/输出动态范围线性可调节,并应用全差分轨对轨跨导器电路构造电压模式和电流模式的多功能双二阶滤波器。

具体研究内容如下:1、设计了一种新型全差分轨对轨结构且线性范围可调节的CMOS 跨导器电路,全差分电路由主放大器和共模反馈环路电路两部分组成,主放大器是由P型电路和Nμ工型电路的栅极并联组成。

电路是单级结构。

应用Cadence 软件,SMIC0.18m 艺,电源电压为1.8V,仿真结果表明:通过连续调节源级负反馈电阻值(0~30KΩ),单级跨导增益最高值为-69.7dB;输出电流的-3 dB截止带宽最高为396Mhz;输入电压线性范围扩展到±0.7V, 输出电流,与不包含源级负反馈电阻相比,范围增大了约5倍;CMRR为-124dB;PSRR为-62dB;功耗为1.5mW。

2、基于所设计的CMOS全差分轨对轨跨导器电路,分别应用组成电压比较器、电压模式和电流模式的多功能双二阶滤波器、模拟各种功能运算。

功能运算模拟包括全差分式电压模式和全差分式电流模式的加法器和积分器。

所设计的双二阶滤波器可以根据不同的输入端参数,实现低通、高通、带通、带阻四种滤波功能。

并且采用所设计双二阶滤波器并联实现四阶电压模式和电流模式滤波器,使用仿真软件Cadence,验证设计的正确性。

3、设计并绘制了不包含无源电阻的CMOS 全差分轨对轨跨导器的电路版图,其版图通过DRC、LVS、RCX验证,进行后仿真PS。

仿真结果表明:跨导增益、截止带宽均有下降,但基本与前仿真一致。

关键字:轨对轨;CMOS 全差分跨导器;跨导-电容双二阶滤波器;电压比较器AbstractWith the high speed development of integrated circuit, the study and design of current-mode circuit has becoming a popular advanced topic in microelectronics or integrated circuit fields of domestic and overseas. Fully differential operational transconductor amplifier (FD OTA) is a general integrated circuit standard of the current-mode circuit , and it is a basis between analog system and digital mixed system.The applications contain Voltage comparator and continuous time transconductance-capacitance filter.This paper mainly studies a new type transconductor with input of fully differential and rail-to-rail, its input/output dynamic range is linear adjustable, and using the transconductor circuit structure multifunctional Biquad filter of voltage mode and current mode. The main work is summarized as follows:Firstly, a new CMOS fully differential OTA circuit with rail-to-rail input and linear adjustable is designed, The fully differential circuit contains main amplifier and common mode feedback (CMFB)circuit . The main amplifier is both P-type、N-type paralleling gate pole.Circuit is only primary structure. Under the condition of SMIC 0.18 µm process and power voltage of 1.8 V, With Cadence application software, the simulation results show that: single grade transconductance gain is -69.7 dB, output current -3 dB by up to 396 Mhz bandwidth, input linear range expand to ±0.7 V, output current range expand about 5 times without source negative feedback resistance.CMRR for -124 dB, PSRR for -62 dB, and power consumption for 1.5 mW through continuous adjusting source resistance (0 to 30 KΩ ).Secondly, based on the design of the CMOS fully differential OTA circuit, a voltage comparator and voltage mode / current mode fully differential multifunctional Biquad filters are designed ,and all sorts of function operation analog respectively. Analog include adder and integrator with voltage mode fully differential and current mode fully differential. According to the input parameters, the Biquad filter can realize low-pass, high-pass, band-pass, band resistance four functions. The voltage mode and current mode four order filters are designed by the Biquad filter, and the validity of the design is verified with Cadencesoft.Thirdly, a CMOS fully differential OTA circuit layout is designed and mapped without source negative feedback resistance. And the layout is through the DRC, LVS, RCX verification, post simulation (PS). The simulation results show that: the overall performance of PS is consistent with the former simulation except for a slight decrease of transconductance gain, the -3dB bandwidth and linear range.Key words: rail-to-rail; CMOS fully differential OTA; transconductance-capacitance Biquad filter; voltage comparator目 录摘 要I Abstract II 第一章 绪论1§1.1引言 (1)§1.1.1模拟集成跨导放大器概述 (1)§1.1.2 研究目的和意义 (1)§1.2国内外研究现状 (2)§1.3本论文内容安排 (3)第二章 全差分跨导运算放大器基本原理及其非线性分析4§2.1 全差分跨导运算放大器理论 (4)§2.1.1全差分跨导运算放大器符号表示 (4)§2.1.2全差分跨导运算放大器结构框图 (5)§2.2 全差分电路的线性化技术 (7)§2.3全差分结构和伪差分结构比较 (9)§2.4 本章小结 (10)第三章 新型线性可调节FD OTA设计关键技术与仿真实现11§3.1 FD OTA电路总体结构设计 (11)§3.1.1轨对轨交叉耦合差动式CMOS输入级 (11)§3.1.2电路中使用的电流镜 (13)§3.2 电路中使用的共模反馈电路 (17)§3.3电路中使用的电压偏置电路 (18)§3.4主跨导器电路的设计和分析 (18)§3.5 CMOS FD OTA电路仿真验证 (22)§3.6 本章小结 (27)第四章 全集成 CMOS FD OTA的应用28§4.1电压比较器 (28)§4.1.1电压比较器的简单介绍 (28)§4.1.2 CMOS FD OTA模块构成的电压比较器 (28)§4.2全差分连续时间CMOS双二阶滤波器 (29)§4.2.1双二阶滤波器 (29)§4.2.2跨导-电容连续时间滤波器的设计方法 (30)§4.3跨导-电容模块的功能模拟 (31)§4.3.1全差分积分器简单介绍 (31)§4.3.2全差分跨导器模拟电阻 (32)§4.3.3全差分电压模式和电流模式的加法器 (32)§4.3.4全差分电压模式和电流模式的积分器 (33)§4.4双二阶CMOS FD OTA-C连续时间滤波器的设计 (35)§4.4.1电压模式双二阶CMOS FD OTA-C滤波器的设计和分析 (35)§4.4.2电压模式双二阶CMOS FD OTA-C滤波器的仿真验证 (36)§4.4.3电流模式双二阶CMOS FD OTA-C滤波器的设计和分析 (37)§4.4.4电流模式双二阶CMOS FD OTA-C滤波器的仿真验证 (38)§4.5四阶CMOS FD OTA-C连续时间滤波器的设计 (39)§4.5.1 电压模式四阶CMOS FD OTA-C滤波器的设计电路和仿真 (39)§4.5.2 电流模式四阶CMOS FD OTA-C滤波器的设计电路和仿真 (40)§4.6本章小结 (41)第五章 基准源的设计和仿真42§5.1基准源的分类和特点 (42)§5.1.1带隙电压基准 (42)§5.1.2带隙电流基准 (44)§5.2电路中使用的基准电流源设计和仿真 (46)§5.2.1 带隙基准电流电路的工作原理 (46)§5.2.2电路分析 (47)§5.2.3电路仿真 (47)§5.3本章小结 (49)第六章 电路版图设计、验证和后仿真50§6.1模拟电路版图设计步骤 (50)§6.2版图设计中的注意事项 (50)§6.3电路版图设计和后仿真实现全过程 (51)§6.4本章小结 (53)第七章 总结与展望55§7.1 总结 (55)§7.2 展望 (55)参考文献57致 谢60作者在攻读硕士期间主要研究成果61第一章绪论第一章 绪论§1.1引言电流模式设计方法是近几十年的重大发现和未来模拟集成电路发展的新阶段。

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

3.1.13低功耗多偏置的新型跨导放大器的设计与仿真姓名1(1东北微电子研究所,辽宁沈阳 110036)摘要:本文主要对一种新型低功耗多偏置的新型跨导放大器进行了设计和仿真,根据管子宽长比的计算完成了电路结构的搭建。

在此基础上,运用Hspice模拟电路的仿真工具提出了网表,并完成了系统仿真设计。

在7.75V电源电压下,采用CSMC 0.5um工艺模型,可以驱动75pF的负载,相位裕度为65度,单位增益带宽为1.19MHz,静态功耗为3.43mW,实现了低功耗运算跨导放大器的良好性能。

关键词:带隙基准源,相位裕度,增益带宽,跨导放大器。

Abstract: In this article, a design method of low power new Gm_OTA is designed and made simulation , and the construction of circuit is finished on the basis of width and length . Basis on that, retiary is also established by Hspice Tool. At the same time, the simulation of the system model are accomplished. Under 7.75v, on the basis of CSMC 0.5um technics model, 75pF load is drived by the design, the phasic margin is 65 degree,the unit plus bandwidth is 1.19MHz,the static power is 3.43mW,and good capability of low power Gm_OTA is carried out.Key words: bandgap, phasic margin ,plus bandwidth, Gm_OTA.1引言:集成运算放大器是模拟集成电路中应用比较广泛的一种器件,随着半导体技术的发展和人类资源的有限,对各种用电器的节能效应越来越高,所以我们即便面对高电压,也要研究设计一种新型的低功耗运算放大器。

本文设计了一种应用于升压式直流调节系统中的核心电路—含有带隙基准源的低功耗跨导放大器(Gm _OTA)。

低功耗运算放大器的特点就是通过在IC外部连接上电阻或恒流源就能适当地调整电源电流,同时也就得到各种不同的参数,从而使它在负3V到正15V间都可以正常的稳定工作。

本文主要针对一种低功耗的新型运算跨导放大器进行了研究与设计仿真。

文章首先对新型电路的各个结构进行了搭建,然后对整体的电路进行了模拟仿真,最后完成了整体电路的版图设计。

2电路设计与性能分析本设计的新型多偏置低功耗跨导放大器应用于升压式开关电源之中,需要7.75V 的较高输入电压,面对如此高的电源电压,其低功耗的性能尤为重要。

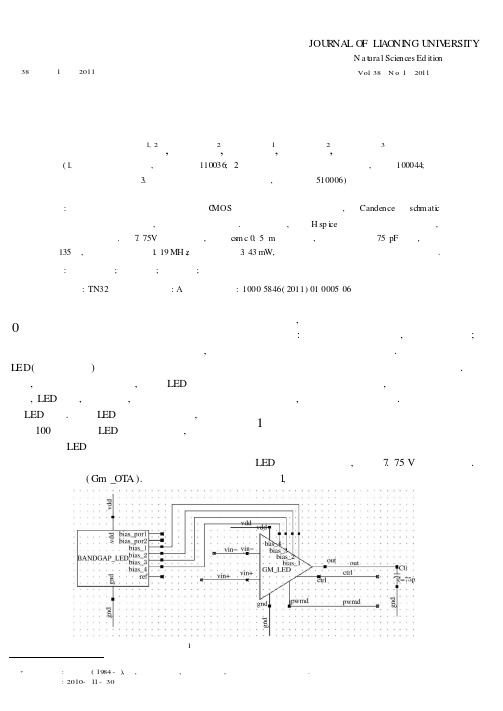

如图1所示,它主要由带隙基准源模块和一个跨导运算放大器模块共同构成,带隙基准模块为跨导放大器模块提供四路偏置电流。

图1跨导放大器的电路结构图2.1 跨导放大器的优点跨导放大器与普通的电压放大器相比较有着许多自身的优点。

第一,输入阻抗低,输出阻抗高。

第二,电源电压承受力强,功耗较低。

第四,具有较高的带宽,增益可控制。

第五,电路的结构新颖简单,便于设计。

因此,跨导放大器具有现实研究意义和使用价值,所以本文对其结构进行优化设计,旨在设计一种低功耗的跨导放大器。

2.2 跨导放大器的基本模型由图2可知,电压信号流进差动对后,转换成电流信号,达到了跨导放大的作用;双端输出的电流I1、I2经过电流镜M1~M3变换成单端输出电流I0;偏置电流I4驱动电流镜M4,经电流镜M4传送到跨导输入级作为尾部电流源,调节本跨导放大器的增益的大小。

CMOS工艺下的跨导放大器的电路结构的核心部分是差动式跨导输入级,而且传输特性的非线性误差也主要来源于差动式跨导输入级。

所以合理地改善跨导输入级的线性范围和线性程度可以极大地提升跨导放大器的性能,本设计就在此处对其结构进行了新颖的改进。

图2跨导放大器的结构框图2.3跨导放大器核心电路放大器一般分为套筒式和折叠式结构,本设计的跨导放大器采用高摆幅的折叠式共源共栅结构,它的内部带有控制的偏置电路,而且外部的带隙基准源为它提供了偏置电流,所以它是一种多偏置的跨导放大器。

图3跨导放大器核心电路在图3中,左半部分差分放大器的偏置bias_opa_1 和bias_opa_2由最右侧给出,而右侧的偏置bias_1~bias_2由带隙基准源提供,偏置电路和折叠式共源共栅放大器的中间部分是该跨导放大器的使能部分。

当PWMD为高电平时,它使管M2开启,漏极电压为“0”,经过四个反相器后,使N管M4、M6栅极电压为“0”而关断,内部电路实现偏置功能。

当PWMD为低电平时,它使管M2关断,漏极电压为VDD,经过四个反相器后,使N管M4、M6栅极电压为VDD而开启,使bias_opa_1和bias_opa_2处电压为0V,从而使偏置电路失去功能达到使能目的。

现在我们近似确定本设计中折叠式共源共栅结构跨导放大器的小信号电压增益。

现将折叠式共源共栅部分放大如图4分析。

图4 折叠式共源共栅结构通过该电路的半边电路,可写出outmVRGA=,我们必须计算出outR和mG,才能得到最终增益。

经过分析,输出短路电流约等于1M的漏电流,因为从M3的源端往里看,所看到的阻抗,即3133//)(Om bmrgg-+,通常远低于51//OOrr。

因此,1mmgG≈。

要计算outR,可以直接得到:)]//()//[(51333OOOmbmOPoutrrrggRR+≈(1.1) 由此得出:]})//[()]//(){[(9777513331OOmbmOOOmbmmvrrggrrrgggA++≈(1.2)以上得出的公式结论也符合该电路的交流小信号模型,对电路进行交流小信号模型如下图5所示:图5 交流小信号模型由此也可以得到相同的增益大小。

3、仿真数据与波形本设计的仿真采用csmc 0.5um工艺模型,采用Hspice仿真工具,工作电压源为7.75v,它的工艺角与工作温度分别如下:TT_25: mostt_bjttt_25度;TT_-40: mostt_bjttt_-40度;TT_85: mostt_bjttt_85度;FF_25: mostt_bjttt_25度;FF_-40: mostt_bjttt_-40度;FF_85: mostt_bjttt_85度;SS_25: mostt_bjttt_25度;SS_-40: mostt_bjttt_-40度;SS_85: mostt_bjttt_85度;为了能够更好的观察仿真结果,跨导放大器只给出TT_25度的波形。

表1 跨导放大器的性能指标3.1、跨导放大器的参数仿真:下面具体地列出,本设计的跨导放大器实际的各项模拟仿真参数结果,并与文档的性能指标作比较。

3.1.1开环增益和相位裕度如波特图6所示,跨导放大器的共模开环增益为78.11db,满足66db的设计要求。

在直流的基础上叠加1V的交流信号进行AC交流仿真,以确定增益和相位裕度,为了避免放大器的输出被箝位在某一个电源电压或震荡,需满足条件:1)()()(000<=ωωωjLjFjA(1.3) 稳定的条件是曲线通过0db点应先于到达0度点。

当等于1(即0db)时的相位值给出了稳定性的度量。

这种度量称为相位裕度,由以下关系式描述:065115180)]([)]()([=-==-=Φ=wodBodBodBMjLArgjFjAArgωω相位裕量(1.4)图6开环增益和相位裕度的波特图3.1.2增益带宽积为了更好地观察跨导放大器的增益带宽,我们在其输出端加了一个80pF的电容,从图7中可以看出跨导放大器的0db增益处频率为1.21MHz ,由此计算出增益带宽积为1.21MHz。

图7增益带宽仿真波形3.1.3输入共模范围ICMR如图9为输入级能正常工作的情况下允许输入的共模信号范围,当共模输入电压超出此范围,跨导放大器便不能对差模信号进行放大。

如图8,跨导运算放大器链接成跟随器,接成负反馈的形式,用来检测输入共模信号范围,可以减小误差。

图8输入共模负反馈电路结构随着输入电压从-0.3变为7.75,输出变化范围从0.4V-6.01V ,如图9,在该测试电路下共模输入范围为0.6-5.36V 。

图9输入共模范围ICMR 仿真波形3.1.4输出电压摆幅跨导运放输入正端接一偏置为2V ,振幅为2V 频率为10K 的正弦信号,输入负端接1v 的直流电压,测试结果如图,运放输出范围8 mv-7.72v 。

图10输出电压摆幅仿真波形3.1.5共模抑制比CMRR共模抑制比等于差模放大倍数与共模放大倍数之比的绝对值,常用分贝表示,其数值为CMR g K l 20。

在运放的开环状态下,将同相和反相输入端同时加入一个幅度为0.5V 的交流小信号源,对输入进行AC 仿真,仿真的结果是共模增益。

它再与差模增益相除,便可以得到最终想要的结果—共模抑制比。

图11输入共模电路结构如图12所示,此跨导放大器的差模开环增益为67.45db ,跨导放大器的共模开环增益为76.03db ,其共模抑制比由式计算得: 88.0|03.76/45.67||/|===oc od CMR A A K (1.9)图12差模开环增益仿真波形3.1.6、电源电压抑制比仿真:电源抑制比随着所加交流信号频率的增加会降低,在低频状态下交流信号的电源抑制比为,具体变化情况如下: 在运放开环的状态下,将运放的反相输入端和输出端相连,电源叠加0.5V 的交流小信号,对同相输入端进行AC 仿真。

如下图13所示:图13电源电压抑制比电路图图14电源电压的抑制比从图14中可以看出,电源电压在3V~10V 变化时,在低频处带宽的范围,增益为一个稳定值。

电源的抑制特性可用PSRR 来衡量,PSRR 的值为70.78dB 。

3.1.7功耗 如图15,通过测量跨导放大器工作在直流情况下,VDD=7.75V 处的稳定电流值为442uA ,可以计算出它的动态功耗为: mW VDD I P VDD OTA 43.375.7442.0=⨯== (2.0)小于4mW ,因此满足了低功耗的设计要求。

图15 VDD 处的电流值仿真波形4、跨导放大器的版图设计模拟电路的版图设计是一门艺术,它决定了电路系统的总体性能,因此极其重要。

对一个电路进行版图设计,无非三个步骤,首先对器件进行布局,其次合理地布线,最后进行验证检查。